描述

內核重置應該保持斷言狀態(tài),直到相關時鐘穩(wěn)定為止。在從重置中取出以太網(wǎng) IP 核之前,它必須具有穩(wěn)定的頻率而且沒有故障。這適用于 SerDes 時鐘和 IP 核時鐘。 如果在一個時鐘中檢測到后續(xù)不穩(wěn)定性,就必須重置 100G 以太網(wǎng) IP 核。

這種不穩(wěn)定性的一個實例是 CDR 鎖丟失。

用戶邏輯應該確定所有需要重置的外部條件(例如:時鐘故障、CDR 鎖丟失或電源故障)。

解決方案

QPLL 和 TX 數(shù)據(jù)通道QPLL 和 TX 數(shù)據(jù)通道需要在 GT 參考時鐘輸入之后重置,而且為 GT 初始化狀態(tài)計時的 dclk/init_clk 會變得有效。

這可通過 Vivado 內核的 sys_reset 輸入完成,也可通過異步下降的 GT 封裝程序的 gtwiz_reset_all 輸入完成。

如果 GT 參考時鐘和 dclk/init_clk 在配置時有效,則內核中包含的 GT 初始化狀態(tài)機將自動觸發(fā)該重置。

TX 數(shù)據(jù)通道:

在串行數(shù)據(jù)生效后,GT 需要一個 GTRXRESET,以確保正確的 CDR 鎖定數(shù)據(jù)。

電纜拔出并重新插入后或為鏈路合作伙伴上電或對其進行重置后,都需要該操作。

在內核層面上,為了避免在鏈路的 TX 端發(fā)生中斷,可以使用 gtwiz_reset_rx_datapath 觸發(fā)重置。

如果可行的話,光學設備的信號檢測或信號損失反轉可用來觸發(fā)該重置。

如果信號檢測或信號丟失不可用,可添加超時邏輯監(jiān)控對齊/鏈路狀態(tài)是否尚未完成,并發(fā)布 gtwiz_reset_rx_datapath 重置。

如果啟用自動協(xié)商,則自動協(xié)商狀態(tài)機提供一個內建的 500ms 超時來重新啟動 AN 和重置狀態(tài)機。

該輪詢及復位程序將在標準上電時鐘穩(wěn)定重置序列后使用:

1) 等待 500ms

2) 輪詢 stat_rx_aligned 狀態(tài)

- 如果 stat_rx_aligned 無效,則斷言 GT rx_datapathonly_reset,然后轉到步驟 (1)

- 如果 stat_rx_aligned 有效,則斷言 GT rx_datapathonly_reset,然后轉到步驟 (3)

3) 等待 500ms

4) 輪詢 stat_rx_aligned 狀態(tài)

- 如果 stat_rx_aligned 無效,然后轉到步驟 (2)

- 如果 stat_rx_aligned 有效,請在步驟 (4) 中等待

在某些拓撲上,如在 PAM4 PHY 或其它 PHY 情況下,可以看到 RX 串行數(shù)據(jù)需要很長時間才能完全穩(wěn)定,而且可能會導致 GT RX 緩沖器錯誤。

如果 CDR 鎖性能良好,完成對齊可能仍會出現(xiàn) GT RX 緩沖器錯誤,因此可能需要對 GT RX 緩沖器狀態(tài)進行更進一步的監(jiān)控,才能觸發(fā)重置。

-

以太網(wǎng)

+關注

關注

40文章

5543瀏覽量

174089 -

緩沖器

+關注

關注

6文章

2023瀏覽量

46281 -

cdr

+關注

關注

1文章

51瀏覽量

18285 -

UltraScale

+關注

關注

0文章

119瀏覽量

31721

發(fā)布評論請先 登錄

相關推薦

賽靈思推出全球最大容量的FPGA – Virtex UltraScale+ VU19P

如何調試Zynq UltraScale+ MPSoC VCU DDR控制器

Zynq UltraScale+ MPSoC的發(fā)售消息

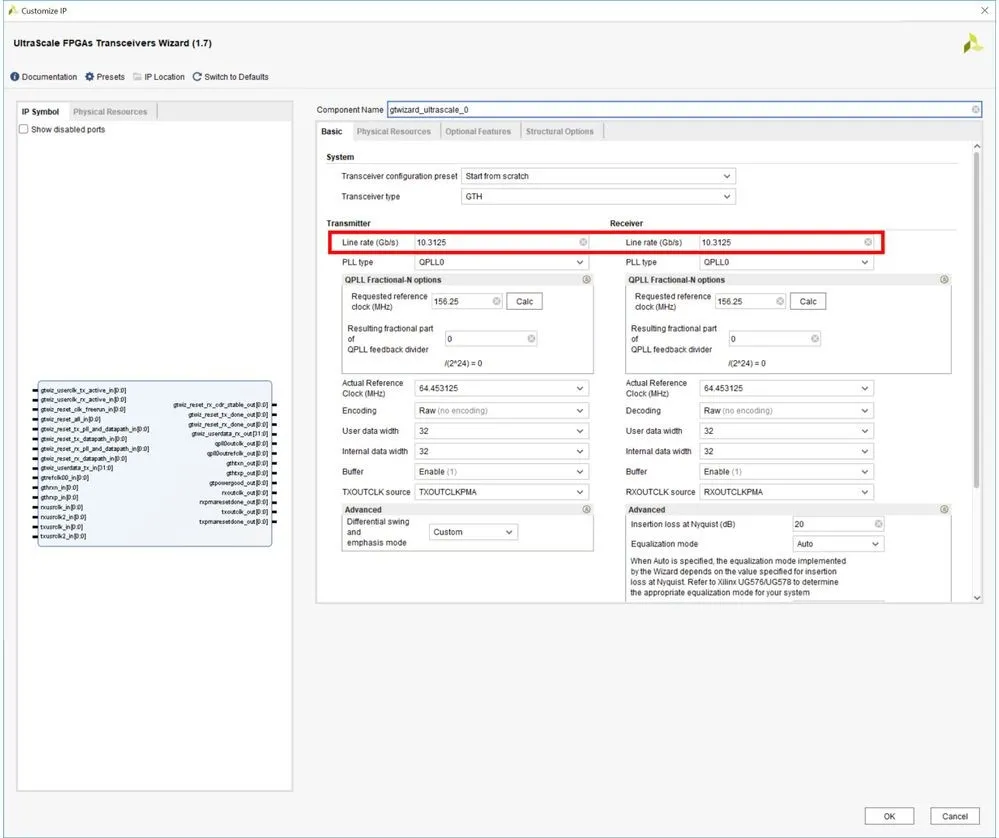

UltraScale/UltraScale+ GTH/GTY 收發(fā)器線速率設置的方法

如何調試 Zynq UltraScale+ MPSoC VCU DDR 控制器?

UltraScale/UltraScale+的時鐘資源

使用加密和身份驗證來保護UltraScale/UltraScale+ FPGA比特流

UltraScale和UltraScale+ FPGA封裝和管腳用戶指南

Zynq UltraScale+ MPSoC的隔離設計示例

AMD推出全新Spartan UltraScale+ FPGA系列

評論