作者:Mculover666

1.實(shí)驗(yàn)?zāi)康?br /> 通過例程探索Vivado HLS設(shè)計(jì)流

- 用圖形用戶界面和TCL腳本兩種方式創(chuàng)建Vivado HLS項(xiàng)目

- 用各種HLS指令綜合接口

- 優(yōu)化Vivado HLS設(shè)計(jì)來滿足各種約束

- 用不用的指令來探索多個(gè)HLS解決方案

2.實(shí)驗(yàn)內(nèi)容

實(shí)驗(yàn)中文件中包含一個(gè)矩陣乘法器的實(shí)現(xiàn),實(shí)現(xiàn)兩個(gè)矩陣inA和inB相乘得出結(jié)果,并且提供了一個(gè)包含了計(jì)算結(jié)果的testbench文件來與所得結(jié)果進(jìn)行對(duì)比驗(yàn)證。

3.實(shí)驗(yàn)步驟

3.1.在Vivado HLS GUI界面中創(chuàng)建項(xiàng)目

3.1.1.啟動(dòng)Vivado HLS 2018.1

3.1.2.創(chuàng)建一個(gè)新的工程

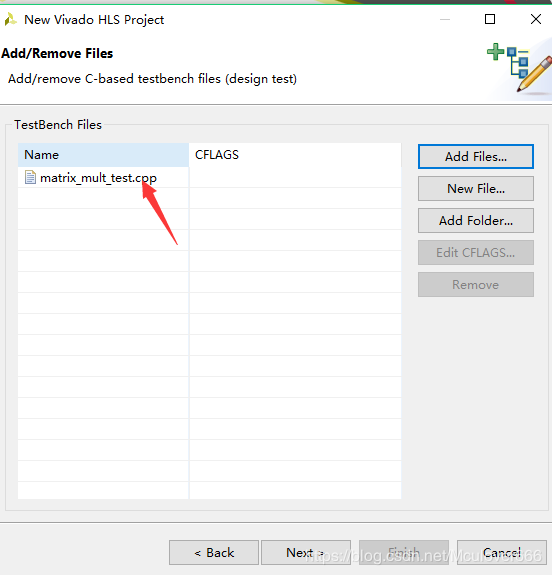

添加提前創(chuàng)建好的測(cè)試文件進(jìn)來:

工程創(chuàng)建完成,綜合界面如圖所示:

3.2.在Vivado HLS 命令行中快速創(chuàng)建項(xiàng)目

在3.1節(jié)中采用GUI界面完成了創(chuàng)建工程的工作,這個(gè)工程命名和添加文件創(chuàng)建工程的工作可以由一個(gè)TCL腳本完成,可以大幅提高我們的效率~

3.2.1.打開Vivado HLS 命令行界面

3.2.2.編寫創(chuàng)建工程TCL腳本

新建一個(gè)文件run_hls_pynq.tcl,然后編寫以下工程配置:

# 創(chuàng)建工程

open_project -reset matrix_mult_prj

# 添加源文件和測(cè)試文件

add_files matrix_mult.cpp

add_files matrix_mult.h

add_files -tb matrix_mult_test.cpp

# 設(shè)置工程頂層

set_top matrix_mult

# 創(chuàng)建解決方案

open_solution -reset solution1

# 選擇具體的FPGA芯片配置

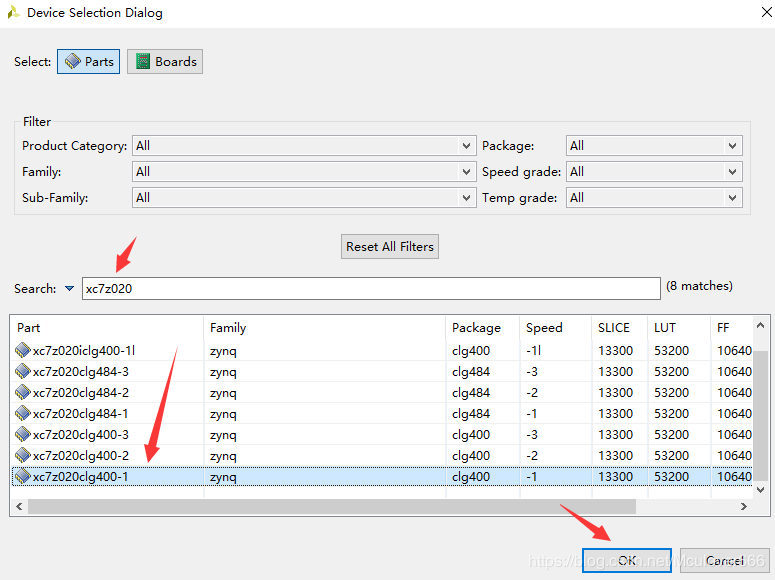

set_part {xc7z010clg400-1}

create_clock -period 5

exit

3.2.3.在Vivado HLS命令行運(yùn)行TCL腳本

在剛剛打開的Vivado HLS命令行界面中輸入cd ,然后輸入目錄所在盤符,進(jìn)入目錄后使用命令vivado_hls -f run_hls_pynq.tcl即可運(yùn)行腳本,完整過程如圖所示:

這樣一個(gè)工程就創(chuàng)建好了;

3.2.4.在Vivado HLS命令行打開創(chuàng)建的工程

使用命令vivado_hls -p matrix_mult_prj即可在GUI界面打開工程,如圖:

3.3.Vidavo HLS中的設(shè)計(jì)優(yōu)化

3.3.1.文件作用c

- matrix_mult.cpp 包含了迭代計(jì)算矩陣乘法的代碼

- matrix_mult.h 包含了宏定義和函數(shù)聲明

- matrix_mult_test.cpp 測(cè)試文件,包含了使用HLS硬件解決方案計(jì)算和軟件計(jì)算的結(jié)果,并計(jì)算驗(yàn)證

3.3.2.運(yùn)行C仿真

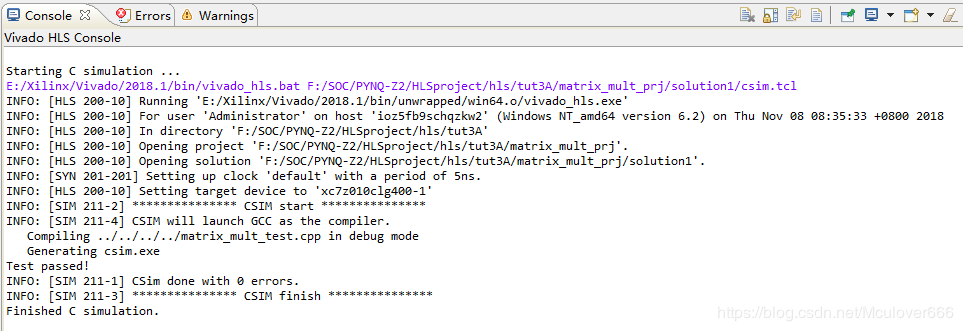

點(diǎn)擊Run C Simulation按鈕,然后不用選擇,直接下一步,可以看到控制臺(tái)輸出:

3.3.2.使用HLS綜合C++代碼

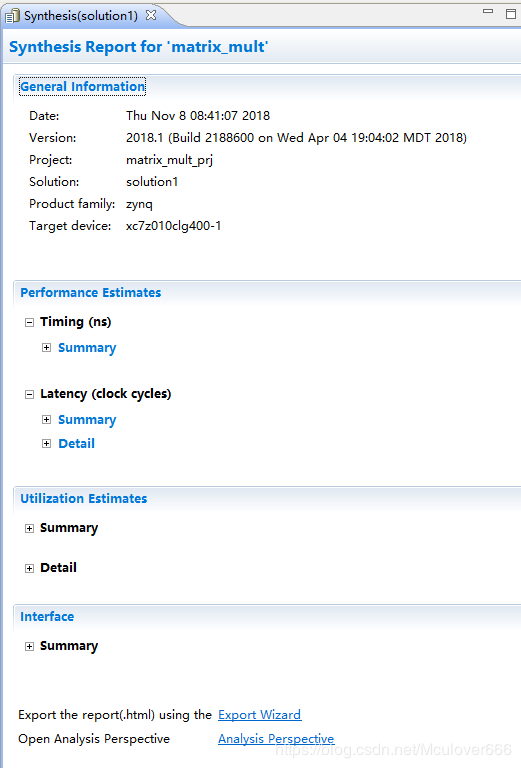

點(diǎn)擊C Synthesis按鈕,Vivado HLS會(huì)開始綜合C++代碼,綜合完成后會(huì)自動(dòng)打開綜合報(bào)告,其中詳細(xì)的描述了設(shè)計(jì)的時(shí)序以及FPGA資源占用估算等:

3.3.3.C/RTL共同協(xié)作

點(diǎn)擊Run C/RTL Cosimulation按鈕,選擇生成verilog語言文件,設(shè)計(jì)完成后會(huì)自動(dòng)彈出結(jié)果,如圖所示:

3.3.4.新建一個(gè)解決方案進(jìn)行對(duì)比

點(diǎn)擊New Solution按鈕新建一個(gè)解決方案:

然后打開matrix_mult.cpp文件,選擇右邊的directive視圖,右擊Product,選擇Inser Directive,然后選擇PIPELINE,確定之后運(yùn)行C綜合來綜合出RTL設(shè)計(jì),完成后同樣會(huì)彈出設(shè)計(jì)信息:

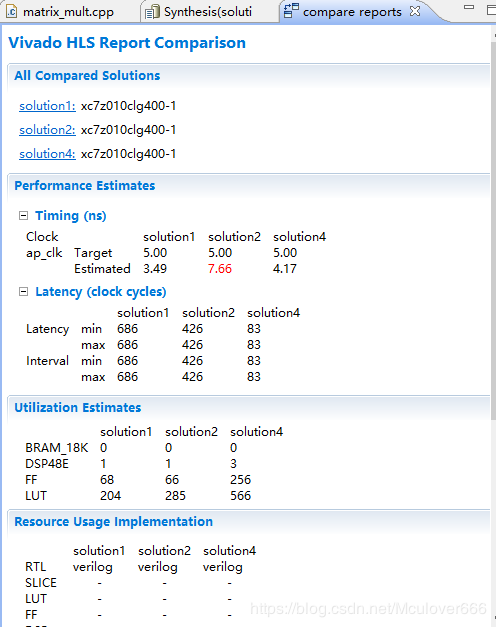

然后可以將報(bào)告與之前solution1的報(bào)告進(jìn)行對(duì)比,

3.3.5.分析

進(jìn)入Analysis視圖:

3.3.6.新建一個(gè)流水線解決方案

3.3.7.解決方案對(duì)比

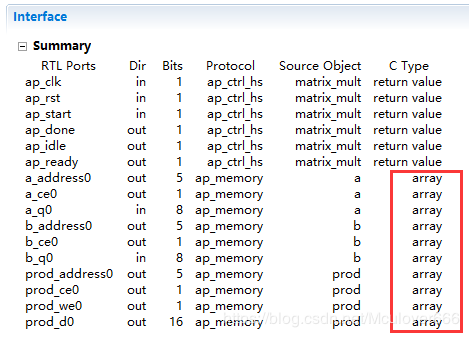

3.4.接口綜合

3.4.1.TCL腳本新建工程

在F:/SOC/PYNQ-Z2/HLSproject/hls/tut3C文件夾,使用命令:

vivado_hls -f run_hls_pynq.tcl

3.4.2.打開工程

vivado_hls -p matrix_mult_prj

3.4.3.C Synthesis

編輯:hfy

-

Vivado

+關(guān)注

關(guān)注

19文章

812瀏覽量

66470

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

Vivado 高層次綜合

來自vivado hls的RTL可以由Design Compiler進(jìn)行綜合嗎?

高層次綜合工作的基本流程

vivado高層次綜合HLS定義及挑戰(zhàn)

Vivado HLS設(shè)計(jì)流的相關(guān)資料分享

FPGA高層次綜合HLS之Vitis HLS知識(shí)庫簡(jiǎn)析

使用Vitis HLS創(chuàng)建屬于自己的IP相關(guān)資料分享

使用Vivado高層次綜合 (HLS)進(jìn)行FPGA設(shè)計(jì)的簡(jiǎn)介

Hackaday讀者有話說:Vivado HLS使用經(jīng)驗(yàn)分享

Vivado Hls 設(shè)計(jì)分析(二)

使用Vivado高層次綜合工具高效評(píng)估和實(shí)現(xiàn)所選壓縮算法

關(guān)于賽靈思高層次綜合工具加速FPGA設(shè)計(jì)的介紹和分享

基于Vivado高層次綜合工具評(píng)估IQ數(shù)據(jù)的無線電設(shè)備接口壓縮算法設(shè)計(jì)

PYNQ上手筆記 | ⑤采用Vivado HLS進(jìn)行高層次綜合設(shè)計(jì)

使用Vivado高層次綜合(HLS)進(jìn)行FPGA設(shè)計(jì)的簡(jiǎn)介

探索Vivado HLS設(shè)計(jì)流,Vivado HLS高層次綜合設(shè)計(jì)

探索Vivado HLS設(shè)計(jì)流,Vivado HLS高層次綜合設(shè)計(jì)

評(píng)論