作者:Evening

Xilinx每一個FPGA都有一個獨特的ID,也就是Device DNA,這個ID相當于我們的身份證,在FPGA芯片生產的時候就已經寫死在芯片的eFuse寄存器中,具有不可修改的屬性,因為使用的是熔斷技術。值得說明的是,在7系列及以前,這個ID都是57bit的,但是在Xilinx的Ultraslace架構下是96bit。

FPGA的DNA我們一般的使用場景是用于用戶邏輯加密。一般來說,用戶在邏輯上可以通過特定的接口把這個Device DNA讀取出來,經過一系列加密算法之后和預先在外部Flash存儲的一串加密后的字節串做比較,這個flash存儲的加密后的字節串也是由該DNA經過加密后得到,fpga加載程序后可以先從flash讀出該段字節做比較,如果相同,則讓FPGA啟動相應的邏輯,如不同,則代表該FPGA沒有經過用戶授權,用戶邏輯上可以關閉FPGA的邏輯功能甚至可以通過一些手段讓硬件損壞。

如何獲取FPGA的Device DNA呢,下面我從JTAG和調用源語兩個方法說明,并開放核心代碼供大家參考。

第一種,通過JTAG獲取,這種方法在ISE的Impact或者vivado都可以實現,下面介紹在Vivado下如何或者Device DNA,這個其實很簡單,首先板卡通過JTAG連接PC,在Flow Navigator -> PROGRAM AND DEBUG 界面下,點擊對應的FPGA的芯片,點擊Hardware Device Properties,在search中搜索dna,在REGISTER下可以找到Device DNA,在Impact下如何獲取DNA網上有相應的文章,這里就不做進一步介紹。

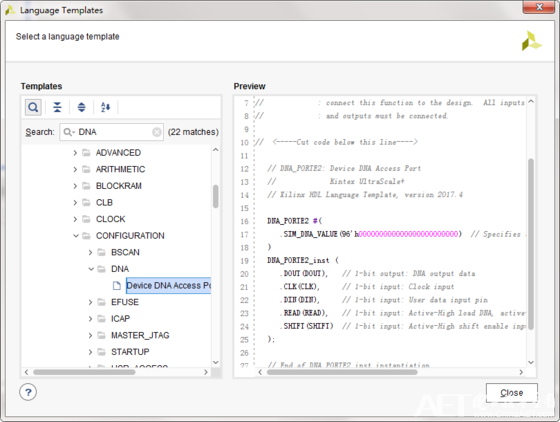

第二種,用戶邏輯通過調用源語獲取,至于源語是什么,這里跟大家分享一個技巧,一般我們使用源語的時候,往往記不住大量的源語定義,那么如何快速搜索到我們想要的源語呢,在Vivado中,有一個功能是Language Templates,在Flow Navigator可以找到,里面包含了基本所有的Xilinx提供的源語和一些語法用法,以DNA讀取為例,我們搜索DNA,就可以找到關于DNA的源語,由于博主用的是VU9P的片子,所以用的是DNA_PORTE2這個源語,針對7系列及以前,使用的是DNA_PORT源語,這兩個源語都可以在Language Templates找到。

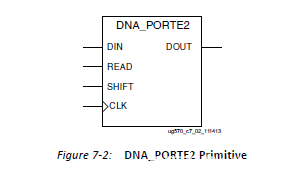

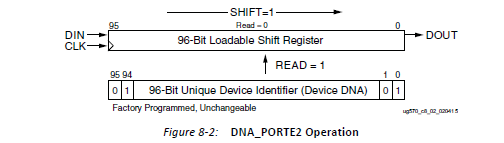

接下來說一下這個源語和源語相關的使用方法,這個源語本質上就是讀取FUSE寄存器表里面的FUSE_DNA寄存器,里面還包含了一個移位寄存器,源語中的接口本質上都是操作移位寄存器,這個移位寄存器的長度和器件類型有關,是56或者96bit。源語里面的READ信號,是用于把DNA的值裝載到移位寄存器里面,DIN是移位寄存器的輸入,DOUT是移位寄存器的輸出,SHIFT是移位寄存器的移位使能,CLK是移位寄存器的操作時鐘,官方提供的源語模型和時序圖如下,

對于用戶來說,調用這個源語,我們只需要按照操作移位寄存器的流程操作就好了,我們目的是讀出源語里面的移位寄存器的值,所以我們設計的思路應該是首先拉高READ先讓移位寄存器裝載DNA的值,然后在時鐘上升沿使能SHIFT,這樣子就能讓移位寄存器里面的值移位出來,下面是核心代碼:

module dna_read(

input sys_clk,

input dna_read_rdy,

output [95:0] dna_read_dat,

output dna_read_vld);

wire dna_dout;

wire dna_read;

wire dna_shift;

DNA_PORTE2 #(

.SIM_DNA_VALUE (96'd0)

)DNA_PORTE2_inst(

.DOUT (dna_dout),

.CLK (sys_clk),

.DIN (dna_dout),

.READ (dna_read),

.SHIFT (dna_shift)

);

reg [95:0] dna_reg = 0;

reg [7:0] dna_cnt = 0;

always @ (posedge sys_clk)

begin

if(dna_read_rdy) begin

dna_cnt end

else begin

dna_cnt end

end

// load dna data from the fuse dna register

assign dna_read = dna_cnt == 8'd63;

// for ultrascale

assign dna_shift = (dna_cnt >= 8'd100) && (dna_cnt

always @ (posedge sys_clk)

begin

dna_reg end

assign dna_read_dat = dna_reg;

assign dna_read_vld = dna_cnt == 8'd196;

endmodule

這是一個axis總線的模塊,在dna_read_rdy拉高表示外部準備好接收數據,這時候模塊讀取DNA的值,然后送出去給外部模塊,外部模塊收到數據和dna_read_vld信號,則拉低dna_read_rdy,完成一次dna數值傳輸流程。

編輯:hfy

-

FPGA

+關注

關注

1646文章

22094瀏覽量

620565 -

寄存器

+關注

關注

31文章

5446瀏覽量

125327 -

Xilinx

+關注

關注

73文章

2185瀏覽量

127068

發布評論請先 登錄

【米爾-Xilinx XC7A100T FPGA開發板試用】Key-test

基于Xilinx ZYNQ7000 FPGA嵌入式開發實戰指南

【米爾-Xilinx XC7A100T FPGA開發板試用】測試一

dac3174與xilinx zynq7000系列連接,fpga的案例參考代碼有沒有?

采用Xilinx FPGA的AFE79xx SPI啟動指南

正點原子fpga開發指南

Xilinx 7系列FPGA PCIe Gen3的應用接口及特性

詳解FPGA的基本結構

【招聘】verilog vhdl FPGA

評論