當今的高速PCB設計具有兩個因素:移動大量數據和信號帶寬,頻率范圍高達非常高的頻率。結果,有幾件事會影響這兩個因素。在“如果您做得不好,您將死在水里”列表頂部的那些元素中,損失很小。在設計過程中有很多事情會影響損耗,但是要做出的基本決定是所選層壓板的介電損耗正切值。簡而言之,介電損耗正切將限制PCB上傳輸線的有效長度,因為它會導致信號電平在傳播過程中降低。

本文將介紹介電損耗角正切,它在高速設計中的作用,它如何取決于玻璃與樹脂的比率和頻率,如何測量它以及對當今產品的影響。對于以32 Gbps速度運行的電路板,我們將研究為什么構建測試板對于合格損耗正切的必要性。

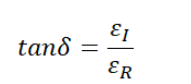

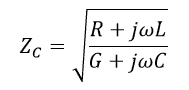

介電損耗角正切有時稱為耗散因數,其符號為Df。在傳輸線的設計和RF設計中,電介質損耗角正切與黃褐色(定義δ ),這是在其中由電磁場(RF)通過電介質行進攜帶的能量由電介質吸收的速率的量度。當一種材料被稱為“高速”時,它就是Df值。需要牢記的一些要點包括:

在PCB和微波組件使用的頻率下,電介質吸收的能量通常隨頻率增加,直到進入高GHz范圍。

損耗隨頻率增大,這是因為不斷變化的電磁場導致電介質中的分子振動。它們振動得越快,損失就越大(下文對此進行了更多介紹)。

材料的損耗角正切值越低,功率損耗就越低。

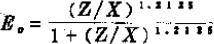

就材料的介電常數而言,任何材料的介電損耗角正切都有一個簡單的方程:

如果知道介電常數的虛部和實部,則可以計算損耗角正切。如果查看PCB層壓板數據表,通常會看到介電損耗正切值和Dk值。只需將它們相乘即可得到介電常數的虛部。

都是分子的

PCB中使用的頻率下電介質的損耗是由于分子由相反的電荷形成而形成,該電荷可以相互吸引和排斥。如果分子中的原子由于電場而移離平衡狀態,則它可以開始振蕩。所有材料都將具有一定的損耗角正切,即使在大多數PCB使用的頻率下損耗很小。

例如,考慮具有極性和非對稱結構的水。有一個氧原子和兩個氫原子形成V形,其中氧原子為負端,氫原子為正端。當水分子經受變化的電場時,它會振動。請注意,分子動能與溫度直接相關,因此,傳播場引起的分子振動會導致基板中的溫度升高。這就是為什么微波爐可以工作的原因。食物中的水由于電場的振動而達到高溫。由于在極性分子的不同區域中更大的電荷分離,所以分子與非極性分子相比可以具有更高的介電損耗角正切。

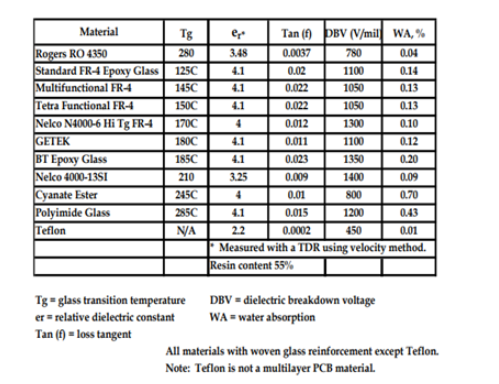

表1中的信息表明,用于制造多層PCB的大多數材料具有相對較高的損耗。(要歸類為低損耗,損耗角正切應低于.004。)

表1.某些常見層壓系統的特性

PCB設計人員面臨的挑戰是確定一種材料何時損耗太大,必須用損耗更低的替代品來代替。由于損耗是頻率和傳輸線長度的函數,因此沒有簡單的規則可用來確定何時必須進行切換。

介電損耗角正切,頻率和玻璃與樹脂的比率

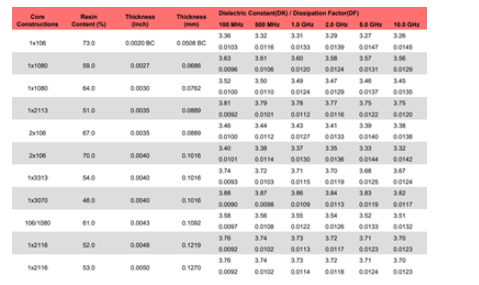

給定的PCB層壓板由樹脂體系和玻璃纖維增強布制成,每一種都有不同的損耗角正切值。因此,由于使用不同比例的玻璃和樹脂來制作具有各種厚度的PCB層壓板,因此總損耗角正切值將有所變化。當信號完整性工程師僅獲得一組層壓板的單個損耗角正切值時(例如Panasonic及其Megtron 6材料系統),這就會給信號完整性工程師帶來問題。表2顯示損耗角正切如何隨頻率和玻璃與樹脂的比率變化。這是Isola Corporation的FR408HR核心材料的數據。

該表包含一個特性良好的PCB層壓板系統的示例。可以看出,介電損耗角正切隨頻率增加的幅度大于其隨玻璃與樹脂之比變化的幅度。這是因為,在該體系中,樹脂體系和玻璃的損耗角正切非常接近。在其他樹脂體系中,這可能有所不同。

測量數字層壓板的介電損耗正切

本文末尾的參考文獻2顯示,IPC記錄了23種不同的方法來測量層壓板中的介電損耗角正切。這些方法中的每一種都是針對特定應用開發的。由于首先需要低損耗層壓板的應用是微波和RF,因此大多數測試方法已針對特定類型的電路(如相控陣雷達)進行了優化。與超高速數字電路的需求相比,這些應用可被視為“窄帶”。

這些方法中只有一種方法以可用于數字多層PCB設計的方式表征層壓板。已證明與帶狀線傳輸線構造的PCB上進行的實際測試具有最佳關聯。所有其他方法都使用諧振腔或其他類型的測量單元,這些單元在狹窄的頻率范圍內表征層壓板,并且它們都有一些誤差。

介電損耗正切數據不完整時該怎么辦?

典型的層壓板數據表沒有包含足夠的有關介電損耗的信息,因此無法對高速數字數據路徑中的潛在損耗進行正確的建模和分析。那么,如何才能確保設計在最終構建時能夠按規格工作?工程師在開發使用最新高速數據鏈路的產品時,都會出現這個問題。由于需要精確地考慮銅走線的損耗,這可能會更加復雜,銅走線的損耗受走線的總表面積以及銅表面粗糙度的影響。

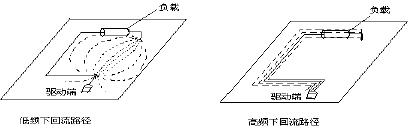

即使準確知道損耗角正切,也沒有可靠的方法可以對所有這些效應進行建模。因此,產品開發人員別無選擇,只能用實際的傳輸線構造測試PCB。將其用于最終產品并進行測試以確定所考慮的層壓板的損耗與頻率的關系,并查看是否可以達到目標。這是為高性能系統構建設計規則集的唯一安全方法。圖1是兩套實際測試PCB的照片,幾年前我們使用它們來驗證超級計算機中的路徑為5.2 Gb / S和TB路由器中的路徑為4.8 Gb / S。這些測試PCB的設計使其在插入在一起時將創建子板/背板接口,以及從背板和子板到外界的接口。

圖2. 5.2 Gb / S和4.8 Gb / S數據路徑的測試PCB集

那么,如何為當今的32 Gb / S和56 Gb / S數據路徑進行設計呢?

當您設計具有32 Gb / S或56 Gb / S數據路徑的產品時,您必須構建測試板以確保產品能夠按設計工作,這可能不足為奇。Speeding Edge的創始人兼總裁Lee Ritchey指出:“一旦進入這些數據路徑,損耗正切就變得更加令人擔憂。您可以構建類似于上述內容的測試板。您只需測量更遠的頻率即可。這些數據速率支配著產品的性能,它們決定了板上的路徑長度。等式非常簡單,路徑越長,損失就越大。”

32 Gb / S和56 Gb / S的速度下,您將超越極限。” 相比之下,光纖通道的損耗要少兩個或三個數量級。當大型機器(例如用于掃描半導體的機器)之間存在盒對盒連接或截面到截面空間時,在很多地方都必須使用光纖。這是痛苦的昂貴,因為在路徑的每一端都必須有一個收發器,每個收發器的價格為50美元。因此,激勵措施是留在銅中。在10 Gb / S服務器場中,我們對收發器進行了改進,以使我們可以通過100英尺長的6類電纜進行10 Gb / S的傳輸。但是,從10 Gb / S提升到56 Gb / S是一個巨大的飛躍。真正好的收發器只能處理大約30英寸。”

編輯:hfy

-

PCB設計

+關注

關注

394文章

4688瀏覽量

85586 -

RF設計

+關注

關注

1文章

27瀏覽量

13093

發布評論請先 登錄

相關推薦

電容器損耗角正切值知識

高速PCB設計經驗與體會

鉭電容的損耗角正切和耗散因數

高速PCB損耗性能的影響分析

PCB設計中介電損耗角正切高速設計作用

PCB設計中介電損耗角正切高速設計作用

評論