在Vivado FIR濾波器設(shè)計(jì)與仿真(一)中產(chǎn)生了兩路正弦信號,頻率分別為4MHz和5MHz,今天要進(jìn)行FIR濾波器設(shè)計(jì),在進(jìn)行濾波器設(shè)計(jì)之前,需要對濾波器的參數(shù)進(jìn)行設(shè)置,需要借助MATLAB軟件或者Filter Solutions軟件,這次使用Filter Solutions來進(jìn)行參數(shù)設(shè)定。

關(guān)于Filter Solutions軟件的使用,這里有一篇博客比較詳細(xì)的介紹了它的用法,可以作為參考:

Filter Solutions之濾波器設(shè)計(jì)

濾波器參數(shù)

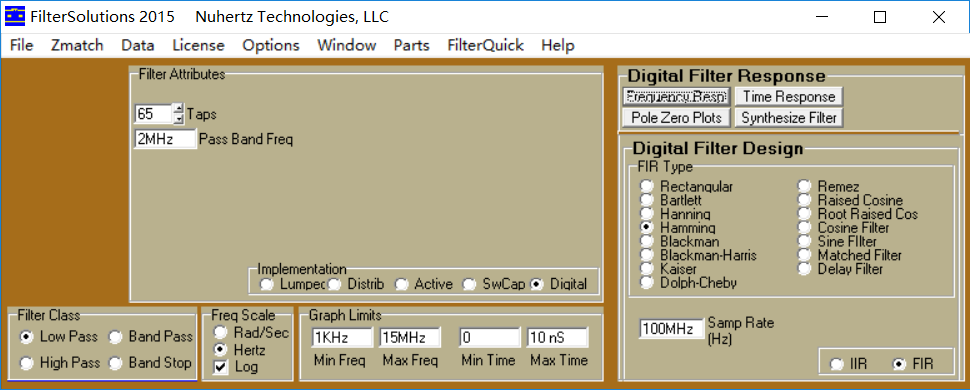

產(chǎn)生的兩路正弦信號分別為4MHz和5MHz,混頻之后產(chǎn)生的信號頻率為1MHz和9MHz,首先進(jìn)行低通濾波設(shè)計(jì),我們要把1MHz的信號濾除掉,F(xiàn)ilter Solutions軟件參數(shù)設(shè)置如圖所示:

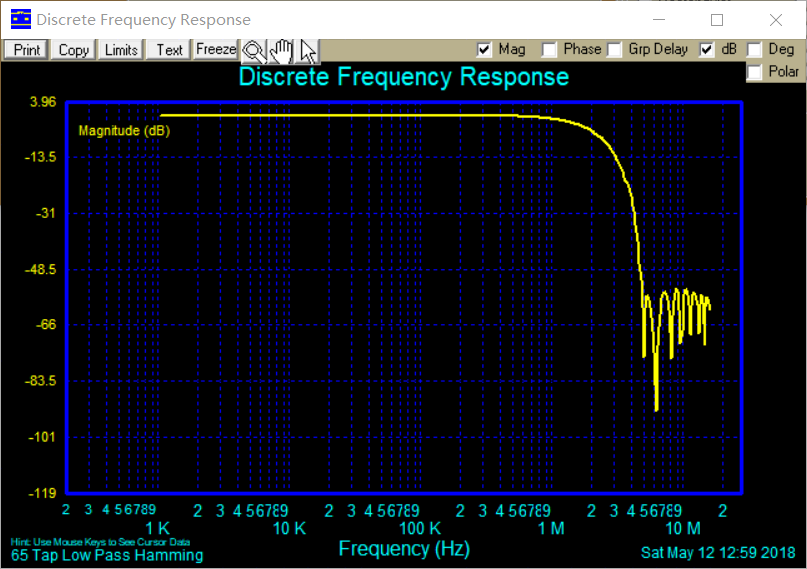

參數(shù)設(shè)定之后生成頻響圖:

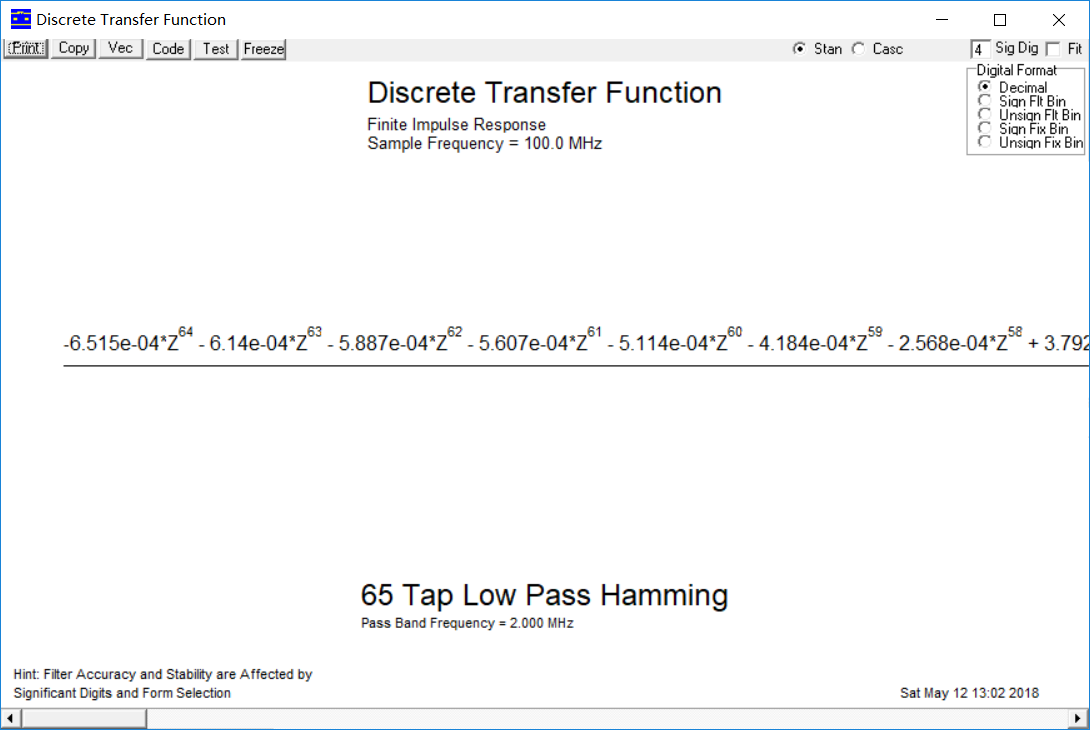

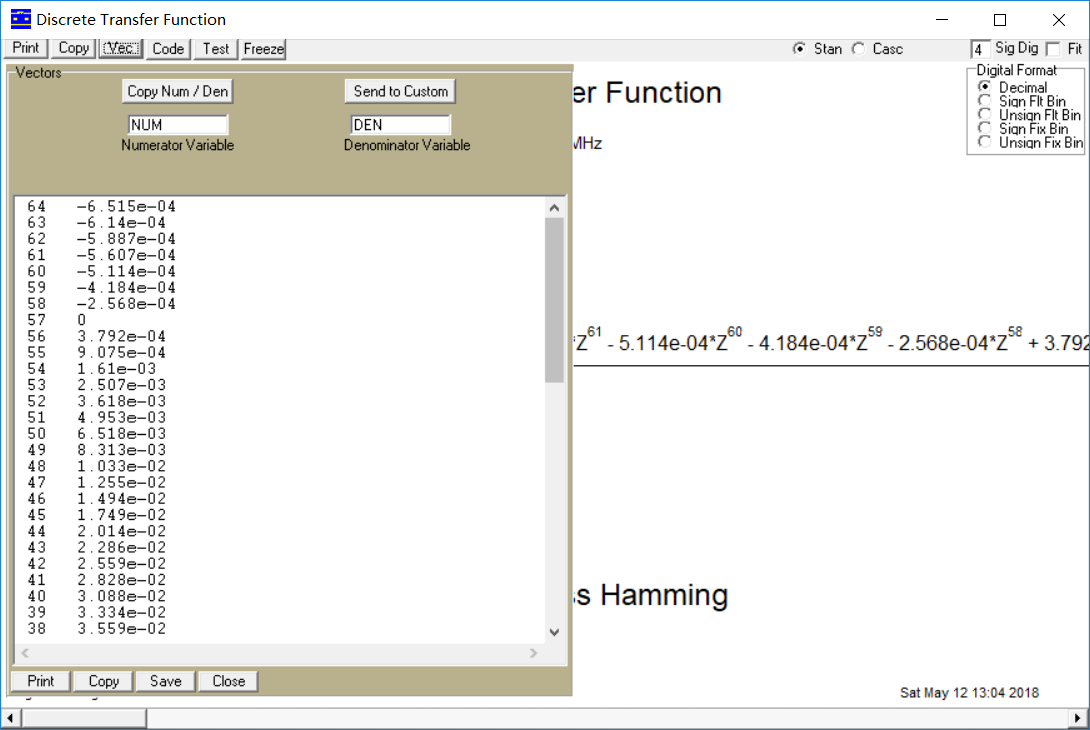

查看相關(guān)參數(shù)并復(fù)制參數(shù):

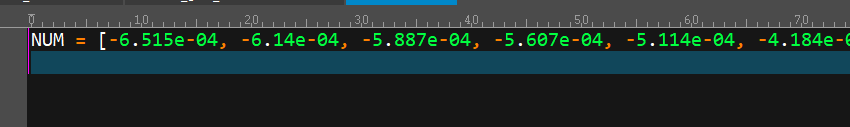

我們把復(fù)制的參數(shù)粘貼出來可以看到是下面的格式:

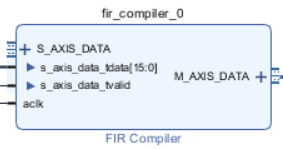

雙擊打開進(jìn)行相關(guān)參數(shù)設(shè)定:

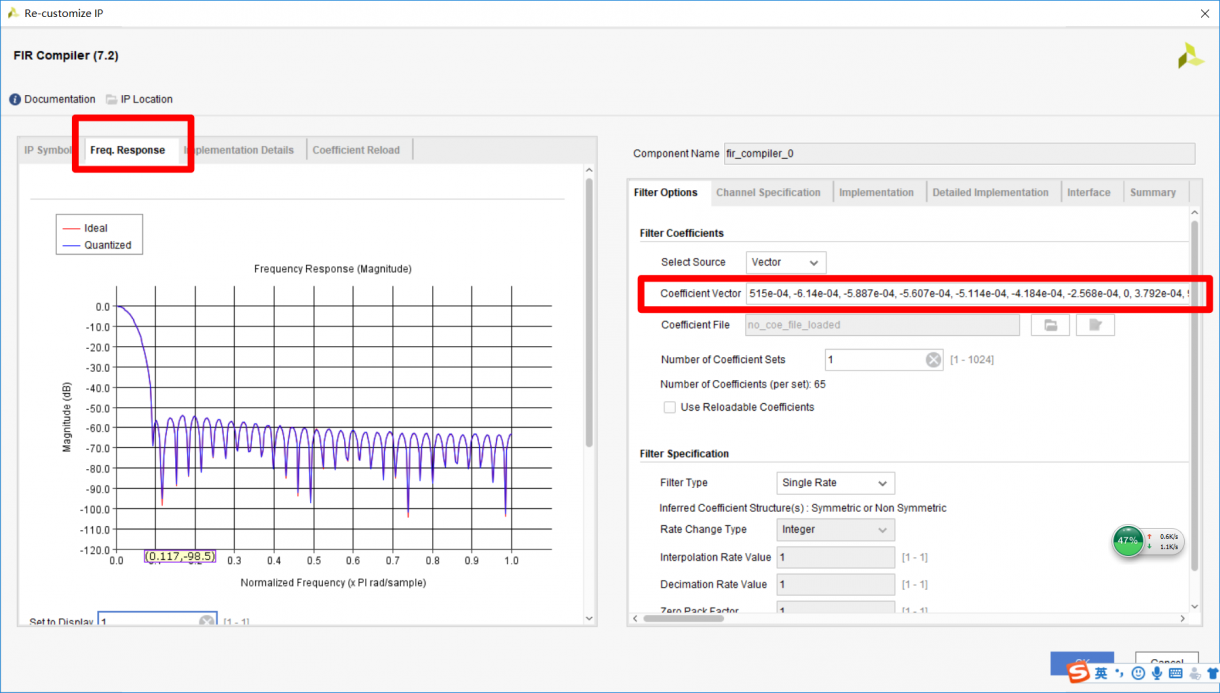

我們把在Filter Solutions軟件中得到的參數(shù)復(fù)制到圖中紅色框中,在左側(cè)Freq.Response中就可以看到頻率響應(yīng)圖

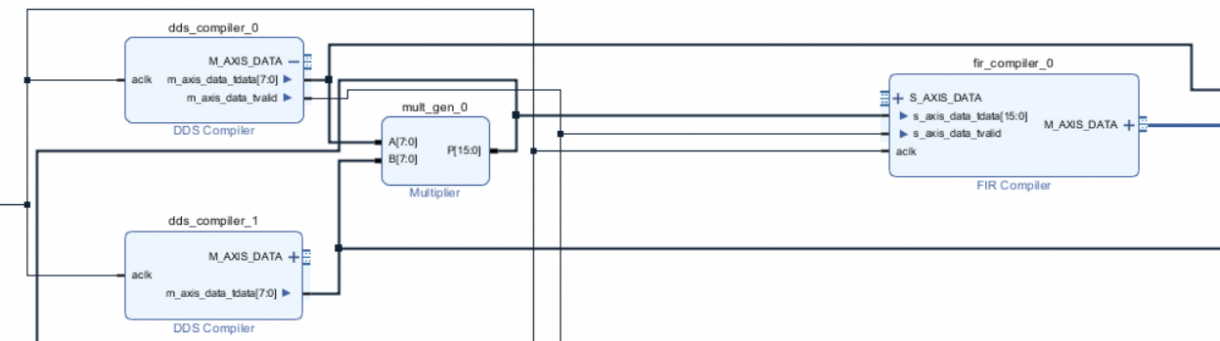

選中FIR的M_AXIS_DATA引腳,右鍵make external連接管腳,也可以將兩路正弦信號連接出來進(jìn)行觀察,連接好之后,valid design沒有錯誤就OK了

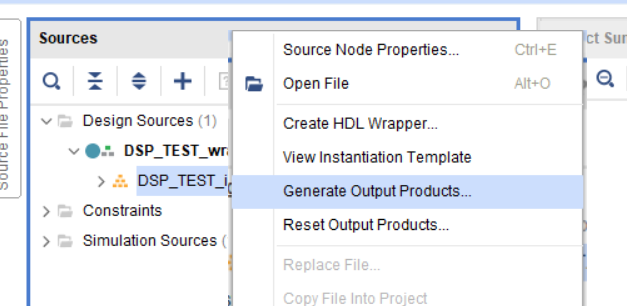

返回到source界面,右鍵菜單中選中g(shù)enerate output products,更新頂層文件。

更新之后就可以看到頂層文件中多了一路信號

Modelsim仿真

我們將新增的一路濾波信號添加到仿真文件中即可進(jìn)行仿真

module tb_top(

);

reg aclk_0 ;

wire [31:0]S_0;

wire[39:0] M_AXIS_DATA_0_tdata;

initial

begin

aclk_0 = 1;

end

always #5 aclk_0 = ~aclk_0 ;

DSP_TEST_wrapper DSP_TEST_wrapper_i

(.M_AXIS_DATA_0_tdata(M_AXIS_DATA_0_tdata),

.aclk_0(aclk_0),

.S_0(S_0));

endmodule

仿真后添加仿真波形進(jìn)行查看:

可以看到在仿真結(jié)果中,低頻信號被濾除了

編輯:hfy

-

FPGA

+關(guān)注

關(guān)注

1629文章

21736瀏覽量

603234 -

fir濾波器

+關(guān)注

關(guān)注

1文章

95瀏覽量

19039 -

Vivado

+關(guān)注

關(guān)注

19文章

812瀏覽量

66509

發(fā)布評論請先 登錄

相關(guān)推薦

基于FPGA實(shí)現(xiàn)FIR數(shù)字濾波器

三合一濾波器的高效電磁兼容解決方案

DC/DC轉(zhuǎn)換器中輸入濾波器穩(wěn)定性問題的簡單解決方案

emi濾波器是什么濾波器

陷波濾波器怎么進(jìn)行濾波

iir濾波器和fir濾波器的優(yōu)勢和特點(diǎn)

基于 FPGA 的任意波形發(fā)生器+低通濾波器系統(tǒng)設(shè)計(jì)

matlab與FPGA數(shù)字信號處理系列 Verilog 實(shí)現(xiàn)并行 FIR 濾波器

有源濾波器和無源濾波器的原理及區(qū)別是什么

Vivado 使用Simulink設(shè)計(jì)FIR濾波器

高通濾波器、低通濾波器、帶通濾波器怎樣測幅頻特性?

基于多速率DA的根升余弦濾波器的FPGA實(shí)現(xiàn)

Matlab生成fir濾波器抽頭系數(shù)的流程

Vivado經(jīng)典案例:使用Simulink設(shè)計(jì)FIR濾波器

Pi濾波器的Python實(shí)現(xiàn)示例

Vivado FPGA實(shí)現(xiàn)濾波器設(shè)計(jì)解決方案

Vivado FPGA實(shí)現(xiàn)濾波器設(shè)計(jì)解決方案

評論