鑒于芯片設計的復雜度提升, 成功設計一個芯片所牽扯的步驟與過程也愈加復雜,所需花費的資金也成倍增加,一個典型的芯片開發項目的周期和花銷如下所示

可以見到在芯片制造出來之前,很多精力會花費在RTL代碼驗證工作上,另外軟件的相關開發工作,也會在得到芯片前開始,這2方面都需要借助FPGA原形來模擬芯片的行為,幫助硬件開發和軟件開發者,共同提升工作效率。

FPGA原型在數字芯片設計中,基本是必不可少的,原因非常明顯,相比用仿真器,或者加速器等來跑仿真,FPGA的運行速度,更接近真實芯片,可以配合軟件開發者來進行底層軟件的開發。當然FPGA原型作為芯片的替身,也是有諸多限制的,比如規模限制,速度限制,功耗限制,結構限制等,在使用FPGA原型作為芯片的替代時,需要進行相應的修改,才能完成相應功能,甚至有些功能最終無法覆蓋。

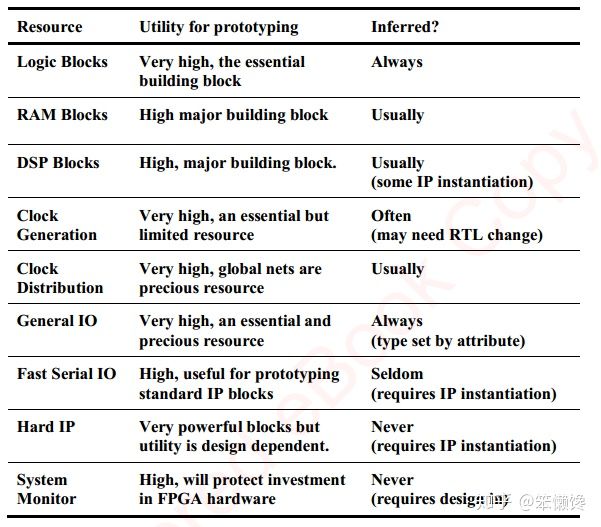

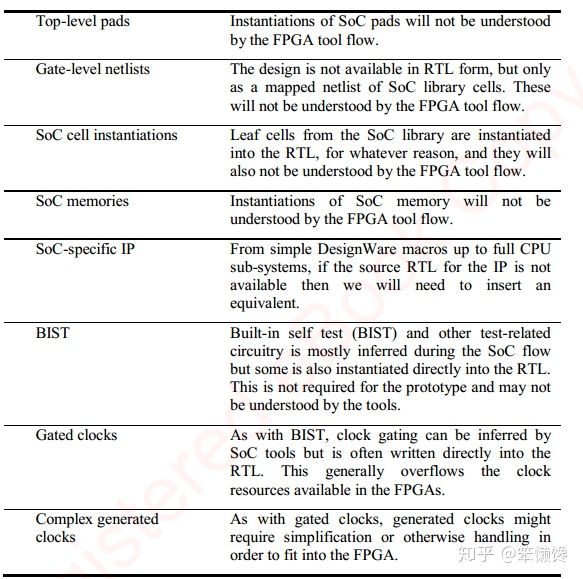

如果對FPGA中可以映射為ASIC的資源做逐一對比,我們可以得到這樣的表格。

以上表格看出,除了普通的RTL邏輯以及基本端口,其他的類似存儲時鐘DSP等,最好都是做手動修改進行映射,把ASIC設計轉換為FPGA比較靠譜。

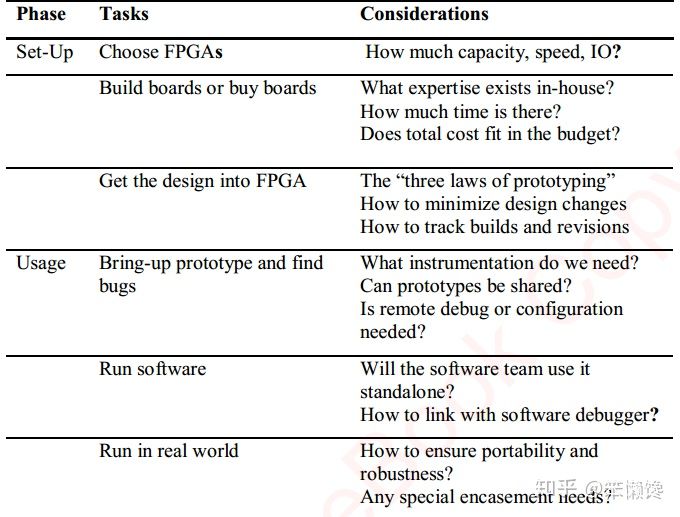

要把一塊ASIC做出FPGA的原型,需要大致一下步驟,

1 FPGA選型

2 做板或者購買原型板。

3 將ASIC設計轉換裝入FPGA

4 調試啟動FPGA原型

5 載入軟件協同運行

6 軟硬件系統驗證

下文就按照這些步驟逐一討論:

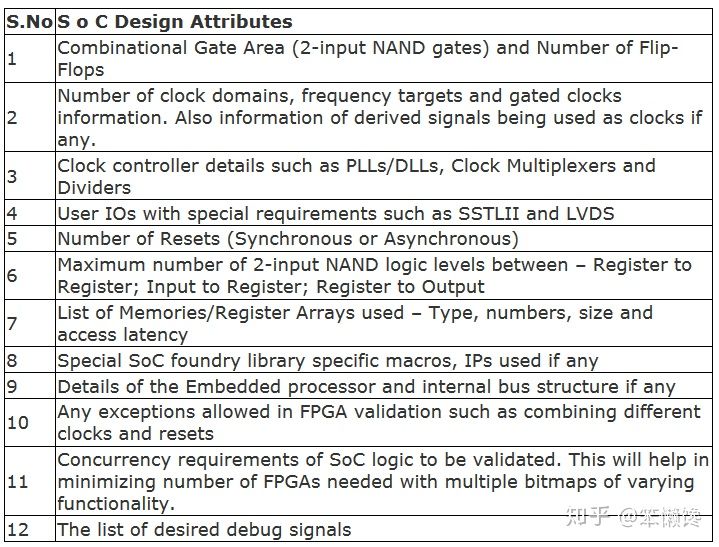

第一個就是FPGA的選型問題,在選型前,當然需要對ASIC的設計進行大致的了解,包括以下各方面:

選型問題最關心的幾個維度:

1 容量 其中包括純邏輯容量,存儲容量,dsp單元容量這些

2 內置IP 包括時鐘,存儲控制,cpu等的硬核

3 接口 普通接口與專用高速接口

4 速度 資源占用率在50%左右時的速度,一般被用來評估原型

其中純邏輯容量,也就是ASIC中組合電路與觸發器的容量,是可以直接與FPGA中的資源換算的。

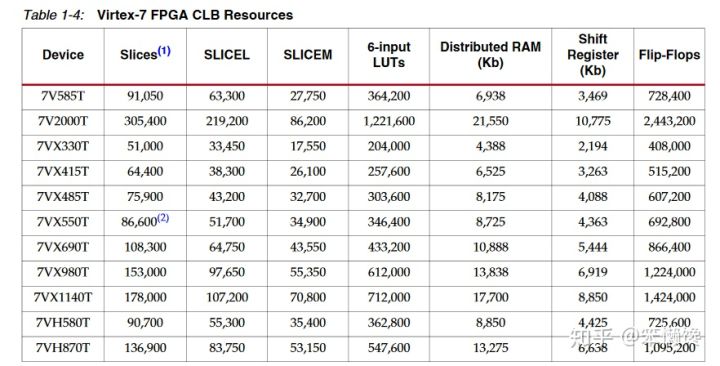

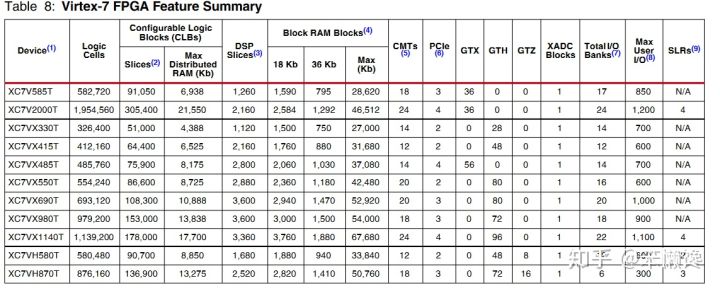

比如上圖xilinx V7 2000T中有2.4M FF,大致對應ASIC的2輸入與非門10M gates,如果使用率按照50%算,大概放置5M邏輯門沒問題。

內置的存儲器,可以實現21M的單雙端口ram,rom,fifo等,如果ASIC中使用的存儲稍微多一點,也可以用lut實現部分的存儲,替代block ram。

如果使用較多乘加運算,也可以映射fpga中的dsp器件實現,具體各種型號的FPGA包含多少器件,可以參考xilinx文檔。

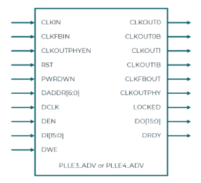

對于內置ip,最先要考慮的,就是時鐘模塊MMCM,一般FPGA會有幾個到幾十個時鐘模塊,例如下表2000T中包含24個CMTs,也就是24個PLL和MMCM,每組PLL和MMCM可以對一個時鐘域的時鐘進行分頻倍頻。一般ASIC會包含多個時鐘域,每個時鐘域至少需要一個CMTs對時鐘進行操作,可以據此選擇使用哪個FPGA器件。

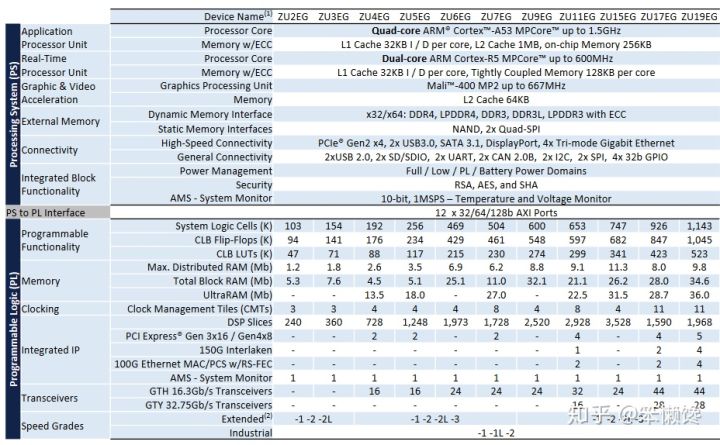

如要選擇帶有ARM硬核的FPGA來模擬ASIC中的ARM核,則需要選擇zynq系列。系統中自研的邏輯,則通過AXI掛入總線中,當然這樣未必能使FPGA與ASIC中的系統完全一致,但是作為一個圓形,也是足夠的,以下是部分帶有ARM核的FPGA的容量以及相應IP情況

對于接口的限制,一般FPGA的普通接口數量夠大,不會成為瓶頸,主要在于ASIC所需的特定接口,在FPGA中是否能夠滿足,很多時候這些特定接口需要外接phy才能完成相應功能。

影響FPGA最終運行速度的因素很多,包括代碼風格,具體設計,資源占用率,FPGA型號等,所以這需要在RTL代碼基本框架完成后,通過工具綜合才能得到一個大致數值,所以作為ASIC原型,盡量選擇速度夠快的FPGA。

通過以上限定條件,基本可以選出使用哪種FPGA型號,但是可能ASIC資源占用太多,任何一種都裝不下,這就有2種解決方式了。一種是分塊分別驗證,當然這樣風險極高,且沒法直接驗證最終系統。

另外就是使用多片FPGA得到原型,這就要涉及不同FPGA之中功能劃分的問題,這個是比較麻煩且有難度的事情,對FPGA電路設計,以及ASIC到FPGA的代碼轉換,都有挺多新問題。

第2步就是制版,這需要考量的方面也是相當多,比如信號完整性,電源問題,時鐘問題,可擴展性等,本人對此沒有直接經驗,也就無從展開。當然對于需要多個FPGA的驗證板,一般實力的團隊,未必能搞定,所以選擇花錢買平安,直接選用類似HAPS這樣的驗證系統,可能更靠譜。

第3步就是ASIC的設計裝入FPGA。這需要對原本面向ASIC的代碼,進行修改。

對于一般的純RTL邏輯,在ASIC中與FPGA中都可以綜合出可用結果,但是以下表中的器件,需要修改

芯片中的pad,一般是fab廠給出的硬核,具有輸入輸出,驅動上下拉控制等。在轉換成FPGA時,一般會在例化中直接用assign替代,并.XDC或者.v中指定上下拉等

如果有ASIC門級網表,可以把底層ASIC實例器件用verilog行為描述替換,在FPGA綜合中則可以對應實現。其他的簡單cell例化,也可以這樣轉換一下。

對于存儲器,一般可以在FPGA中找到與ASIC功能一致的SRAM,ROM ,可以直接把FPGA MEM 外包一層改變端口名字,替代ASIC MEM。小的嵌入flash,則可以把FPGA的SRAM包一層邏輯來模仿。

其他的硬核IP, 可能需要在FPGA中尋找功能一致的,并相應修改接口,與ASIC代碼中其他部分有效連接。

對于BIST,最直接的辦法是去除,一般不會影響實際功能。

對于各種門控時鐘,倍頻分頻等,一般需要針對FPGA做手動修改,使用DCM完成與芯片中時鐘一致的行為。

以下就一些修改中會出現的具體問題,詳細說明。

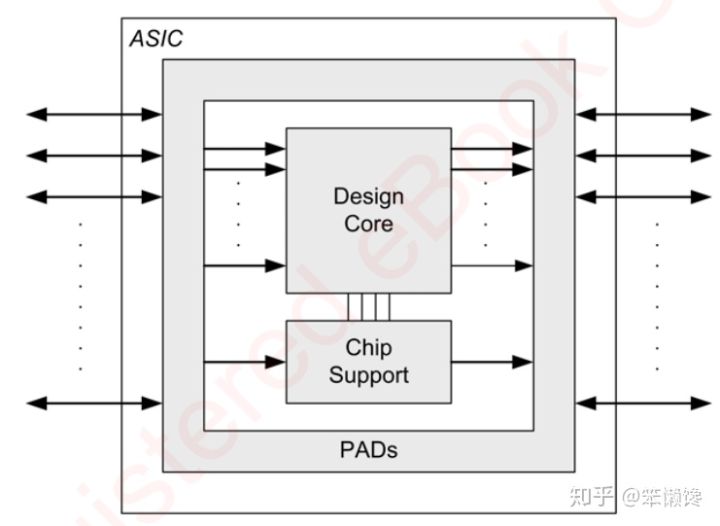

首先我們拿到的ASIC設計的結構,基本如下圖所示,最外一圈是各種pad ring,里邊先是芯片的各種輔助功能,包括 clk, rst, power, test,debug等。然后是與芯片實際功能相關的部分,可能包括部分模擬電路,數字電路包括cpu,mem 總線,各種邏輯控制等。我們需要明確用FPGA來原形驗證的,主要是數字電路中的那些核心功能,芯片核心外部的那些輔助邏輯,很多是需要修改的,也是無法得到驗證的。這里的pad一般直接在FPGA中直接去例化一個包含幾個assign語句的 FPGA PAD 等效實例,clk rst 需要根據具體上電順序,時鐘資源做調整,一般會對rst功能進行簡化,做成一個全局復位,clk中的分頻與關斷功能會放在CMT中實現。power控制,一般在FPGA中直接忽略,因為用FPGA幾乎無法模擬各種UPF指定的行為。debug test可以根據實際情況保留或者去除,但是即使保持,一般也不會真的去用。核心功能中需要更改的,一般就是各種內部存儲器了。

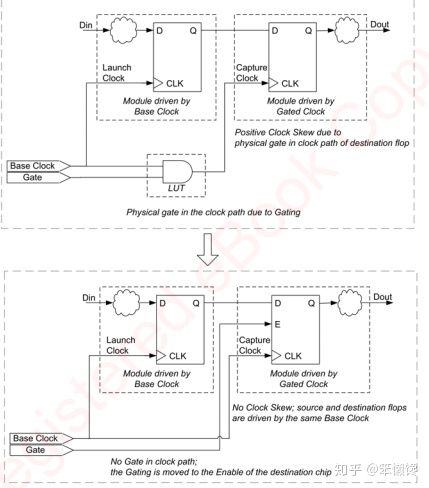

時鐘門控 clock gating 一般在ASIC中廣泛使用,一般會在clk模塊中例化成由latch與門組成的門控單元,對某個模塊進行時鐘控制。這些門控單元,如果直接在FPGA中例化為相同邏輯的latch與門,邏輯功能是沒有問題的。但是這時與門出來的受控時鐘,則不能再FPGA的專用時鐘網絡中走線,而是走普通的信號網絡,這樣FPGA能達到的頻率很差。為了糾正這樣情況,可以把對寄存器的門控,放在寄存器端,也就是選用FPGA中行如FDCE這樣帶門控的寄存器。這個過程可以手動完成,但是比較麻煩,一般來說專門的FPGA綜合工具能做這種自動轉換。比如 vivado中使用 (* gated_clock = "true" *) input clk_a; 標定受控時鐘,并在腳本加入 -gated_clock_conversion on 綜合選項。

當然如果需要的可控時鐘不太多,也就是少于FPGA中BUFGCE的數量,則可以直接把門控信號加在 BUFGCE的控制端,輸出就是走時鐘網絡的門控信號了。如果FPGA器件中有 BUFHCE,則可以對更多層級的時鐘進行門控,也就可以得到更多的受控時鐘。

有關FPGA門控時鐘的更詳細解釋,可以參照 https://forums.xilinx.com/t5/General-Technical-Discussion/Reg-Clock-gati...

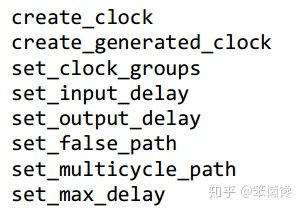

ASIC轉變到FPGA使用的綜合約束,在SDC與XDC基本相容,例如

這些都可以直接使用,當然很多情況下FPGA還是不可能跑到ASIC速度,必須降速運行。另外還需要添加FPGA中對管腳位置,類型,驅動強度等的約束,以及一些綜合選項

以上即為對ASIC代碼更改的主要部分,在下到FPGA板調試前,最好對更改的FPGA代碼進行仿真,確認功能正常,減少上板調試的工作量。

第4步為啟動調試FPGA原型。

在把修改后的FPGA代碼裝入調試前,先需要保證FPGA板本身是正常可用的,這時如果是外購的開發板或者類似haps的驗證系統,則會省去一些麻煩。

如果是頭次開發的FPGA板,則需要先裝入一個最簡單的FPGA鏡像文件,測試一下FPGA的電源供電,下載連接是否可用,然后通過幾個用于測試的FPGA文件,測試下板上與FPGA連接的其他器件是否正常工作。一般頭次設計的板子,多少會有各種問題,比如電源供電問題,管腳連接的差分信號匹配問題,阻抗匹配,電流驅動,信號質量等問題 如果板子通過了以上測試,則可以認為電路硬件設計沒有問題,可以裝入FPGA原形文件進行測試了。

裝入修改了的FPGA原型模擬ASIC,一般不會一次成功,一般出現的問題可以分為以下三類:

1 RTL邏輯錯誤,包括原本ASIC既有的和修改過程引入的錯誤。

2 接口錯誤 與外部器件的電信號連接錯誤,包括電壓不匹配,驅動電流不一致等。

3 軟件錯誤 MCU運行的軟件沒有正確配置相關功能導致,這種一般在仿真中難以發現,因為仿真很少運行真正的軟件系統。

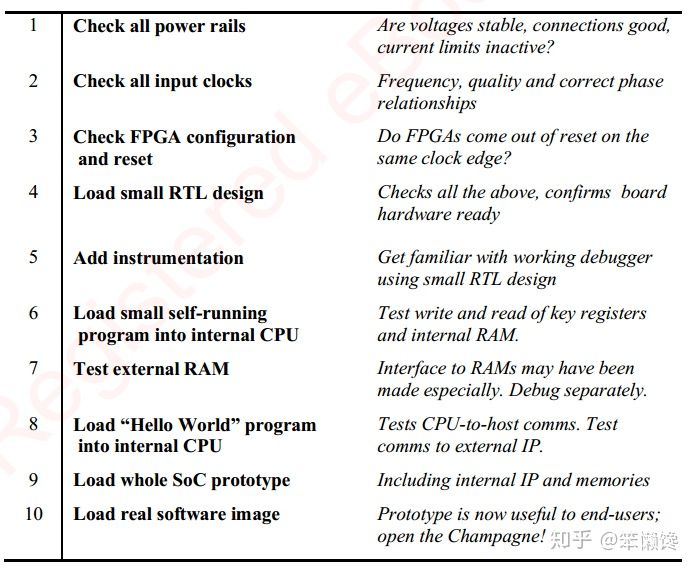

對fpga原型的板上調試,可以歸納為以下步驟。

當載入實際運行的軟件后,通過FPGA原型,就可以如同在實際芯片中一樣,對軟件進行測試修改,同時完成系統級的驗證工作了。也就進入了步驟5.6,這與普通的嵌入式軟件開發大致相同。

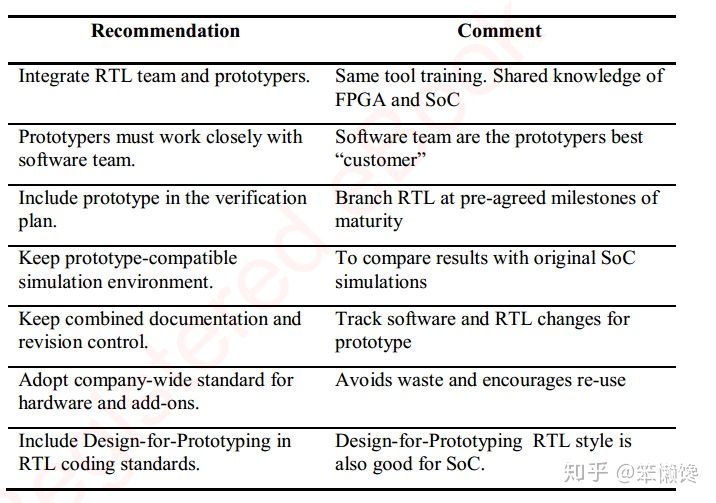

對于通過FPGA進行原型驗證,有以下設計流程上的建議,值得參考

以上參考了xilinx網站內容,以及FPMM等書。

編輯:hfy

-

FPGA

+關注

關注

1645文章

22020瀏覽量

617134 -

asic

+關注

關注

34文章

1245瀏覽量

122235 -

Xilinx

+關注

關注

73文章

2184瀏覽量

124928 -

芯片設計

+關注

關注

15文章

1082瀏覽量

55580

發布評論請先 登錄

西門子桌面級原型驗證系統Veloce proFPGA介紹

超大規模芯片驗證:基于AMD VP1902的S8-100原型驗證系統實測性能翻倍

AMD技術賦能西門子FPGA原型設計解決方案

新思科技推出基于AMD芯片的新一代原型驗證系統

Nordic推出最新物聯網原型驗證平臺Thingy:91 X

芯華章發布新一代FPGA原型驗證系統HuaPro P3

國產EDA公司芯華章科技推出新一代高性能FPGA原型驗證系統

FPGA與ASIC的區別 FPGA性能優化技巧

FPGA和ASIC在大模型推理加速中的應用

數字芯片設計驗證經驗分享文章 實際案例說明用基于FPGA的原型來測試、驗證和確認IP——如何做到魚與熊掌兼

FPGA與ASIC的優缺點比較

解鎖SoC “調試”挑戰,開啟高效原型驗證之路

FPGA算法工程師、邏輯工程師、原型驗證工程師有什么區別?

將ASIC IP核移植到FPGA上——更新概念并推動改變以完成充滿挑戰的任務!

評論