IBIS模型概述

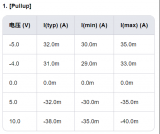

IBIS是一種器件模型標準,允許使用行為模型進行開發,這些行為模型描述了器件內部互聯的信號。IBIS模型保留專用的電路信息,不像SPICE這種結構化模型,IBIS模型是基于測量或電路仿真得到的 V/I曲線數據。

每個IOB標準都有IBIS模型,器件的所有I/O標準的IBIS模型組合在一起便是IBIS文件。IBIS文件還包含器件中所使用的管腳列表,這些管腳連接到配置為支持特定I/O標準的IOB上,該標準會將管腳與特定的IBIS buffer模型關聯在一起。

IBIS標準規定了輸出文件的格式,包括一個文件頭部分和一個組件描述部分。IBIS開源論壇小組開發了Golden Parser這款工具,可以通過檢查IBIS數據格式中的語法來驗證IBIS模型文件。

當使用Vivado IDE導出IBIS模型時,軟件會生成一個.ibs文件,其中包含了:設計使用管腳列表、FPGA內部與管腳連接的信號、與管腳連接的IOB的IBIS buffer模型。

導出IBIS模型

設計者通常都會關心信號完整性問題,比如交叉干擾、地彈、同時轉換噪聲(SSN)。 PCB工程師使用IBIS模型仿真設計,可以更好的在系統級角度了解信號完整性情況。IBIS模型有助于描述電流電壓(I-V)曲線和封裝器件的信息。

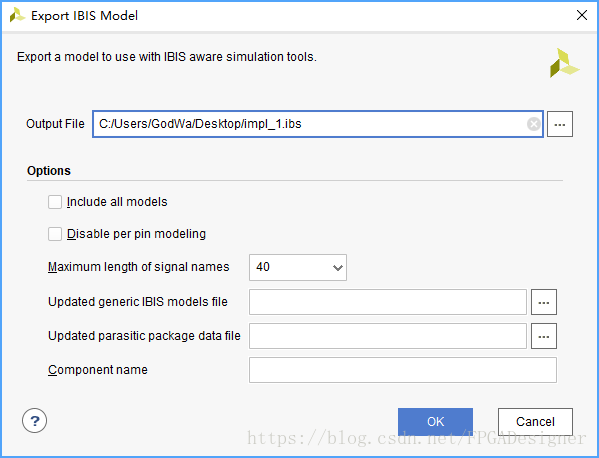

Vivado會使用設計中的網表和實現細節,將這些信息與可用的每個管腳的封裝信息聯合起來,創建一個IBIS模型。打開某一階段的設計,點擊File->Export->Export IBIS Model:

Output File:規定輸出IBIS文件的名稱和路徑;

Include all models:默認情況下,只有設計中用到的buffer模型才會添加到IBIS文件中。選中此選項,會添加FPGA中所有可用的I/O buffer模型;

Disable per pin modeling:禁止包含每一個管腳的封裝模型。勾選此選項,所有管腳的封裝會簡化為單個RLC傳輸線模型,并且在IBIS文件的Package部分中定義;

Maximum length of signal names:會將信號名稱截斷到限制的長度,可以設置為40、20或Unlimited.

Updated generic IBIS model file:可選地提供一個器件的IBIS模型;

Updated parasitic package data file:可選地提供一個用于每個管腳提取的pkg文件。上述兩個文件在Vivado安裝目錄下data/parts目錄中都有,一般只有在該目錄中沒有這些文件的情況下才需要在此處設置。

Component Name:默認名稱為器件的系列,可以在這里設置改變IBIS文件中Component部分的名稱。

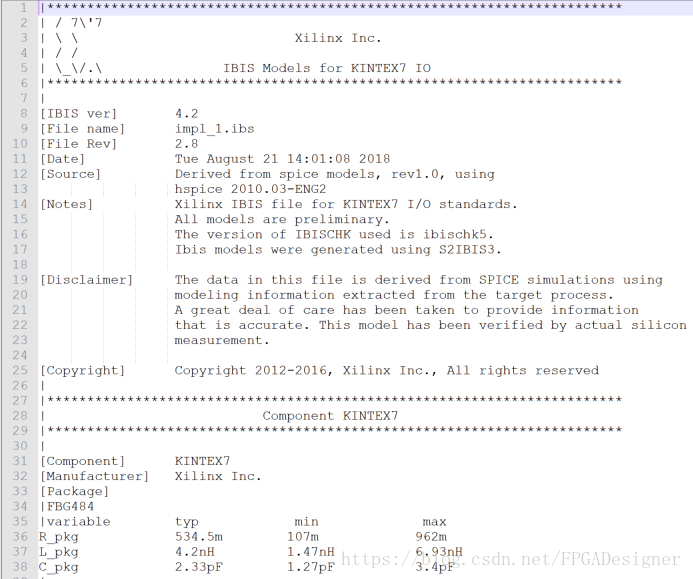

導出的ibs文件可以用文本編輯器打開查看信息,包含文件頭和Component(名稱默認為FPGA系列KINTEX7)兩部分,:

結合本系列第13篇~第16篇,除了IBIS模型外,Vivado還提供了CSV文件、DRC檢查、SSN分析等工具,幫助設計者完成PCB設計。此外,為了在整個PCB環境下更好地優化I/O賦值工作,Xilinx還支持Cadence Allegro FPGA System Planner和Mentor Graphics I/O Designer兩款第三方工具。有機會后面再做介紹。

編輯:hfy

-

PCB設計

+關注

關注

396文章

4800瀏覽量

90279 -

IBIS

+關注

關注

1文章

55瀏覽量

20227

發布評論請先 登錄

如何在Unified IDE中創建視覺庫HLS組件

CYUSB2304的IBIS型號與CYUSB330x IBIS型號相同嗎?

IBIS模型中的Corner參數處理

請問如何獲得AD8000的IBIS模型?

一文詳解Power-Aware IBIS模型

AN-715::走近IBIS模型:什么是IBIS模型?它們是如何生成的?

評論