筆者將從芯片IC的系統設計的角度去詮釋如何掌握體系編程和SOC編程。筆者有超過10年的嵌入式研發經驗,作為架構師多次主導過基于ARM/MIPS/51核的多媒體SOC研發并成功量產案例,希望本系列文章能給嵌入式學習者和從業者有較深刻的指引。

一、體系編程的邊界和范疇

嵌入式開發人員往往從最簡單的51單片機編程開始,然后慢慢會接觸到PIC、AVR、STM32等系列或者型號控制器,還會可能轉向三星S5PV210、Exynos4412等高端處理器編程。

開發人員一般的開發過程都是理解完該型號控制器或者處理器對應的指令集和datasheet,然后通過簡單的例程開始編程,而最普遍的模塊是GPIO、中斷和定時器timer。在接觸到多種類型的處理器編程之后,我們可能會有歸納式的疑問:

在include一個代表該型號IC的register map的頭文件后,某些系列芯片的控制編程可能是完全一樣的,而不同系列芯片的控制編程也是類似,唯一的不同可能在于寄存器命名的不同。這是為什么?

要回答這些問題,我們必須要弄懂體系編程的范疇,明確體系編程的邊界。要深刻地理解體系編程,我們需要從芯片的系統設計的角度去理解芯片的研發構成,可以參考筆者之前撰寫過的《集成電路設計和分工》。

其中有一點非常重要,就是我們要理解CPU核心和SOC的關系。這個世界上有能力研發SOC(System on chip片上系統)的公司很多很多,大到大名鼎鼎的蘋果和三星公司,小到深圳那些籍籍無名但又很賺錢的芯片設計公司都是屬于這個行列。而CPU核呢,放眼世界,能設計CPU知識產權核的就那么幾家,如Intel的X86,ARM公司的ARM核,MIPS公司的MIPS核,51內核也算一個。這里要說明一點,中國沒有,國家雖然重點扶持集成電路,但高層也知道這個砸重金也沒用,實實在在的先把集成電路封裝、工藝等技術發展起來再說。現在的android智能機都是基于ARM核的,想知道ARM之父是誰嗎?前不久大師steve furber在廣東工業大學做了講座:

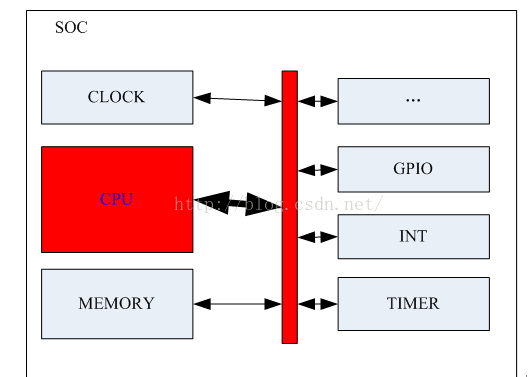

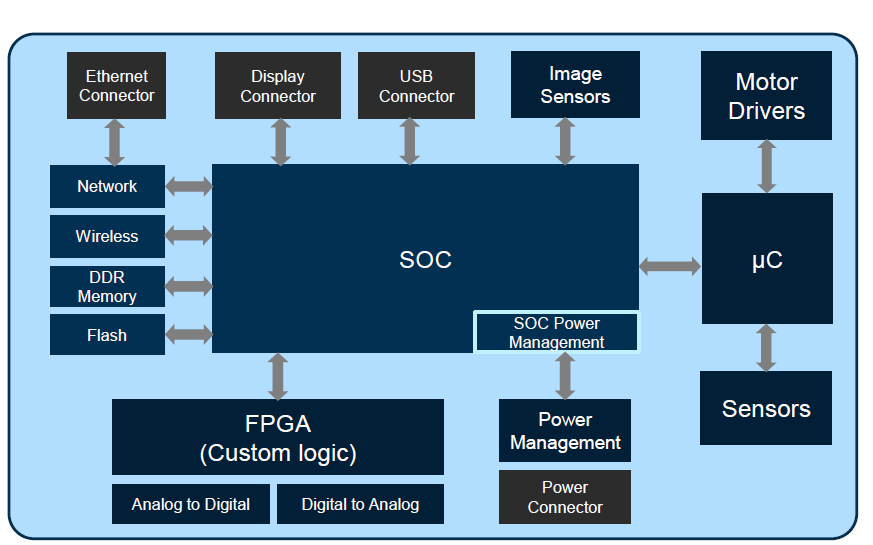

SOC都是根據市場需求和功能定位,在某個類型的CPU核基礎上集成各種通用的外圍模塊控制器,如前面說的GPIO、INT和TIMER,和一些專用的模塊控制器,如TI公司的藍牙單芯片CC2541集成的藍牙基帶和射頻控制器。SOC和CPU核的關系如下圖:

體系編程明顯是針對體系結構的編程,而體系的載體就是CPU。因此,89C51、CC2541等都是51體系編程,而PIC32、ATJ213X都是基于MIPS體系編程,而S5PV210和S3C2440都是ARM體系編程。對同一家CPU核設計公司,它沒有理由將自己的CPU核設計成風格迥異,同一家公司不同的CPU處理器系列應該遵循同一個體系結構。那么,體系結構的范疇是什么?是上圖中紅色的部分,其包括CPU核的設計和總線的時序和控制標準。而CPU核又細分CU(控制單元)和PU(運算單元),CU再分取指、譯碼、訪問寄存器、回寫存儲單元等流水線操作,高級CPU一般還會集成協處理。因此體系架構編程一般包括以下內容:

1)指令集(尋址、運算)、匯編偽指令

2)流水線、指令預取和跳轉規則。在流水線的工作模式下,指令預取當前執行指令的下面N條指令,因此PC和執行地址并不一致,因此假如發生中斷、異常等情況下的返回地址要如何確定。

3)協處理(MMU虛擬內存、cache緩存)

4)寄存器使用和參數傳遞規范(ABI)。其要解決寄存器級如何實現C語言的參數傳遞。請參考筆者之前的博文《C/匯編混合編程接口--MIPS ABI》

5)異常中斷處理(硬件中斷、一般異常、指令陷入中斷等),上圖中的INT管理所有的硬件中斷,如串口、定時器、外部等中斷,并將所有的中斷引腳進行或之后送入CPU的中斷信號。因此,對于CPU來說,當發生中斷時,它并不知道是哪個模塊發生了中斷,只有INT模塊才知道。

6)調試規范

7)總線規范。對于編程人員來說,并不需要太關心總線規范。但它是SOC芯片設計的重要規范。它規定了總線的時序和仲裁的規范以及存儲工作模式(馮諾依曼還是哈佛結構)。

對于一個CPU核設計公司來說,它會給SOC芯片設計公司提供兩樣東西,一是體系設計相關規范,如ARMV7指令集,描述了每一條指令執行的偽代碼過程(這個偽代碼針對的是硬件語言,如HDL);另一樣東西是特定系列CPU的設計規范,以及在該規范下實現的CPU IP核(知識產權核),為RTL寄存器級電路。

那么,對于同一個體系下不同的系列,他們的差異在哪里?

例如,ARM公司現在的發展方向是Cortex A系列主要面向高端消費類電子,如手機平板,Cortex R主要面向軍工、航空等實時要求高的場合,Cortex M系列則是搶占低端控制器市場,如STM32,STM8等。三者的體系都是ARM體系結構,但三者的工藝、功耗、性能并不一樣,而且,CPU核集成的東西是不一樣的,例如M系列并沒有集成cache,相當A系列,M系列的MMU也是一個簡化版。

體系編程是嵌入式架構師和操作系統開發人員需要精通的,對于一般的開發人員比較少接觸到。以上的分析都是基于理論層面的分析。而SOC編程則是面向廣大的普通開發者,將會從系統設計的角度指導大家如何進行SOC編程。

二、SOC編程的范疇和定義

SOC編程是針對片上集成模塊進行寄存器控制編程。在開發實踐中,我們往往把SOC編程和體系編程統稱為體系編程了。沒關系,只要我們理解清楚他們之間的關系就可以了。

那么SOC編程的范疇是什么?

1) 通用控制模塊,如CLOCK、GPIO、INT、TIMER、UART等。

2) 專用控制模塊,如LCD、藍牙、編解碼等。

有些模塊不需要通過引腳連接外圍設備就可以完成功能,如TIMER,大部分模塊需要通過引腳連接外圍設備來完成功能。因此芯片片上集成的是模塊的控制部分,例如LCD控制器,該控制電路實現LCD驅動器(外圍設備)所需要的數據傳輸時序、行信號、列信號和設置接口等。換一個角度說,如果沒有LCD控制器,我們也一樣能夠通過GPIO來模擬出LCD驅動器的時序,但是這樣做,對于普通的開發者來說太復雜,對CPU來說也是一個沉重的負擔。所以系統設計人員會針對LCD驅動器來實現專有的控制電路。

那么對于LCD控制器來說,我們SOC編程來做什么呢?至少,我們需要給LCD控制器一個標識,讓它啟動或者關閉,如何給出這個信號呢?LCD控制器電路無非是一堆的時序電路和邏輯組合電路,啟動和關閉可以用一個信號輸入來表示,而該信號在CPU看來可以映射成一個寄存器的其中一個bit。因此,SOC編程即是針對寄存器編程。對于LCD控制編程,當然不只一個寄存器這么簡單,因為對于一個SOC廠商來說,它希望能兼容市面越多的LCD驅動器,兼容不同的分辨率和圖像深度,因此肯定會有不同的寄存器來進行設置。

從教學的角度來總結,體系編程和SOC編程分為五個層次:

1)體系指令集,如ARM指令集

2)特定系列的CPU規范,如基于ARM體系的CortexA8核

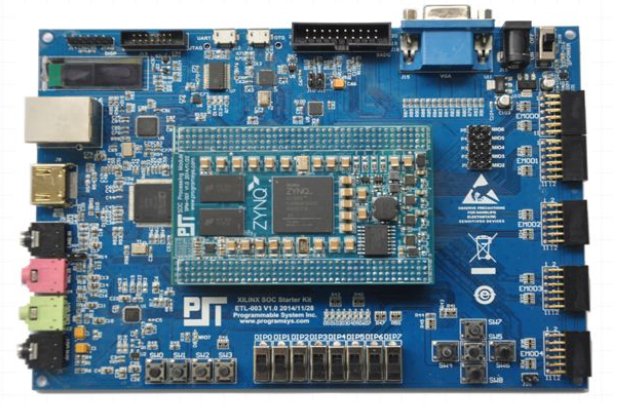

3)SOC級,在CPU核的bus總線基礎上集成clock、timer、interrupt、GPIO等控制器,如三星的S5PV210和TI的OMAP3430都是基于Cortex A8核。

4)板級電路,如開發板、手機主板電路,其電路圖將明確SOC的引腳和外圍設備的連接關系。如GPIO A的第一個引腳接LED0,那要控制LED0就需要對GPIOA0進行控制編程。

5)外圍設備規格,表示板級電路圖上所有外圍設備的規格,如具體LCD SPEC(尺寸、分辨率、延時參數等)。

筆者給SOC編程的過程定義是:基于1)和2)的指令集和CPU總線控制機制,根據具體外圍設備5)的特性參數和4)具體的電路連接關系,對3)SOC對應控制模塊的寄存器進行編程,達到控制、使用的目的。

三、SOC設計和編程

理解SOC系統設計能夠極大地幫助編程,每款SOC的控制例程都是由SOC系統設計人員給出,因為他們也需要通過編程來對SOC芯片進行功能測試和驗證。

另外,我們需要明白的一個觀點是,對于不同的體系來說,同樣的模塊的設計思路是基本一致的,或者可以說,從編程的角度來說,片上集成的模塊的設計控制過程無關于體系結構(兩者有關更多的是在總線控制方面,而這個跟編程人員來說關系不大)。因此基于ARM體系的LCD控制器和基于MIPS體系的LCD控制器,其設計思路都是一致的,不同系統的GPIO控制也是一致的。盡管底層的寄存器電路可能不一樣,但對于上層編程人員看來,兩者是一致的,不同的可能只是寄存器名稱。例如51單片機和arm處理器的GPIO都是輸入寄存器、輸出寄存器、方向寄存器、上下拉寄存器等等。

下面就以CLOCK和GPIO為例說明SOC編程,盡量提取通用的設計和控制過程。

1.最小系統

最小系統除了CPU和RAM之后,還有一個重要的組件就是晶振。SOC或者CPU說到底都是一堆邏輯組合電路和時序電路,時序電路需要時鐘才能正常工作,而晶振就是提供時鐘的,其在上電后不斷地產生時鐘。

2. CLOCK

一般的低端單片機并沒有時鐘控制模塊,其直接利用晶振(如12M或者24M)工作,即CPU的工作頻率就是12M或者24MHz。但是作為一個高級處理器來說,其支持的主頻達到1G或者更高。而市場上并沒有1G的晶振,因此SOC內部必然要實現調頻,PLL鎖相環倍頻技術被廣泛應用在處理器的CLOCK模塊中,其是將晶振的頻率進行倍頻提升。CLOCK模塊除了實現倍頻的控制外,還需要考慮這樣的需求:

1)SOC集成的模塊很多,各種模塊的工作頻率并不盡相同,或者說是在不同的層級,例如CPU和GPU、RAM的工作頻率在G級,LCD的工作頻率則在100M左右,視頻編解碼的工作頻率百M級別,而像GPIO、串口這些模塊的工作頻率可以在10M級別。因此CLOCK還需要進行分頻。所以CLOCK模塊一般的處理方法是將模塊進行分類,并進行一級分頻。例如,S5PV210的CLOCK會將頻率分為三個范圍,M域供給CPU、中斷異常等,D域供給LCD、JPEG、HDMI等,P域供給GPIO、UART等外圍設備。每個域都給定一個頻率(可以通過控制器調節)。

2)對于在同一個域內的模塊,其工作頻率不盡相同,因此允許其內部進行二級分頻。

因此,對于一個高級處理器集成的模塊編程來說,設置好其CLOCK源頻率的相關寄存器是第一步。一般一級分頻由操作系統開發人員設定,二級分頻設置由各模塊的開發人員負責。

3.引腳復用

芯片封裝是芯片成本的重要組成部分,而封裝涉及到引腳復用,而且芯片封裝也涉及到最終產品的BOM成本,因此在系統設計時的引腳復用是一項非常關鍵的技術,可以說SOC集成電路公司的絕密技術。盡可能高效地進行引腳復用非常關鍵。

對于編程人員說,我們要做什么呢?那就是記得每個引腳都可能是功能復用引腳,在使用這個引腳之前,必須設置該引腳的功能。引腳一般默認是GPIO功能,如果我們要使用該引腳進行串口或者LCD等控制線功能,就必須對該引腳對應的功能寄存器進行設置。這是SOC編程的第二步。

CLOCK和引腳功能設置對所有模塊都是適用的。

4.GPIO

這里我們要談通用的模塊GPIO。對于GPIO編程來說,我們應該非常熟悉了,那就是它一定帶有輸入數據寄存器、輸出數據寄存器、輸入輸出高阻態設置寄存器、上下拉設置寄存器。一般的過程是:

1)設置上下拉寄存器

2)設置引腳的方向

3)通過輸入數據寄存器讀入數據或者寫數據到輸出數據寄存器。

記得功能引腳設置也是需要的。有些高級SOC可能還會有驅動能力等級設置寄存器,控制引腳的驅動強度。

5.INT

請參考筆者的博文《軟件和硬件都是對生活的高度抽象---論中斷控制(ARM體系編程)》。

編輯;hfy

-

cpu

+關注

關注

68文章

10854瀏覽量

211583 -

soc

+關注

關注

38文章

4161瀏覽量

218165 -

編程

+關注

關注

88文章

3614瀏覽量

93686 -

GPIO

+關注

關注

16文章

1204瀏覽量

52052

發布評論請先 登錄

相關推薦

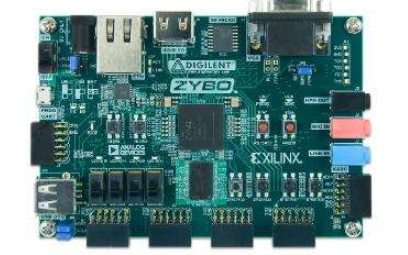

可編程SoC(SoPC),什么是可編程SoC(SoPC)

Mouser備貨Cypress PSoC 4可編程SoC

關于Xilinx發布的全可編程SoC和MPSoC的SDSoC開發環境介紹

Zynq-7000可完全編程SoC設備詳細介紹

Zynq-7000全可編程SoC產品中文簡介資料免費下載

如何掌握體系編程和SOC編程 SOC設計和編程關系

如何掌握體系編程和SOC編程 SOC設計和編程關系

評論