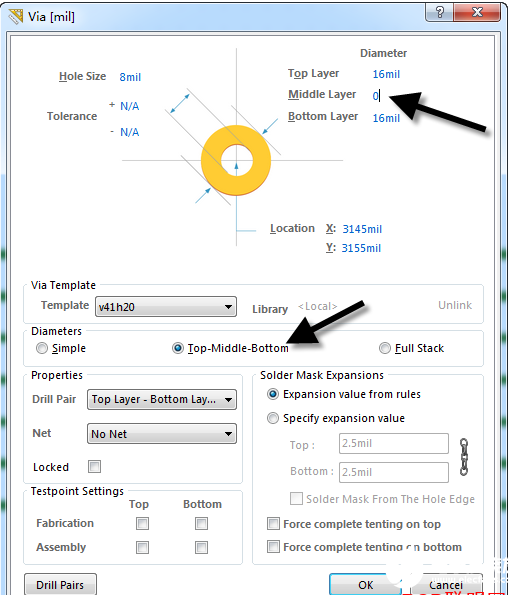

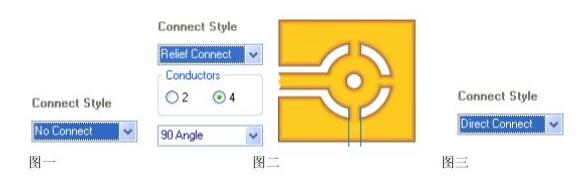

有時候為了增大內層的敷銅面積,特別是BGA區域,尤其在高速串行總線日益廣泛的今天,無論是PCIE、SATA,還是GTX、XAUI、SRIO等串行總線,都需要考慮走線的阻抗連續性及損耗控制,而對于阻抗控制主要是通過減少走線及過孔中的Stub效應對內層過孔進行削盤處理。過孔的削盤處理如圖1所示,雙擊過孔,設置其屬性,選擇“TOP-Middle-Bottom”模式,把內層焊盤的大小設置為“0”即可,多選擇過孔的話可以批量處理。

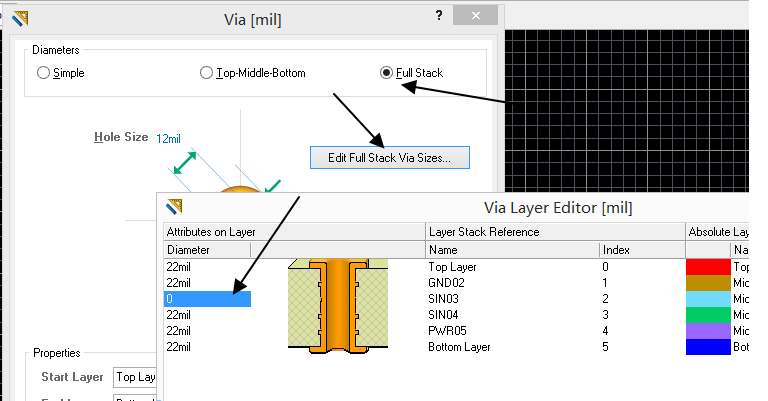

如果是行單獨對某個層進行削盤 可以選擇FUll stack 的選項,想對應的層設置為0mil即可

編輯:hfy

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

pcb

+關注

關注

4322文章

23128瀏覽量

398630 -

BGA

+關注

關注

5文章

546瀏覽量

46929 -

過孔

+關注

關注

2文章

200瀏覽量

21923 -

阻抗控制

+關注

關注

1文章

55瀏覽量

10659

發布評論請先 登錄

相關推薦

PADS過孔:有什么辦法設置使得中間層的keepout只比鉆孔大6mil

請問我在PADS使用使用過孔的時候發現從top連到bottom層的時候(4層的板子),中間的層過孔顯示的外圍的keepout(就是比焊盤大6mil的一圈),但是實際上

發表于 12-08 10:45

pads layout中間層無法鋪銅,請教是怎么回事?

本帖最后由 elec96325 于 2018-1-22 15:47 編輯

4層板,在鋪銅的時候,中間層應該怎么鋪,是跟TOP和BOM層一樣的鋪法嗎?可是為什么我TOP和BOT層可以鋪上,但是

發表于 01-22 14:23

嵌入式系統結構硬件層中間層系統軟件層

層主要包含了嵌入式系統中必要的硬件設備:嵌入式微處理器、存儲器(SDRAM、ROM等),設備IO接口等。中間層中間層為硬件層與系統軟件層之間的部分,有時也稱為**硬件抽象層(Hardware ...

發表于 12-22 08:03

PCB四層板的中間層能走信號線嗎?

PCB四層板中我將中間兩層設置成了信號層,能否給點實用的布線的經驗???當布完線后該怎么進行敷銅呢?需要在哪層進行敷銅,最好是能說說為啥。如果將中間層設置成電源層和地層,那中間層還能走信號線嗎???需要注意些什么???在此謝過。

發表于 04-11 17:33

基于NDIS中間層的包過濾的研究與設計

在分析介紹Windows 2000/xp 平臺的NDIS 驅動程序的基礎上,提出了一種使用NDIS中間層驅動程序實現包過濾的方法。應用該方法能攔截所有進出計算機的網絡數據包、根據應用策略處理

發表于 08-22 09:40

?21次下載

Al合金接觸反應釬焊接頭力學響應及中間層厚度的確定

接觸反應釬焊是目前常用的材料連接方法。為了合理選擇中間層材料的厚度,本文以Si作中間層接觸反應釬焊LF21鋁合金為例,采用有限元(FEM)模擬的辦法,對不同寬度的釬縫對外加拉

發表于 12-26 14:55

?8次下載

Altium-Designer-Duplicate-Net-Names-Wire-XXX解決辦法

Altium-Designer-Duplicate-Net-Names-Wire-XXX-解決辦法

發表于 09-18 16:12

?0次下載

Altium處理過孔中間層削盤的解決辦法

Altium處理過孔中間層削盤的解決辦法

評論