無論是為新IC設計電路,還是為具有分立組件的PCB布局設計電路,設計中的導體組之間都將存在耦合電容。您永遠無法真正消除直流電阻,銅粗糙度,互感和互電容等寄生現象。但是,通過正確的設計選擇,您可以將這些影響減小到不會引起過多串擾或信號失真的程度。

耦合電感很容易發現,因為它以兩種主要方式出現:

兩個不垂直延伸且參考接地平面的網絡可能具有彼此面對的環路(互感)。

提供返回電流路徑的每個平面在其參考網絡中將具有一些耦合電感(自感)。

由于耦合電容無處不在,因此很難確定。每當將導體放置在PCB或IC布局中時,它們都會具有一定的電容。這兩個導體之間的電勢差使它們像典型的電容器一樣進行充電和放電。這會導致位移電流從負載分量轉移出去,并導致信號在高頻下在網之間交叉(即串擾)。

使用正確的電路模擬器工具集,您可以對LTI電路中的耦合電容如何影響時域和頻域中的信號行為進行建模。一旦設計好布局,就可以從阻抗和傳播延遲測量中提取耦合電容。通過比較結果,可以確定是否需要更改布局,以防止網絡之間發生不必要的信號耦合。

電路圖未明確考慮電路中導體之間的任何耦合電容。這是因為耦合電容取決于以下方面:

幾何。導體之間的距離,其橫截面積以及布局中彼此面對的區域的大小將決定電路的電容。

介電常數。分隔導體的電介質具有較高的介電常數,并且耦合電容與介電常數成正比。

寄生之間的耦合。單個導體可以具有多個網絡的耦合電容。這些電容與其他寄生電容和電感結合在一起以產生復雜的耦合,這可能是頻率的復雜函數。

由于耦合可能是頻率的復雜函數,因此返回路徑和串擾信號可能會產生結果,其頻率也與源信號不同。這是由于設計電路,耦合電容和任何其他寄生效應(直流電阻和寄生電感)形成的等效網絡的傳遞函數。

要檢查寄生效應如何影響您的電路板,需要使用布局前和布局后仿真工具。布局前模擬要靈活得多,但是由于尚未創建布局,因此它們不能考慮布局中的幾何形狀。相比之下,正確的數字化布局后仿真工具集將幾乎精確地說明寄生現象,但要查明布局中能產生最強耦合的確切部分卻很困難。此外,如果不更改布局,就無法瀏覽不同的耦合電容或電感值來找到可接受的寄生耦合電平。

耦合電容建模工具

因為直到布局完成,布局中的耦合電容才是未知的,因此開始對耦合電容進行建模的位置在原理圖中。這可以通過在關鍵位置添加一個電容器來建模組件中特定的耦合效應來完成。這允許根據電容器的放置位置對耦合電容進行現象學建模:

輸入/輸出電容。實際電路(IC)中的輸入和輸出引腳會由于引腳和接地層之間的隔離而具有一定的電容。對于小型SMD組件,這些電容值通常約為10 pF。這是在布局前仿真中要檢查的主要點之一。

網之間的電容。在兩個承載輸入信號的網絡之間放置一個電容器將對網絡之間的串擾建模。通過可視化受害者和攻擊者網絡,您可以看到打開攻擊者的方式如何在受害者上引發信號。由于這些電容非常小,并且串擾還取決于互感,因此通常僅在布局后執行串擾仿真才能獲得最高的精度。

將電容走線回到接地層。即使走線很短,它相對于接地層仍將具有寄生電容,這會導致短傳輸線上的諧振。

示例:BJT輸入引腳處的耦合電容

例如,讓我們看一下使用PSpice中的瞬態分析的BJT晶體管的輸入引腳與其參考平面之間的耦合。下圖顯示了一個示例電路,其中包括對短傳輸線上的寄生進行建模的電路。短線上的電感器和電容器(分別為L1和C1)以及電阻器模擬輸出端帶有一定電阻的短傳輸線行為。該系統中的源是范圍為0至5 V的脈沖源,其上升/下降時間為2 ns,重復頻率為100 ns(10 MHz)。晶體管Q1是40237 NPN晶體管。

放置電容器C2以模擬Q1輸入端的pi電容。一個更準確的模型將包括連接到基極的引腳封裝電感,但目前我們將重點放在將電容耦合回接地平面上。

耦合電容仿真示意圖

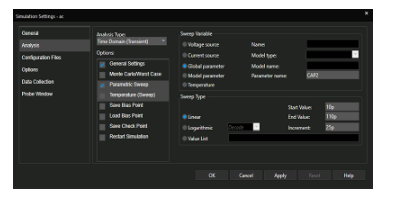

為了檢查輸入耦合電容如何影響信號行為并可能導致失真,將電容器的值定義為全局參數CAP2。這是通過打開組件屬性對話框并將組件值設置為{CAP2}來定義的。需要使用PSpice中“放置零件”菜單中的“ PARAMS”零件將全局參數放置在原理圖上。在下圖中,我為C2 定義了從10到110 pF 的參數掃描范圍(增量為20 pF)。總共給出6條曲線,每個C2值一條。

在PSpice中定義參數掃描范圍

現在已經定義了耦合電容范圍,是時候運行仿真并檢查耦合電容如何影響信號行為了。

時域和頻域結果

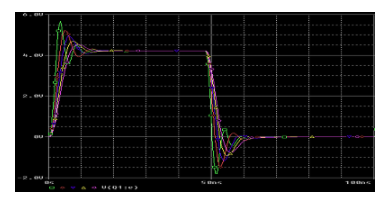

下圖顯示了10 MHz脈沖流中第一個脈沖的發射極電壓的放大圖。由于這條短傳輸線上的共振,我們可以看到明顯的振鈴。當耦合電容較小(綠色曲線,C2 = 10 pF)時,振鈴最大,但隨著耦合電容增加(紫色曲線,C2 = 110 pF),振鈴變小。

參數掃描產生時域

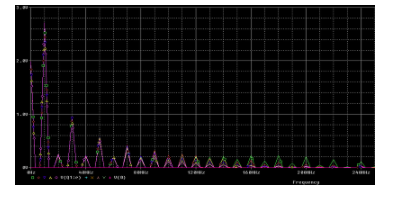

耦合電容的作用是將信號帶寬中的高頻分量作為位移電流分流到地平面。這可以在頻域結果中很好地看到,該結果是通過傅立葉變換計算的。

參數掃描產生頻域

在信號帶寬的高頻端(?120 MHz或更高),當耦合電容較大時,這些頻率的峰值電平會降低。實際上,Q1和C2就像具有高截止頻率的低通濾波器一樣。請注意,這些信號的拐點頻率約為175 MHz,約占總信號功率的75%。我們可以看到,耦合電容開始引起低于該頻率的濾波,從而導致信號失真。

添加源阻抗匹配

盡管隨著耦合電容的增加,振鈴會略有減少,但新型IC往往具有較小的功能,從而具有較小的耦合電容。在這種情況下,這是有問題的,因為瞬態響應導致振幅更大的無阻尼振蕩。這凸顯了該電路設計中源極終端的需求。如果我們將源的輸出阻抗匹配到?50 Ohms,則可以預期瞬態響應具有較低的幅度,并且可能會出現臨界阻尼或過阻尼的振蕩。

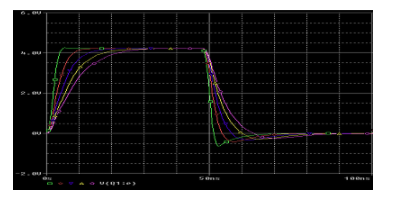

下圖顯示了一個50歐姆電阻與脈沖電壓源(V1)串聯以提供源端接的瞬態分析結果。這顯著抑制了上升沿的振蕩,并使瞬態響應受到嚴重抑制。在下降沿,仍然存在一些下沖。

參數掃描導致時域帶有源終止

根據傳輸線的電路原理,將產生臨界阻尼的源端接電阻是(線路+負載電路)網絡的輸入阻抗的兩倍。端接所需的確切電阻將取決于耦合電容的值。從設計的角度來看,您應該嘗試在布局中找到一個可以容納一定范圍內耦合電容值的源電阻,以幫助抑制由于該電路中的瞬態響應而引起的過沖/下沖。

此設計中耦合電容可能突出的其他地方包括:

脈沖驅動器的輸出(接地)。

晶體管的輸出(接地)。

在晶體管輸出和電源引腳之間。

上面的前兩點結合起來可以增加互連的電容,從而稍微降低其阻抗。根據電路理論,這與增加晶體管的輸入電容時一樣,使瞬態響應更接近臨界阻尼或更深,成為過度阻尼。在長傳輸線上,需要將負載阻抗與線路阻抗分開考慮,并且我們需要查看電路反射以確定耦合電容引起的信號行為。

編輯:hfy

-

電容器

+關注

關注

64文章

6217瀏覽量

99540 -

電感器

+關注

關注

20文章

2329瀏覽量

70508 -

IC設計

+關注

關注

38文章

1295瀏覽量

103918 -

耦合電容

+關注

關注

2文章

154瀏覽量

19811 -

電路模擬器

+關注

關注

3文章

12瀏覽量

11570

發布評論請先 登錄

相關推薦

PCB布局設計電路中的耦合電容解析

PCB布局設計電路中的耦合電容解析

評論