承前:討論濾波電容的位置與PDN阻抗的關系,提出“全局電容”與“局部電容”的概念。能看到當電容呈現“全局特性”的時候,電容的位置其實沒有想象中那么重要。

本節:多層板設計的時候,電容傾向于呈現“全局特性”,“電源加磁珠”的設計方法,會影響電容在全局范圍內起作用。同時電源種類太多,還會帶來其他設計問題。

通過上一篇文章,我們知道電容在不同的使用條件,會呈現“全局特性”與“局部特性”。

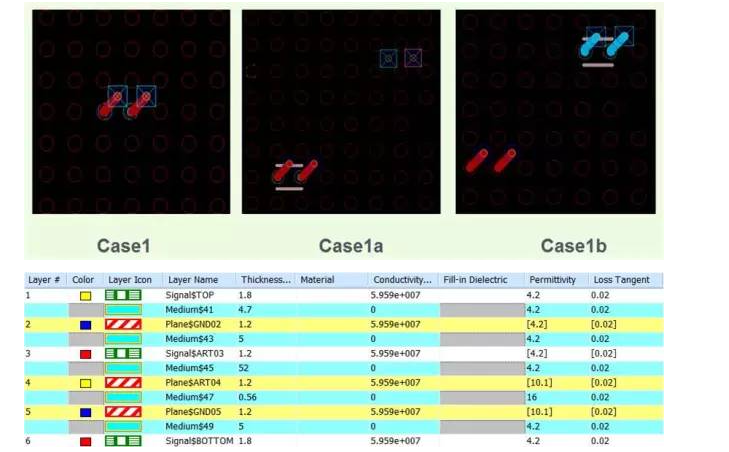

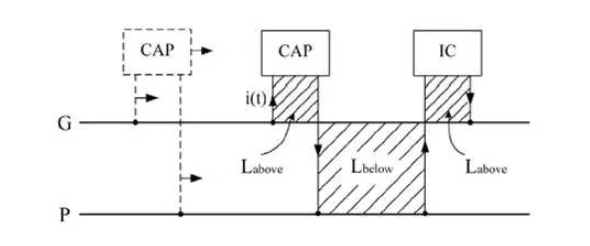

避免研究公式的繁瑣,我們來看看實際仿真結果。為了便于研究,設計了一個仿真案例,如圖1所示:Case1是電容放在芯片管腳附近,Case1b是電容遠離芯片管腳放置。這時候Case1b比Case1多出一對電源地過孔,為了同等條件下只比較電容的位置影響,我們增加Case1a案例,在和Case1b電容Fan out同樣的位置上增加一對電源地過孔。

圖1

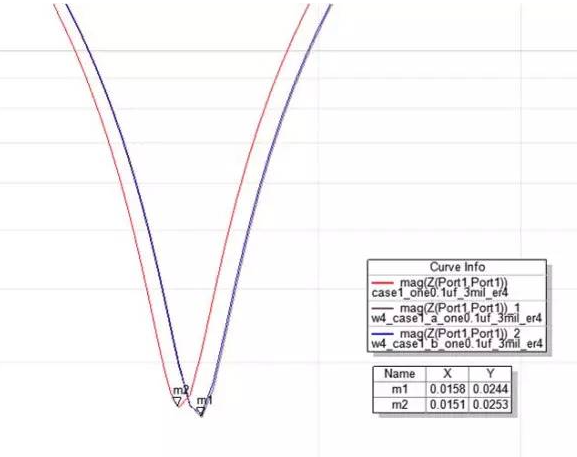

圖1的4、5兩層為電源地耦合的平面。先來看看電源地距離為3mil時的情況:當電源地緊耦合時,a和b兩個Case的PDN曲線基本重合,說明電容的諧振頻率沒有變化。也就是說,電容位置好像幾乎沒有任何影響,反而是Case1的諧振頻率偏向于低頻,說明Case1的安裝電感反而更大一些。這個容易理解,主要是多出來的一對電源地過孔導致的。

圖2

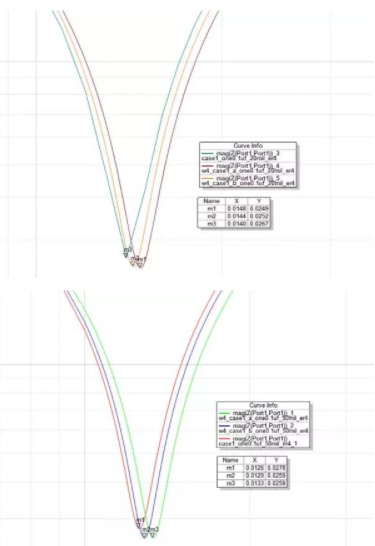

電源地距離在10mil以內時,以上結論都類似。但是當電源地距離在20mil甚至50mil時,情況稍有變化。如圖3所示,電源地距離變大時,a和b兩個Case的PDN曲線開始偏離,Case1b的諧振頻率向低頻偏移,說明電容遠離芯片管腳的時候,電容的安裝電感明顯變大。

圖3

所以,我們可以得出簡單的結論:

典型的8層以上單板,或者6層板采用3個電源地平面,電源地相對緊耦合的設計,這時候板上的濾波電容呈現“全局特性”,也就是說電容的位置不是很“重要”,電容在全局起作用。雙面板四層板,以及6層板電源地距離比較遠,相對松耦合的時候,板上的濾波電容傾向于“局部特性”,電容的位置比較重要,最好能靠近芯片管腳放置。

當電源供電網絡不使用電源地平面來設計的時候,電容更傾向于“局部特性”。如PLL電源的電容,如DDR3設計中Vref電源的電容,都希望嚴格把相應的電容靠近芯片的管腳,甚至最好能做到設計時指定電源必須從濾波電容進入芯片管腳。

同樣的,對于常規數字電源,如3.3V,2.5V等IO電源,如果我們對每一個芯片都使用磁珠隔離之后單獨供電,那么電容就失去了“全局”作用。最直接的一個負面作用就是導致設計需要增加更多的濾波電容。或者某個芯片的電容數量與種類不夠,導致電源軌道噪聲變大。

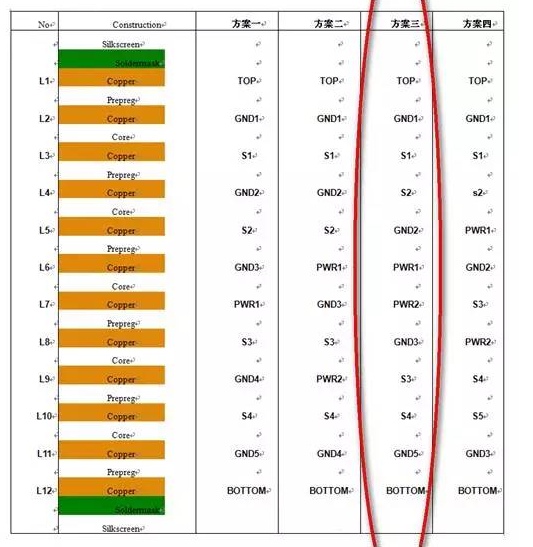

就算是電容的數量不是問題,電源噪聲可控,“濫用”磁珠還會造成其他設計問題。圖4中的方案三是現在非常流行的12層板層疊設計。大家選擇這樣的層疊最主要的原因就是電源的分割太破碎,這樣的電源層如果作為參考平面的話,會比較難避免“跨分割”問題(單面跨電源分割問題,我們會另外有專題討論)。方案三的層疊避免了電源分割多的問題,卻帶來更加惡劣的層間串擾等其他問題。

電源種類多是設計的現狀,“濫用”磁珠會“雪上加霜”的讓電源種類更多。加大電源地平面設計的難度。而增加的磁珠,其實并沒有給電源噪聲帶來好處。

圖4

總結:常規的數字電源,在采用多層板設計,電源地平面緊耦合的情況下,不建議“濫用”磁珠,保持電容的“全局”特性起作用。

需要使用磁珠的場合大致分為兩種

1、“特別”保護自己,如PLL電源等

2、“關愛”他人,自身的干擾性比較強,避免EMI問題,如強驅動的時鐘芯片等

每次一個話題結束的時候,總覺得沒什么問題可以問,因為覺得都講清楚了。不過每次編輯都會強調“你的問題”呢?那就找一個問題,作為下一個話題的鋪墊吧!

作者:吳均 一博科技高速先生團隊隊長

編輯:hfy

-

pcb

+關注

關注

4319文章

23080瀏覽量

397518 -

數字電源

+關注

關注

28文章

513瀏覽量

109299 -

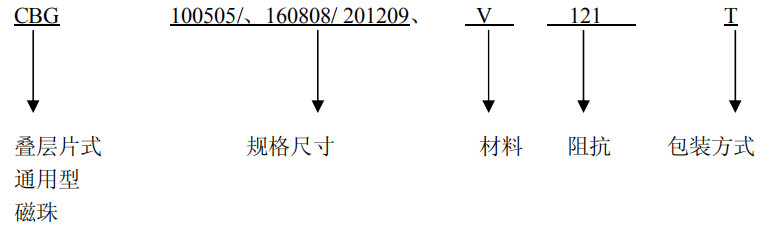

磁珠

+關注

關注

6文章

266瀏覽量

44157

發布評論請先 登錄

相關推薦

PCB設計的磁珠選用技巧

PCB設計正確使用磁珠

PCB設計磁珠的選用你真會嗎?

PCB設計之磁珠的使用

PCB電路設計中磁珠的選用技巧

磁珠對電源紋波可能會存在的影響?

如何在PCB板設計時正確的選擇磁珠

加磁珠使電源紋波會變大嗎

電源系統中鐵氧體磁珠使用

PCB設計:“電源加磁珠”的設計方法

PCB設計:“電源加磁珠”的設計方法

評論