低電平組件需要超穩定的電源,而高速數字信號則需要具有可重復的邊沿轉換時間。數字信號的兩個方面是相關的,您需要抑制電源噪聲的所有方面以減少數字系統中的抖動。在設計調試期間,如果要隔離和消除電源噪聲源,則需要在整個電路板上收集測量結果。這是您如何隔離直流線上會引起抖動的確定性強噪聲源的方法。

電源噪聲和抖動源

如果您曾經覆蓋過數字信號的時域軌跡,那么您就對抖動很熟悉。該術語(有時與相位噪聲互換使用)是指數字信號的邊沿觸發和通過邏輯電路的傳播延遲中的波動。抖動與電源噪聲密切相關,在電源噪聲中,直流電源電平的波動會導致數字信號延遲觸發或延遲觸發。下表顯示了一般半導體器件和PCB中電源噪聲的主要來源。

| 噪聲源 | 噪聲類型 | 描述 |

| 開關噪聲 | 周期 | 產生于開關調節器中的開關元件 |

| 高斯噪聲 | 隨機 | 由電容電阻能級的熱波動引起,這通常不是電子設備中考慮的比較大噪聲源 |

| 1/f噪聲 | 隨機 | 這主要于你的元件中的半導體晶格缺陷有關,盡管沒有1/f噪聲的單一來源 |

| 漂移 | 偽隨機 | 這是局限在低頻率,頻率成分可以隨時間變化 |

| 瞬態響應確定性 | 確定的 | 當一個系統有多個時鐘時,這通常看起來是隨機的,但是通過一些分析,你可以確定哪些組件是這種噪聲的主要驅動因素 |

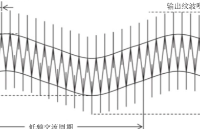

該表中的最后一項是最值得關注的一項,因為它對抖動的影響很大。PDN設計和分析中經常提到?1 ps / mV的抖動靈敏度值。對于具有高電源電平和低上升時間(例如分別為3.3 V和?1 ns)的器件,紋波引起的抖動可能僅在5%紋波時不會上升到15%以上。但是,隨著組件變得越來越小以及開關速率增加,抖動和電源電壓紋波的容差也越來越嚴格。

降低抖動需要在兩個方面抑制電源噪聲的影響:

在PDN上:您需要將PDN設計為低紋波,以防止強烈的抖動。如果您可以降低到幾mV RMS紋波電壓,那么您的PDN設計就做得很好。

時鐘抖動:所有時鐘對各種噪聲源都有自己的敏感性,這會影響時鐘信號輸出的抖動。PDN應該設計為始終具有低紋波,但是時鐘信號中的抖動仍會在組件的輸出上產生抖動。這是由于在其他組件中鎖存和觸發位轉換時出錯。

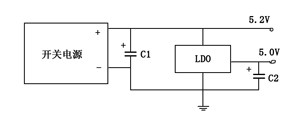

當您擁有多個系統時鐘時,最后一點將變得更加困難,并且您需要確定對抖動影響比較大的時鐘。對于系統時鐘,或來自單個源的多條時鐘線,您可能可以查明特定組件的抖動源。通常,多個時鐘將導致PDN上的瞬態紋波,然后造成系統中其他位置的抖動。自然抖動也有一個下限,與瞬態紋波無關。這只能通過使用PLL鎖定到更穩定的參考振蕩器來清除。最后,一個PDN部分(例如5 V)上的噪聲可能會在另一PDN部分(例如3.3 V)上產生噪聲。

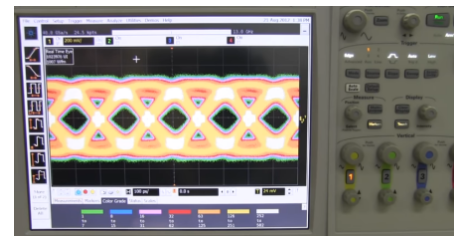

如果可以測量抖動和電源噪聲,則可以確定對組件中的抖動影響比較大的噪聲源。您需要的主要工具是可以收集眼圖的高帶寬示波器。

如何測量由于電源噪聲和紋波引起的抖動

對于某些示波器來說,測量抖動非常困難,因為它在觀察波形時依賴于邊沿觸發。從視覺上看,在觀察示波器跡線時抖動并不明顯,確定抖動可能需要手動平移并疊加多個信號跡線,以量化抖動。這就是為什么量化電源噪聲及其抖動的標準方法是使用高質量的示波器收集眼圖的原因。

眼圖測量顯示抖動和電平變化

收集了特定組件的眼圖后,您可以將其與時域中PDN上紋波的直接測量值進行比較。應當在多種情況下執行此操作,因為瞬態紋波導致的電源噪聲不會增加。在這種情況下,PDN電壓波動被表示為正交相加的復數。

對于示波器對PDN紋波的任何測量,請使用衰減系數盡可能低的探頭,因為這將防止探頭夸大您測得的電源噪聲。此外,請注意示波器的帶寬。PDN上的瞬變可以具有高達?1 GHz的頻率分量。僅使用需要收集準確測量值的帶寬,因為這將使您看到PDN紋波中所有可能的毛刺。

您可能希望從時域PDN紋波測量中看到FFT結果。強大的高頻噪聲源對背景噪聲非常明顯

進行時域測量后,如果有多個有源組件,您將無法查看哪個開關組件或時鐘是造成紋波的主要因素。而是將數據帶入頻域。功率譜中的任何強峰值將對應于某些組件或時鐘在指定頻率下的切換。然后,您可以采取措施減少所標識組件產生的紋波,例如添加去耦/旁路電容器或確保相關PDN上的更大的平面間電容。

編輯:hfy

-

示波器

+關注

關注

113文章

6240瀏覽量

184799 -

數字信號

+關注

關注

2文章

969瀏覽量

47539 -

電源噪聲

+關注

關注

3文章

151瀏覽量

17474 -

PDN

+關注

關注

0文章

83瀏覽量

22703

發布評論請先 登錄

相關推薦

為什么不同示波器的紋波噪聲測量結果總是不同

如何測量由于電源噪聲和紋波引起的抖動

如何測量由于電源噪聲和紋波引起的抖動

評論