1.關于等長

第一次聽到“繞等長工程師”這個稱號的時候,我和我的小伙伴們都驚呆了。每次在研討會提起這個名詞,很多人也都是會心一笑。

不知道從什么時候起,繞等長成了一種時尚,也成了PCB設計工程師心中揮不去的痛。需要等長設計的總線越來越多,等長的規則越來越嚴格。5mil已經不能滿足大家的目標了,精益求精的工程師們開始挑戰1mil,0.5mil……還聽過100%等長,沒有誤差的要求。

為什么我們這么喜歡等長?打開PCB設計文件,如果沒有看到精心設計的等長線,大家心中第一反應應該是鄙視,居然連等長都沒做。也有過在賽格買主板或者顯卡的經驗,拿起板子先看看電容的設計,然后再看看繞線,如果沒有繞線或者繞線設計不美觀,直接就Pass換另一個牌子。或許在我們的心中,等長做的好,是優秀PCB設計的一個體現。

做過一個非正規的統計(不過一博每年上萬款PCB設計,我們的采樣基本上也可以算做大數據了),稍微復雜一點的高速板子,繞等長要占據總設計時間的20%~30%。如果等長規則更嚴格,或者流程控制不好,做了等長之后再反復修改,這個時間還會更多。

2.那些年,我們一起繞過的等長

培訓的時候,我們經常會玩一個游戲,游戲的名字叫做:那些年,我們一起繞過的等長……

說到等長要求,先說說什么是“裕量”哈。“裕量”是設計時保留的安全間距,百度百科的解釋更簡單:多出來一部分,就稱之為裕量。到底要多多少,什么才是安全,那就見仁見智了。每個人的安全感不同,對“裕量”的定義就不一樣。但是在時序設計的時候,有一個現象比較普遍,那就是裕量層層放大,比如產品經理可能要求等長范圍是±100mil,項目經理可能就會更嚴格到±50mil,然后到具體的實施工程師,可能就變成±5mil了。碰到一些“安全感”不足的工程師,那就恨不得是完全等長,沒有偏差。

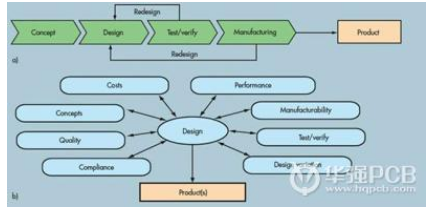

所以,后面的討論里面,我們不會太多糾結在等長到底是10mil還是±5mil,我們集中精力來看看哪些等長是沒有必要的,哪些等長反而破壞了系統的時序設計要求。

編輯:hfy

-

工程師

+關注

關注

59文章

1569瀏覽量

68504 -

PCB設計

+關注

關注

394文章

4683瀏覽量

85548

發布評論請先 登錄

相關推薦

PCB設計工程師福利來咯~

有沒有在海口的PCB設計工程師

誠聘PCB設計工程師

工程師需要掌握的PCB布線技巧

電子工程師高端PCB設計工具:20種完全免費的PCB設計必備工具

pcb設計工程師必須了解SMT術語

PCB設計工程師必須掌握的PCB制造知識

電路設計工程師與PCB設計工程師在進行技術評估時應考慮哪些問題

PCB設計:如何繞等長?資料下載

PCB設計:為什么要繞等長?資料下載

PCB設計工程師淺談繞等長的概念

PCB設計工程師淺談繞等長的概念

評論