從去耦半徑出發,通過去耦半徑的計算,讓大家直觀的看到我們常見的電容的“有效范圍”問題。

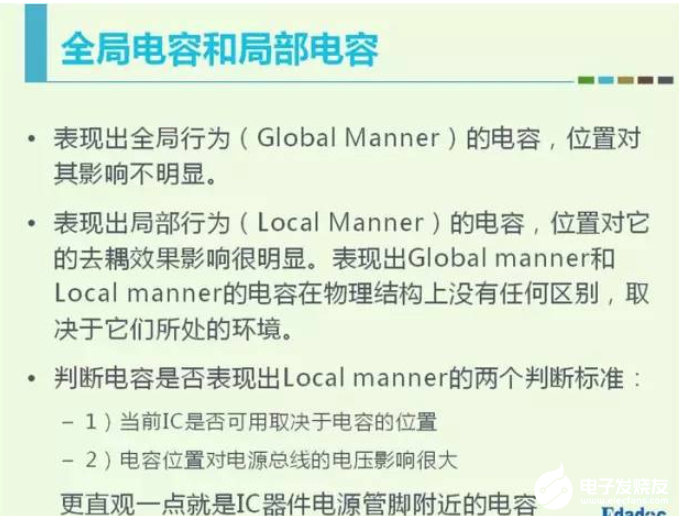

本節:討論濾波電容的位置與PDN阻抗的關系,提出“全局電容”與“局部電容”的概念。能看到當電容呈現“全局特性”的時候,電容的位置其實沒有想象中那么重要。

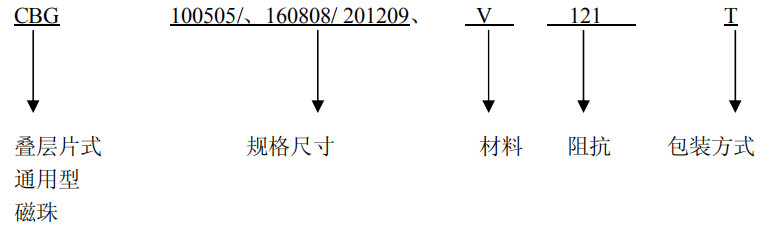

啟后:多層板設計的時候,電容傾向于呈現“全局特性”,“電源加磁珠”的設計方法,會影響電容在全局范圍內起作用。同時電源種類太多,還會帶來其他設計問題。

通過上一篇文章,我們知道平常“耳熟能詳”的電容去耦半徑理論,對PCB設計其實沒有什么指導意義。0.1uf的電容去耦半徑足夠大,設計中參考這個值沒有用處,工程師還是會“盡量”把0.1uf電容靠近芯片的電源管教放置。PCB設計師需要更有效的理論來指導電容的布局設計。

既然簡單的用四分之一波長理論推算的電容去耦半徑不起作用,那么電容放置得離芯片電源管腳比較遠,還會有哪些影響呢?很多人都答對了,影響安裝電感。

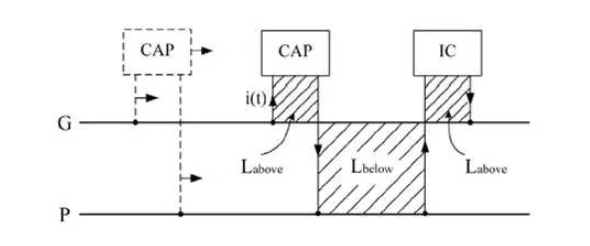

在上一個專題的第四篇文章里面,已經討論過電容安裝電感的估算。這一次,我們來更詳細的看看安裝電感。從圖1能看到,安裝電感可以簡單分為L above和 L below。

圖1

在這里引入兩個概念:Labove 、Lbelow (電容和IC下面的電流回路大小不一定一樣,但在這里分析的時候,假定大小等同)

總電感:LTotal= 2Labove+Lbelow

Labove包括電容的ESL和Fan out帶來的電感,我們會另外專題討論電容的Fan out問題。至于L below就更多收到電容位置的影響。簡單來說,電容離芯片電源管腳越遠,L below圍成的面積就越大,相應的安裝電感就越大。

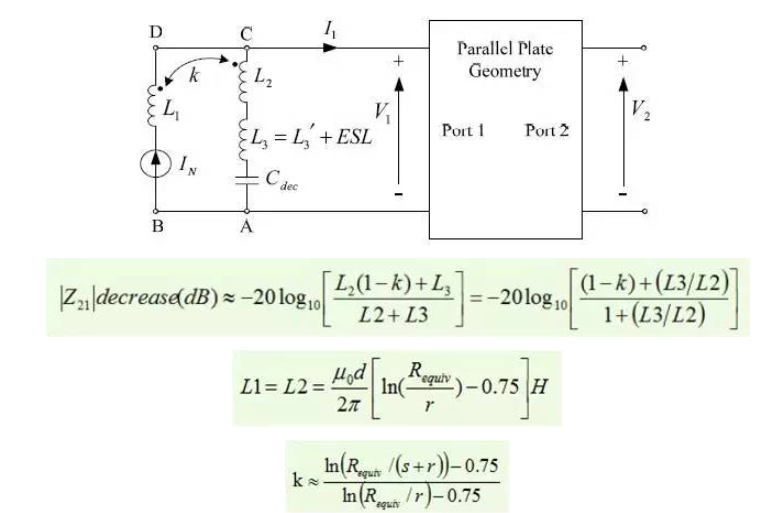

更具體點,Lbelow主要是兩個過孔的自感和互感,當電容的位置離IC器件更近時,如圖2所示,Lbelow的互感增大,因互感的作用與自感的作用相反,導致其整體電感減小,充放電速率更快

圖2

可以列出一堆公式來推導這個互感乃至L below,但這個不是高速先生的風格。

其實從圖1可以簡單看出,G和P之間的距離對L below影響很大,G和P之間的距離越近,L below對應的陰影區域面積就越小。而L below越小,也就意味這電容可以放得越遠,換句話說,電容的有效濾波范圍更大。電容也就更加傾向于呈現“全局”特性。

下一節我們還會通過一個直觀的仿真,讓大家看到平面距離與安裝電感的關系,以及為什么說在新的設計條件下,電容會呈現全局特性。

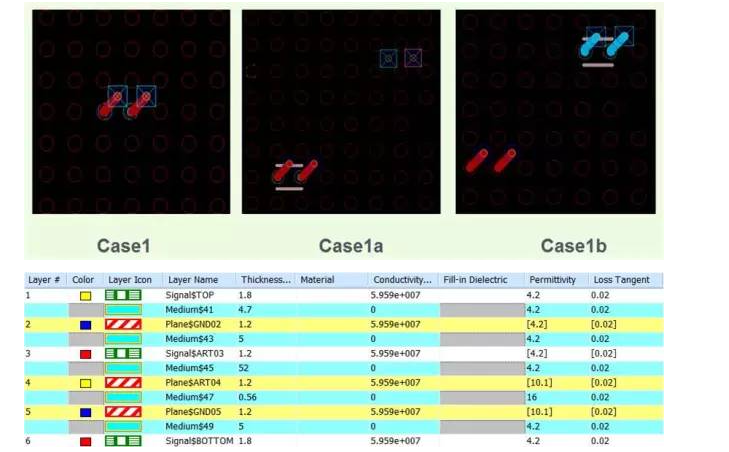

圖3是一個簡單的總結,更具體的分析,請聽下回分解。

圖3

編輯:hfy

-

濾波電容

+關注

關注

8文章

459瀏覽量

40968 -

PCB設計

+關注

關注

396文章

4789瀏覽量

89508 -

電容去耦

+關注

關注

0文章

4瀏覽量

5105

發布評論請先 登錄

評論