賽靈思為 FPGA 和 MPSoC 器件中所有受支持的 I/O 標(biāo)準(zhǔn)提供了 I/O 緩存信息規(guī)范 (I/O Buffer Information Specification, IBIS) 模型。

本篇博文旨在提供有關(guān)如何為可編程邏輯 (PL) 和處理器系統(tǒng) (PS) 多用途 I/O (MIO) 進(jìn)行 IBIS 模型名稱解碼的指導(dǎo)信息。 本文主要分 3 個部分:

PL I/O 標(biāo)準(zhǔn)

PS MIO 標(biāo)準(zhǔn)

PS DDR I/O 標(biāo)準(zhǔn)

在這 3 個章節(jié)中包含多個解碼器表格,其中逐一細(xì)分羅列了模型名稱的每個部分并提供了一些模型名稱示例。

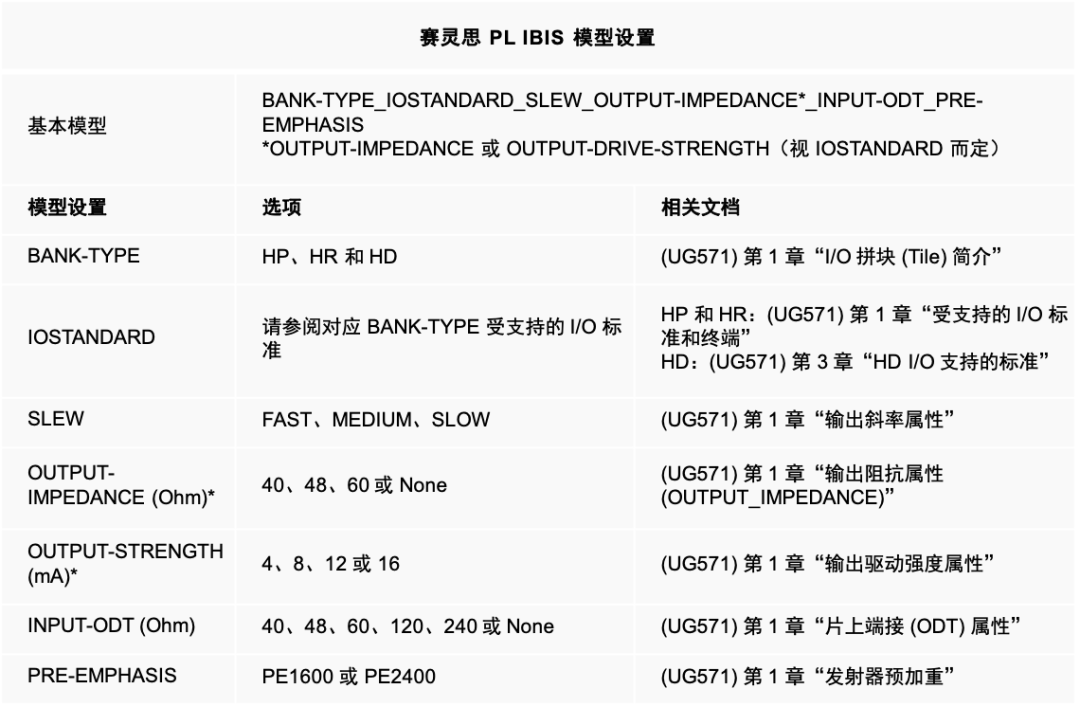

1. 賽靈思 PL I/O 標(biāo)準(zhǔn) IBIS 解碼器

PL IBIS 解碼器可用于為所有可編程邏輯 I/O 執(zhí)行 PL IBIS 模型解碼。 它適用于 Zynq MPSoC PL I/O。

表 1:PL IBIS 解碼器

所有模型(LVDS 除外*)都將包含“bank 類型 (Bank Type)”、“I/O 標(biāo)準(zhǔn) (IOStandard)”、“斜率 (Slew Rate)”和“輸出阻抗/驅(qū)動強(qiáng)度 (Output Impedance/DriveStrength)”。

*LVDS 模型將包含“bank 類型 (Bank Type)”、“LVDS”、“I/O 標(biāo)準(zhǔn) (IOStandard)”和“數(shù)字端接 (Digital Termination)”。

內(nèi)部 100-ohm 差分終端僅在以 1.8V (LVDS) 或 2.5V (LVDS_25) 加電的 bank 中可用。 請參閱(UG571) v1.12 第 103 頁以獲取詳細(xì)信息。

https://china.xilinx.com/support/documentation/user_guides/c_ug571-ultrascale-selectio.pdf

注:并非每個 IBIS 模型都包含所有模型設(shè)置。

如果模型名稱中不含某項設(shè)置,即表示此模型不支持該項設(shè)置。

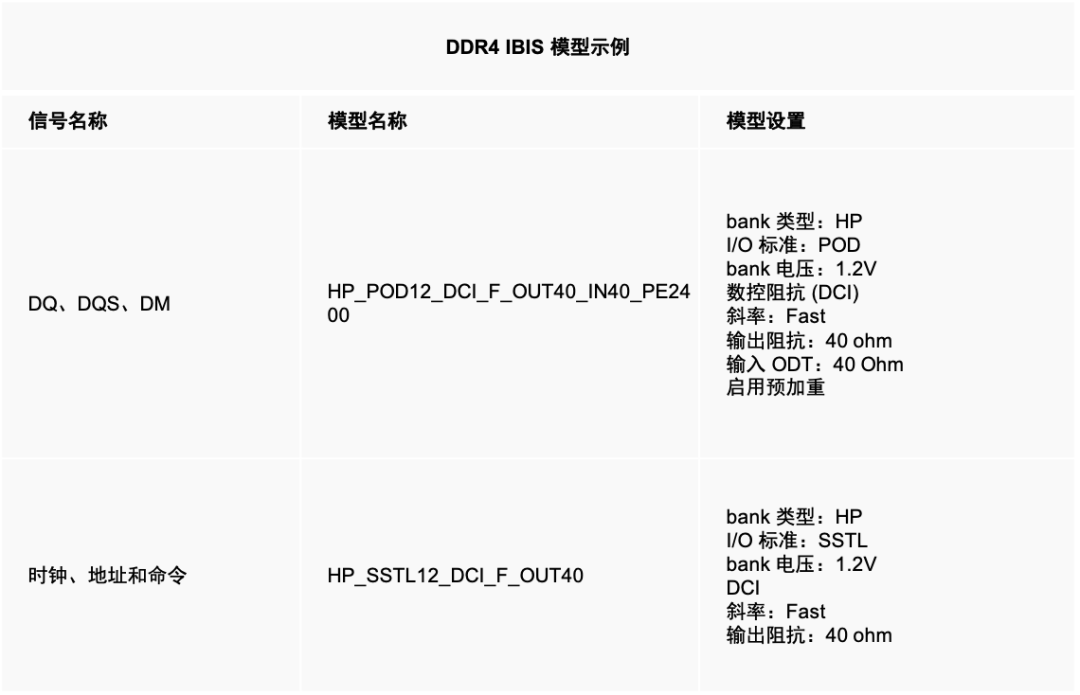

表 2 和表 3 提供了適用于 DDR4 和 SelectIO 的 PL IBIS 模型示例。

表2:PL DDR4 IBIS 模型

差分信號在 IBIS 文件中的“[Diff Pin]”關(guān)鍵字下指定。

表 3:PL SelectIO IBIS 模型

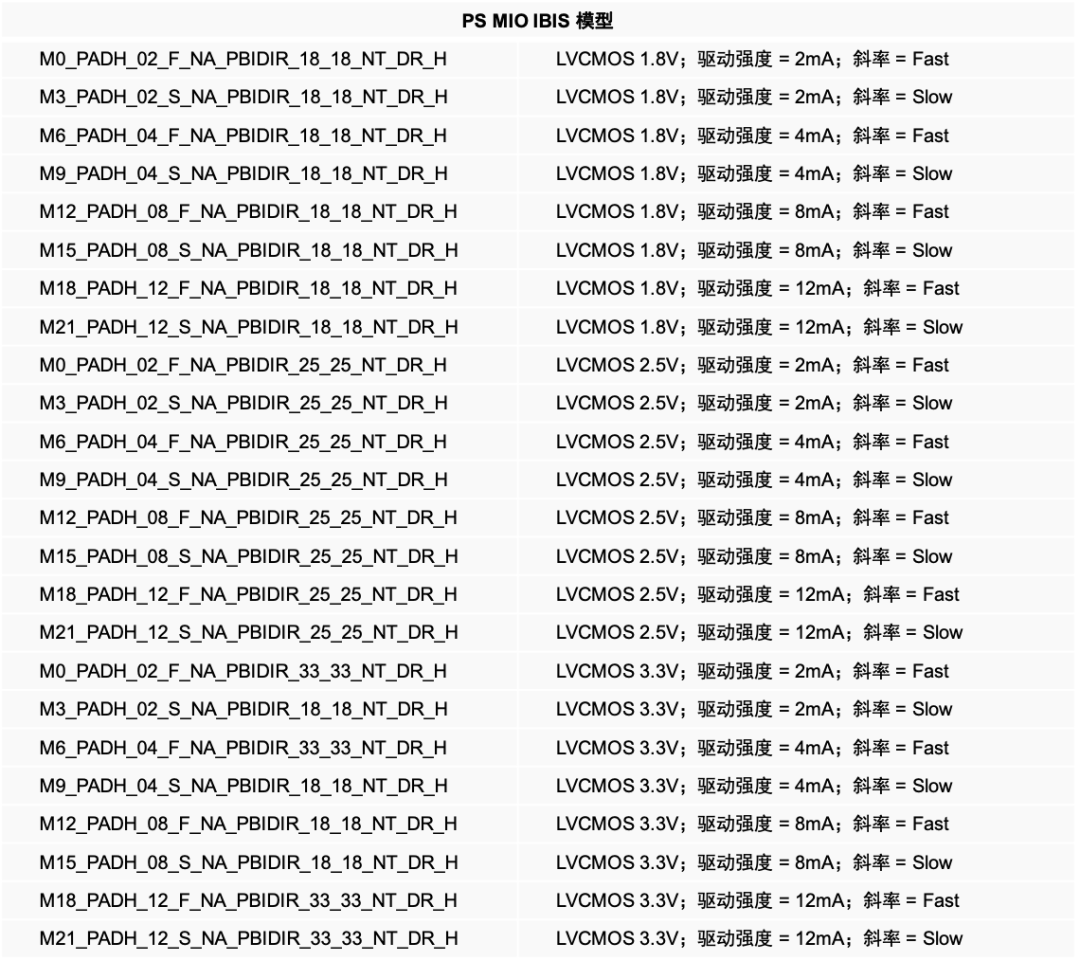

2. 賽靈思 Zynq MPSoC PS MIO IBIS 模型

Zynq MPSoC MIO 管腳支持 LVCMOS,可提供以下選項

接口電壓:1.8V、2.5V 或 3.3V

驅(qū)動強(qiáng)度:2mA、4mA、8mA 或 12mA

斜率:Slow 或 Fast

MIO IBIS 模型格式為M0_PADH_02_F_NA_PBIDIR_18_18_NT_DR_H。

表 4 對每個 IBIS 模型的驅(qū)動設(shè)置進(jìn)行了解釋。

表 4:PS MIO IBIS 模型

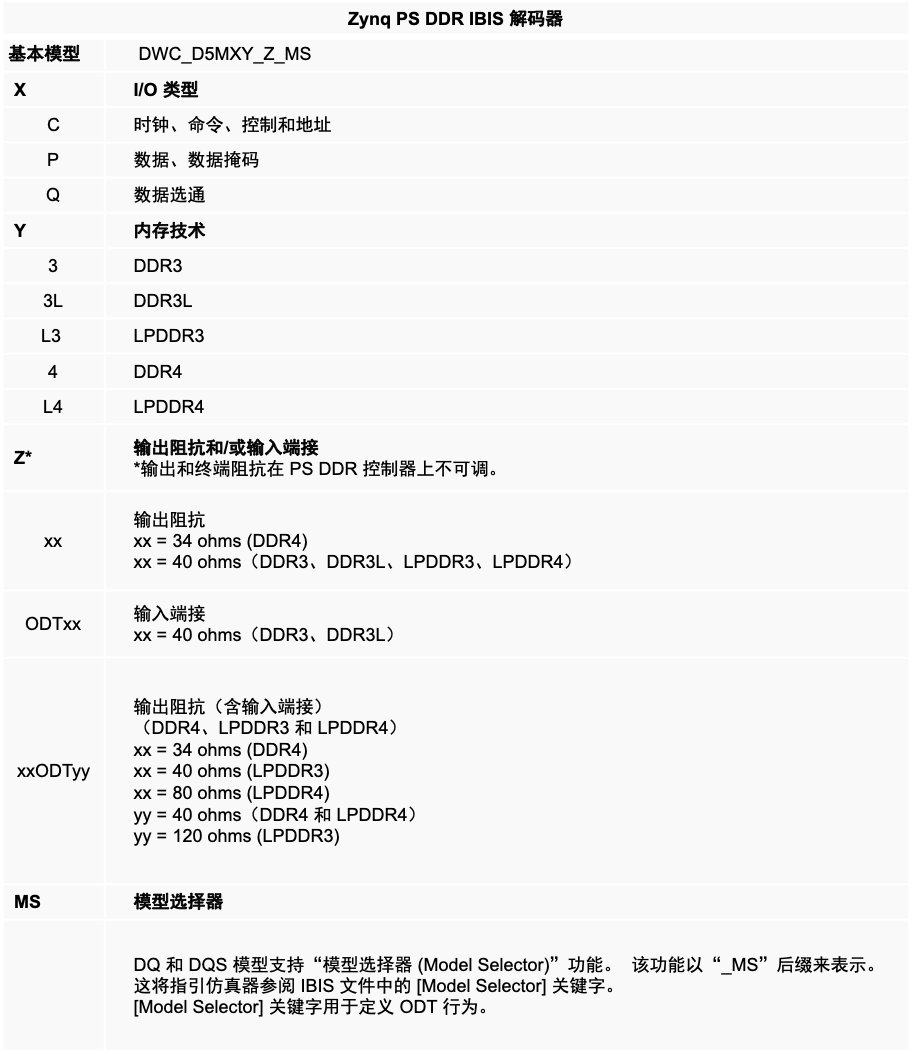

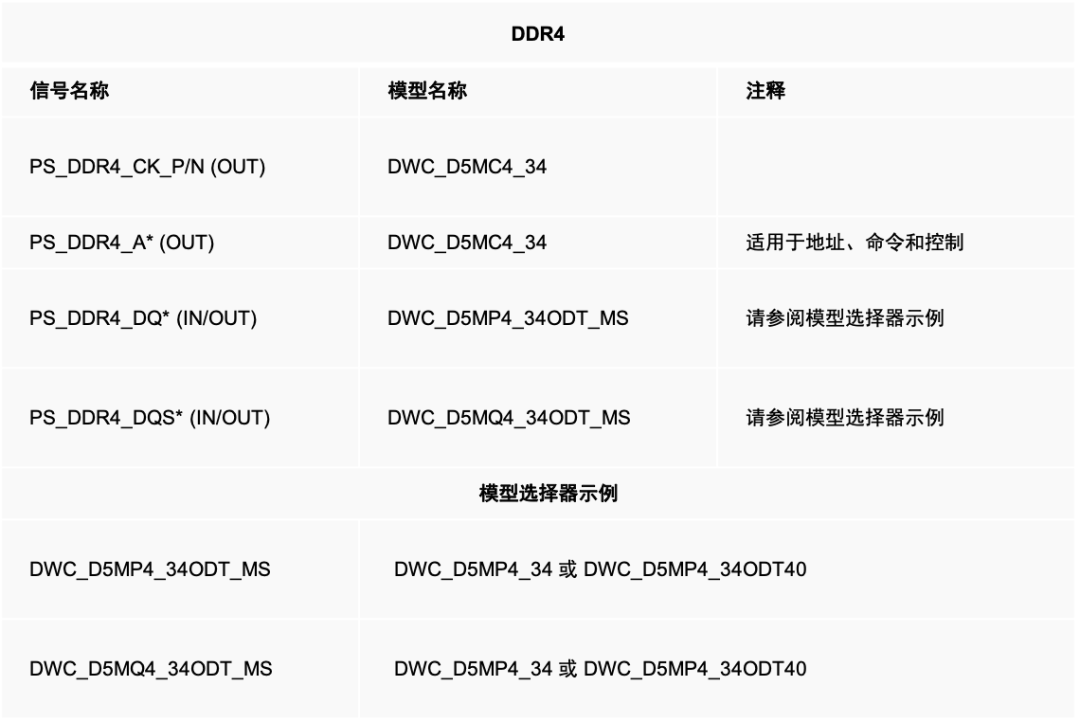

3. 賽靈思 Zynq MPSoC PS DDR IBIS 模型

Zynq MPSoC PS DDR IBIS 信號與所有其它信號都不同。

表 5 顯示了適用于 Zynq MPSoC PS DDR IBIS 模型的解碼器。

其中為每一種 DDR 內(nèi)存類型的 IBIS 模型都提供了相應(yīng)的示例。

表 5:PS DDR IBIS 解碼器

表 6 到 10 提供了對應(yīng)受支持的 PS DDR 技術(shù)的 Zynq PS DDR IBIS 示例。

表 6:PS DDR3

表 7:PS DDR3L

表 8:PS LPDDR3

表 9:PS DDR4

表 10:PS LPDDR4

-

可編程邏輯

+關(guān)注

關(guān)注

7文章

516瀏覽量

44113 -

IBIS模型

+關(guān)注

關(guān)注

8文章

15瀏覽量

17596

原文標(biāo)題:開發(fā)者分享 | 賽靈思 PL 和 PS IBIS 模型解碼器

文章出處:【微信號:FPGA-EETrend,微信公眾號:FPGA開發(fā)圈】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

變頻驅(qū)動器與可編程邏輯控制器的區(qū)別

可編程邏輯控制器的基本功能

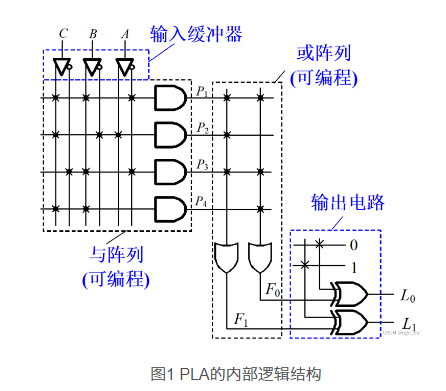

什么是現(xiàn)場可編程邏輯陣列?它有哪些特點(diǎn)和應(yīng)用?

可編程片上系統(tǒng)的基本特征和主要應(yīng)用

可編程片上系統(tǒng)是什么意思

可編程片上系統(tǒng)是什么

現(xiàn)場可編程門陣列的原理和應(yīng)用

極海APM32F407可編程邏輯控制器PLC應(yīng)用概述

可編程邏輯器件的特征及優(yōu)勢科普

可編程邏輯陣列PLA內(nèi)部邏輯結(jié)構(gòu)示意

如何為可編程邏輯和處理器系統(tǒng)進(jìn)行IBIS模型名稱解碼

如何為可編程邏輯和處理器系統(tǒng)進(jìn)行IBIS模型名稱解碼

評論