作者:Sanjay Havanur,Vishay Siliconix公司

自從30多年前首次推出以來,MOSFET已經成為高頻開關電源轉換的主流。該技術一直在穩步改進,目前我們已經擁有了對于毫歐姆RDSON值的低電壓MOSFET。對于較高電壓的器件,它正快速接近一位數字。實現這些改進的兩個主要MOSFET技術進展是溝槽柵極和電荷平衡結構[1]。電荷平衡技術最初是為能夠產生超結(superjunction)MOSFET的高電壓器件而開發的,現在該技術也擴展到更低的電壓。雖然該技術大幅度降低了RDSON以及所有的連結電容,但它也使得后者更加非線性化。MOSFET中的有效存儲電荷和能量確實減少了,并且是顯著地減少了,但是,計算這些參數或比較不同的MOSFET以獲得最佳性能,已經成為一項相當復雜的事情。

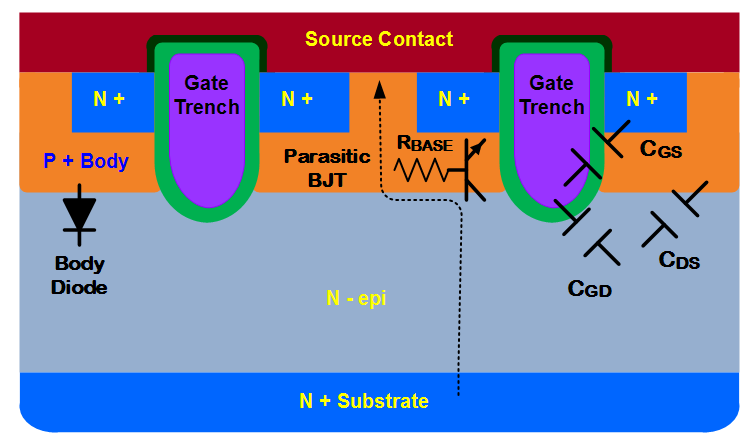

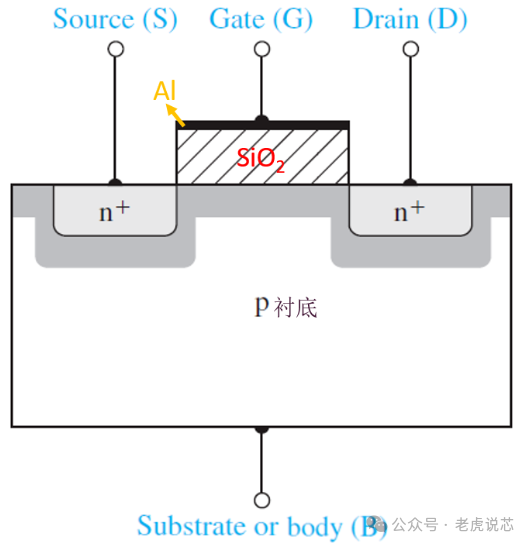

圖1a:溝槽MOSFET的結構及其電容。

圖1b:等效電容。

與MOSFET相關的三個電容的基本定義如圖1a和1b所示。以VDS的函數的方式測量這些電容并不是一件直截了當的工作,在此過程中需要它們中的某些被短路或開路(left floating)。產品資料中最后測量和給出的如下定義的三個值:

CISS = CGS + CGD

COSS = CDS + CDG

CRSS = CGD

在這三個數值中,輸入電容CGS是非線性程度最低的。它是柵極結構和源極之間的電容,并且不太作為VDS的函數而變化。另一方面,CGD是極端非線性的,對于超結器件而言,在第一個100V內變化范圍幾乎達到三個數量級。它也有助于在VDS=0時所看到的對于CISS的微小步長。

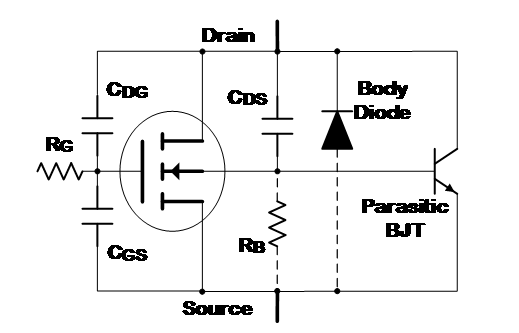

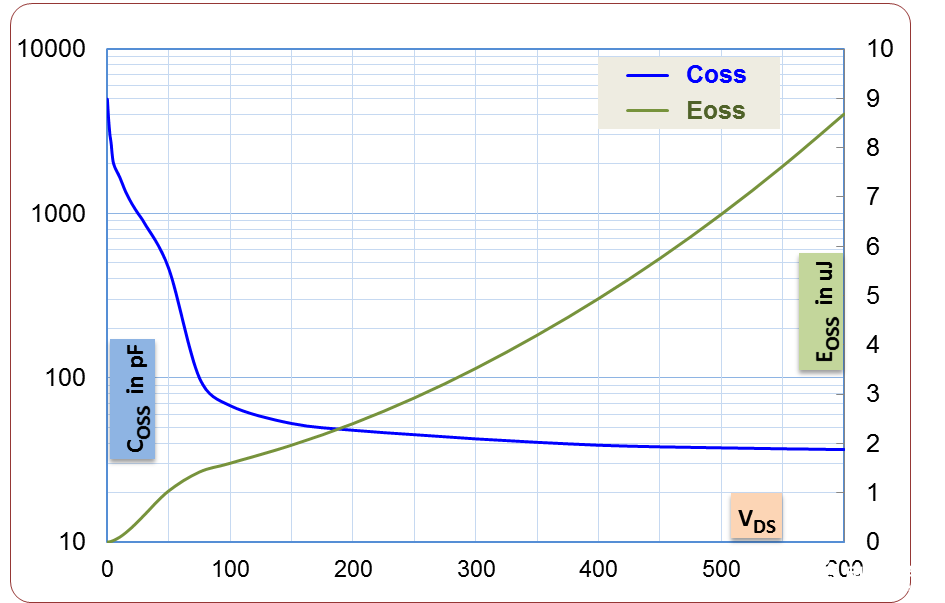

最近,很多人有興趣了解COSS的特性以及它對高頻開關的影響。這有幾個原因,例如,COSS存儲的電荷和損耗已經成為實現高頻AC-DC轉換器的最大挑戰。一般來說,任何與電容相關的損耗都與所施加電壓的平方成正比。正如文獻[3]中指出的那樣,相同的電容器在550V時的儲存能量和損耗比12V時高2100倍。隨著人們日益關注降低RDSON,導通損耗已經顯著下降,但是COSS并沒有成比例下降。例如,在早些時候,600V MOSFET在TO-220時的最低RDSON曾經是340mΩ。而現在,該數值在600V超結器件中已經下降至65mΩ。對于電容而言,在不同的技術之間比較具有相似RDSON值的器件更有意義。圖2比較了兩種器件的電容:一個是SiHP17N60D,它是一種平面器件;另一個是SiHP15N60E,它是一種超結MOSFET,具有接近但略低的RDSON。請注意,這些數值是以對數刻度繪制的。對于超結器件,COSS在100V時已經從136pF降低到67pF,但它也變得更加非線性。在平面器件中,COSS在VDS=0V與100V時比率為25:1,但現在已經上升三倍達到75:1。在VDS=0時,COSS值大于輸入電容CISS的情況并不少見。

圖2:平面MOSFET與超結MOSFET的電容比較。

參考文獻[4]~[9]從多方面嘗試解釋COSS的非線性性質,并就其對高頻開關的影響提出了新見解。在對COSS曲線進行積分、模擬以及其它復雜處理之后,這些文獻大多數都重新確認了電容的非線性性質。人們引入、模擬和分析了“小信號”電容和“大信號”電容等術語。除了在技術上不正確之外,這些新術語從行業實踐角度看也沒有產生什么區別。可以看出,所謂的大信號電容無非是與時間相關的值COTR,該數值在參考文獻[4]發表后的許多年來一直被MOSFET行業所規范。在精細仿真結果與產品資料數值之間突出差異依然很好地處于MOSFET的產品描述和批量生產中所涉及的公差范圍內。

另外一個分析方法提出了在與COSS串聯時的隱藏電阻,即ROSS,用于描述與非線性電容相關聯的所有原因不明的損耗(見參考文獻[10])。但這與基本電路理論相矛盾,該理論明確指出:電容器充放電損耗完全由存儲在其中的能量所決定,而與任何串聯電阻的值無關。關于ROSS,沒有人提出過任何半導體層面的解釋或實驗驗證,而該論文中所提供的波形清楚地顯示出導通的MOSFET體二極管,它為這些損耗提供了更簡單(如果不是太奇特的話)的解釋。事實上,體二極管導通在對具有感應負載的任何橋式電路進行分析時都是一項基本考慮因素。在其他最近的同行審議會議出版物中(參考文獻[11]和[12])已經提出,COSS中的存儲電荷和能量都存在遲滯現象,并且在不同的電壓路徑下可能存在差異。這種遲滯的意義在于,電荷守恒原理不適用于功率MOSFET。

它不是要挑戰物理學的基本定律,而是要重新審視他們,并驗證它們是否正確地在適當場合加以正確運用,這更有啟發性。調查提出了一個不解之謎,因此可能進行得有點引人入勝 —

如果兩個電容并聯連接,充電到相同的電壓并保持完全相同的存儲電荷,那么,是否必然得出結論說,它們也存儲了相同的能量?

根據眾所周知的公式Q=CV和E=?CV2,答案應該是肯定的“是”。情況似乎應當是,即使電容是非線性的,這個結論在任何電壓下也都應當成立。但遺憾的是,關于存儲的電荷和能量的那些熟悉的公式并不是普遍有效的,它們只適用于恒定電容這種特殊情況。更基本的關系是將電容定義為電荷轉換(w.r.t.)電壓的變化速率,而電壓本身被定義為單位電荷能量變化的度量。換句話說,基本的關系是:

C = dQ/dV 和 V = dE/dQ

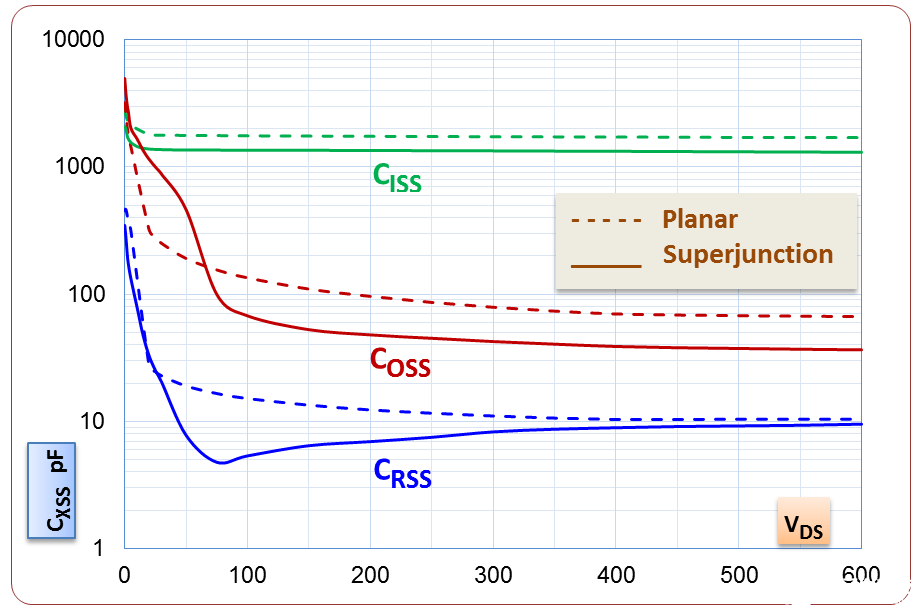

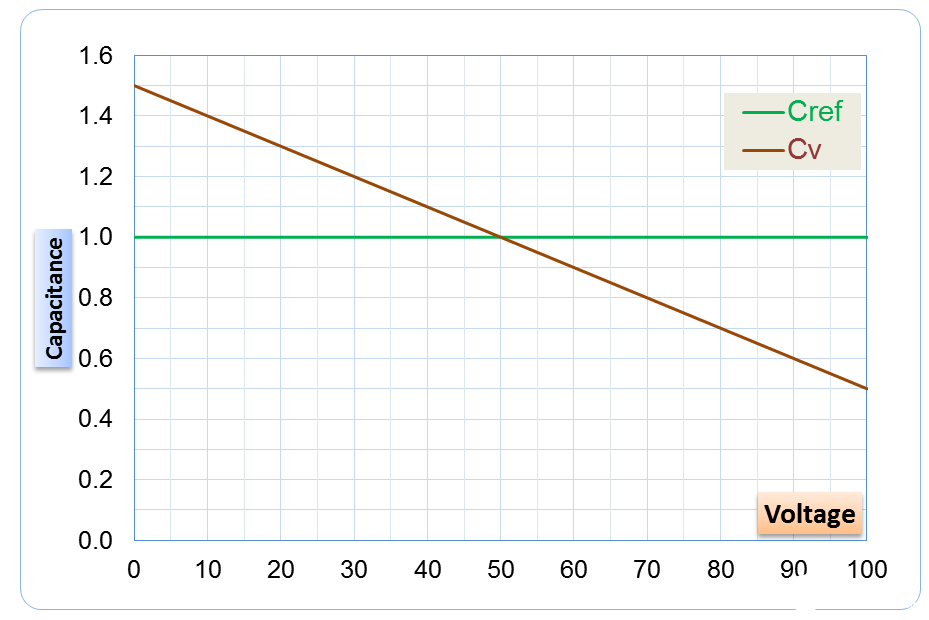

關于電荷和能量的簡單方程在推導時存在靜態電容這一隱含假設。對于非線性電容,必須通過在電壓上分別積分電容和電荷來導出電荷和能量。為了進一步說明這一點,請考慮圖3描述的兩個電容器。基準值由電容器CREF提供。另一電容器CV從1.5xCREF到0.5xCREF線性變化。在100V時,它們攜帶相同的電荷。觀察這兩個電容器的CxV面積可以清楚地看到這一點,并且也可以通過在電壓上對電容值進行積分來驗證。

然而,所存儲的能量是完全不同的。如果在電壓上對所存儲的電荷進行積分,可以發現,CREF僅具有在100V時所存儲能量的83.3%。還可以看到,在75V時,CV所存儲電荷比CREF多10%,但兩者的能量是相同的。

圖3:恒定電容與可變電容的對比。

MOSFET制造商多年來一直在進行這些積分,但他們不是將其指定為電荷和能量,而是將其轉換為兩個不同的等效電容。

COTR——一個固定電容,其在充電至80% VDSS時具有與COSS相同的存儲電荷

COER——一個固定電容,其在充電至80% VDSS時具有與COSS相同的存儲能量

參考文獻[4]給出了“有效”COSS在80%額定電壓情況下的經驗值,它與時間相關的等效電容相同。但是,該應用說明并未區分COTR和COER,它們兩者已經變得非常不同,需要單獨處理。請注意,COTR和COER兩者本身都是電壓的函數;對非線性函數進行的任何積分將總是產生另一個非線性函數。因此,產品資料把它們定義在某個具體的電壓之下,例如額定VDS的80%或400V。對于相同的COSS,存在兩種不同的“等效”值,一個用于存儲電荷,另一個用于能量,這一事實多多少少能夠解答上述難題。

COTR和COER不僅互不相同,而且它們之間差異的程度可作為測量非線性的指標。在我們的例子中,1.5:0.5的電容范圍會在COTR與COER之間產生16.7%的差異。對于SiHP15N60E而言,相同的COTR/COER比率幾乎是3.6。對于其他超結器件,電容范圍可能寬于100:1,而且COTR/COER之比可能高于10。圖4a突出了SiHP15N60E中存儲電荷與能量之間的差異。作為電壓的函數,這兩個相關參數的變化率有著顯著不同。超大COTR以及由此所隱含的超大總存儲電荷,需要在所有的橋配置中加以考慮,尤其是那些運行在ZVS模式下的配置。對MOSFET的輸出電容放電與對其進行消能(de-energizing)是不太一樣的,應當根據COTR進行設計計算,而不應當根據COER。當然,COER和能量對于計算開關損耗仍然是需要的(參考文獻[3])。

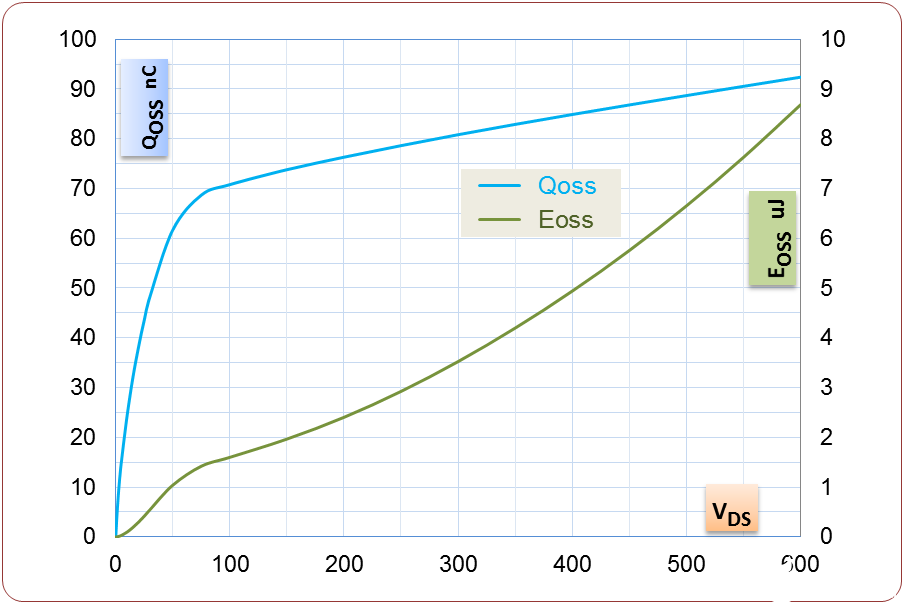

現在應該很清楚了,COSS在任何電壓下的絕對值不再有什么意義。用戶也不再需要它。它本身不是與電路相互作用的電容,而是定義該行為的存儲電荷和能量。如果你考察任何涉及COSS的設計計算,你將會發現,在某種地方,它通過與相關電壓因子相乘而被轉化為存儲電荷或能量。為了進一步幫助系統設計人員,包括Vishay在內的一些MOSFET制造商目前已經在其高電壓產品資料中除了提供COTR和COER之外,還提供完整的EOSS曲線,如圖4b所示。對于100V MOSFET,通常把QOSS規定在50%,以幫助在48V ZVS橋接線路中進行死區時間分析。

圖4a:COSS儲存電荷和能量與電壓的對比。

圖4b:電容和存儲能量與電壓的對比。

類似的考慮也適用于柵漏電容CRSS,但其價值遠遠低于COSS。根據定義,其值已經包含在本文開始提及的對COSS的測量中。CRSS的非線性特性實際上在很早以前就被認為是一個問題,而且一直在各種文獻中有所闡述。柵極電荷曲線中的QGD成分也不過是CRSS中的總存儲電荷,該電荷需要在開關接通或斷開期間注入到柵極或從柵極移除。請注意,柵極電荷曲線的分段線性分割并不是由于所涉及的電容的任何非線性特性所致。打開MOSFET的過程涉及到對兩個不同的電容器進行充電,這兩個電容在關斷狀態下有不同電壓(見參考文獻[2])。

在處理MOSFET時,牢記這一點是很有用的:它的電容并不是由電介質所隔開的兩個電極組成的。它們的電容在本質上是短暫的,主要出現于開關間隔期間,此時器件受到高dV/dt的影響。等效電路中顯示的電容揭示了半導體材料中的有源電場與其電流之間的相互作用。只有當這種關系是線性時,這種揭示才是有意義的。對于我們在當今的MOSFET器件中看到的極端非線性情況,可以絲毫不夸張地說,根本不存在COSS或CRSS這樣的事情。對電容曲線進行積分無法揭示出它們如何與電路的其余部分進行相互作用的任何信息。設計人員不應當嘗試線性化并以某種方式拉直該曲線,而是需要專注于基礎知識,并直接處理存儲的電荷和能量。

參考文獻:

[1] Sanjay Havanur和Philip Zuk.“功率MOSFET基礎原理:了解超結技術”,Vishay應用注記AN-849,2015年4月,http://www.vishay.com/docs/66864/an849.pdf

[2] Sanjay Havanur,“功率MOSFET基礎原理:理解開關過程”,Vishay應用注記AN-850,2015年6月,http://www.vishay.com/docs/68214/turnonprocess.pdf

[3] Sanjay Havanur,“謹慎處理零電壓開關”,2016年4月通訊,http://www.how2power.com/pdf_view.php?url=/newsletters/1604/articles/H2PToday1604_design_VishaySiliconix.pdf

[4] 國際整流器,“功率MOSFET輸出電容COSS更真實的特征”,AN-1001,1999年。http://www.infineon.com/dgdl/an-1001.pdf?fileId=5546d462533600a401535590a5c70f36

[5] Shen,Z.John,Yali Xiong,Xu Cheng,Yue Fu和Pavan Kumar.“功率MOSFET開關損耗分析:一項新洞察”。2006年 IEEE工業應用會議第四十一屆IAS年會,第3卷,第1438-1442頁。

[6] M.Orabi,A.Abou-Alfotouh和A. Lotfi.“Coss電容對同步降壓轉換器損耗的貢獻”,功率電子器件專家會議(PESC),2008年,第666-672頁

[7] Drofenik,U.,A.Muesing,和J.W.Kolar.“功率電子器件多域仿真中的電壓相關電容器”。2010年國際功率電子器件會議(ECCE亞洲)會議錄,第643-650頁。2010年。

[8] Costinett,Daniel,Regan Zane,和Dragan Maksimovic.“開關模式電源轉換器中非線性器件電容的電路定向建模”。功率電子器件的控制與建模(COMPEL),2012 IEEE第13期研討會,第1-8頁。IEEE,2012年。

[9] Elferich,Reinhold.“關于非線性電容的一般ZVS半橋模型以及在LLC設計中的應用”。2012年IEEE能源轉換大會及展覽會(ECCE),第4404-4410頁。

[10] “功率MOSFET在零電壓開關應用中與Coss相關的能量損耗”,JB Fedison等,IEEE應用功率電子器件會議及展覽會(APEC),2014年,第150-156頁

[11] Roig,Jaume,Filip Bauwens.“在采用超結FET的諧振轉換器中異常滯后的原因”。IEEE關于電子器件的報告,第62期,第9輯(2015年),第3092-3094頁。

[12] Fedison,J.B.和M.J.Harrison.“高級超結MOSFET中的Coss滯后”。2016年IEEE應用功率電子器件會議及展覽會(APEC),第247-252頁。

編輯:hfy

-

MOSFET

+關注

關注

147文章

7158瀏覽量

213153 -

開關電源

+關注

關注

6459文章

8328瀏覽量

481760 -

電荷平衡

+關注

關注

0文章

3瀏覽量

9723 -

RDSON控制器

+關注

關注

0文章

6瀏覽量

2343

發布評論請先 登錄

相關推薦

銳駿200V低壓和600V高壓MOS對于電機控制和電源管理

MOSFET屬于什么器件?MOSFET的用途有哪些?

MOSFET的基本結構與工作原理

突破碳化硅(SiC)和超結電力技術的極限

基于VLPE技術的碲鎘汞p-on-n雙層異質結材料與器件研究進展

用于CCD讀出的電荷耦合器件時鐘技術

產生超結MOSFET的高電壓器件開發技術——電荷平衡技術

產生超結MOSFET的高電壓器件開發技術——電荷平衡技術

評論