原子層刻蝕和沉積工藝?yán)米韵扌苑磻?yīng),提供原子級控制。 泛林集團(tuán)先進(jìn)技術(shù)發(fā)展事業(yè)部公司副總裁潘陽博士 分享了他對這個話題的看法。

技術(shù)節(jié)點的每次進(jìn)步都要求對制造工藝變化進(jìn)行更嚴(yán)格的控制。最先進(jìn)的工藝現(xiàn)在可以達(dá)到僅7 nm的fin寬度,比30個硅原子稍大一點。半導(dǎo)體制造已經(jīng)跨越了從納米級到原子級工藝的門檻。工程師現(xiàn)在必須關(guān)注結(jié)構(gòu)的尺寸變化,僅相當(dāng)于幾個原子大小。由于多重圖案模式等復(fù)雜集成增加了工藝數(shù)量,進(jìn)一步限制了每個步驟允許的變化。3D NAND和finFET結(jié)構(gòu)的復(fù)雜性會帶來更高挑戰(zhàn)。

對于半導(dǎo)體行業(yè)而言,控制工藝變化始終都是一大關(guān)鍵挑戰(zhàn),因為它會直接影響到產(chǎn)品的性能、良率和可靠性,進(jìn)而產(chǎn)生重大經(jīng)濟(jì)后果。工藝誘生的變化有多個來源,包括晶粒、晶圓和工具。要控制這些變化,一種方式是通過運用原子層沉積 (ALD) 和原子層刻蝕 (ALE) 等技術(shù),這些技術(shù)本身比傳統(tǒng)等離子體方法更加精確。

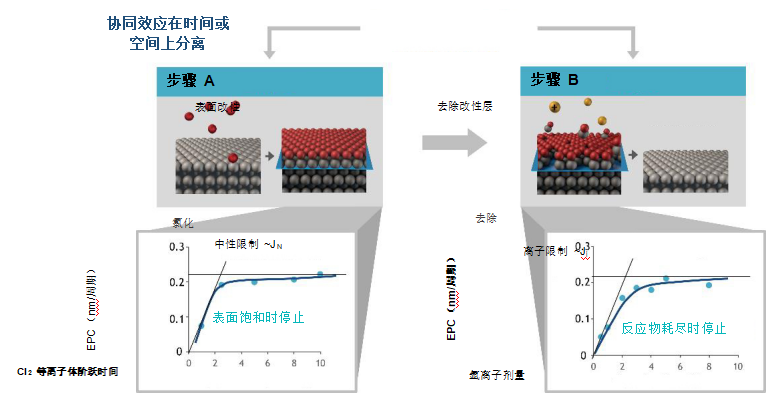

圖 1. 原子層工藝中的所有半周期反應(yīng)是自限性反應(yīng)。

原子層工藝

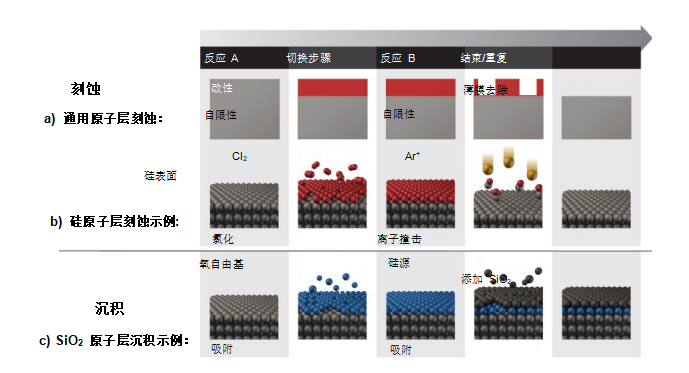

原子層工藝包括沉積和刻蝕解決方案,它們具有一些共同的特征。與連續(xù)工藝不同,它們分周期進(jìn)行,每個周期都會添加或去除有限固定數(shù)量的分子層。每個周期又分為若干半周期,每個半周期分別是不同的自限性工藝,為下個半周期準(zhǔn)備表面。例如,在 SiO2 沉積中(圖1和2),第一個半周期會吸附氧原子,這個過程是自限性的,受到結(jié)合位點的限制。然后,多余的氧被從腔室中清除,表面暴露在硅原子源下,硅原子與吸附的氧發(fā)生反應(yīng),形成一層 SiO2。這個半周期工藝也是自限性的,在這種情況下,它受到氧的限制。原子層沉積的自限和有序的特性在先進(jìn)邏輯和存儲器芯片HVM中得到了廣泛應(yīng)用。

與沉積技術(shù)相同,原子層刻蝕同樣分為若干半周期進(jìn)行,這些半周期也是自限性的。例如,在硅刻蝕工藝中,第一個半周期將硅表面暴露在氯下,氯與第一層硅原子結(jié)合,弱化它們與底層原子的鍵合(圖2)。當(dāng)表面飽和時,該過程停止,然后清除未使用的氯。第二個半周期使用氬離子來撞擊改性表面,去掉氯激活的硅頂層,而不是底層硅。氯化層去掉之后,周期完成,薄材料層已精確去除。

過去,要將原子層刻蝕工藝集成到大規(guī)模半導(dǎo)體生產(chǎn)中,我們會受制于相對連續(xù)刻蝕工藝來說較低的刻蝕速率。以下兩個因素結(jié)合在一起,減少了較低刻蝕速率對整體產(chǎn)量的影響。第一個因素是特征尺寸持續(xù)減小,從而減少了要去除的材料數(shù)量,以及所需的ALE周期數(shù)。第二個因素是ALE技術(shù)的進(jìn)步,例如快速氣體交換技術(shù),它們顯著提高了循環(huán)速度。隨著我們越來越多地需要對較小結(jié)構(gòu)實現(xiàn)原子級控制,這種技術(shù)引起了更多關(guān)注。原子層刻蝕還提供了其他一些重要優(yōu)勢,包括改進(jìn)的方向性(異向性)、更光滑的表面、更好的材料選擇性、更均勻的刻蝕表面、較少的表面損壞和混合,消除了圖案密度引起的非均勻效應(yīng),并改進(jìn)了晶圓間的均勻性。

圖 2. 原子層工藝能夠去除或沉積材料。在以上刻蝕示例中,氯吸附到硅表面,然后通過氬離子撞擊去除改性層。在沉積示例中,氧吸附到硅表面,硅與改性表面層相結(jié)合,沉積二氧化硅。

創(chuàng)新的原子層刻蝕與原子層沉積技術(shù)解決方案

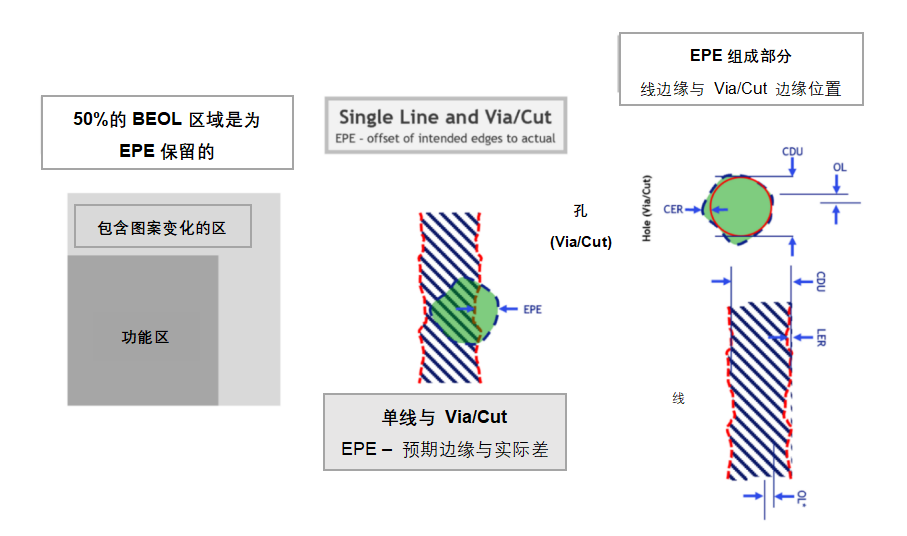

圖 3. 邊緣放置誤差 (EPE) 最終限制空間擴(kuò)展。50%的BEOL區(qū)域是為EPE保留的。因EUV光刻技術(shù)中隨機缺陷引起的線和圓形邊緣粗糙度極大地促進(jìn)了EPE的產(chǎn)生。

EUV 光刻技術(shù)中的隨機缺陷

在7nm和10nm節(jié)點采用EUV光刻技術(shù)的制造商面臨著隨機缺陷的挑戰(zhàn)。EUV光的較短波長使其能夠聚焦至更精細(xì)圖案,但也意味著每個光子具有更多能量,產(chǎn)生更多光致酸,同時曝光更大量的光刻膠。EUV系統(tǒng)非常昂貴,而且必須實現(xiàn)較高的產(chǎn)量才能在成本基礎(chǔ)上與傳統(tǒng) (i193) 光刻技術(shù)進(jìn)行競爭,因此它們采用短曝光、低光子劑量以及以最小量光子就可以實現(xiàn)曝光的化學(xué)放大光刻膠 (CAR)。光刻膠中光子與光致酸在空間與時間分布上的隨機變化性會導(dǎo)致隨機缺陷,這本質(zhì)上是一種統(tǒng)計塊度,在已創(chuàng)建的光刻膠圖案中體現(xiàn)為邊緣和表面粗糙度。圓形邊緣粗糙度 (CER) 以及線邊緣粗糙度 (LER) 均是邊緣定位誤差 (EPE) 的組成部分,最終限制了特征尺寸可能減少的程度。在先進(jìn)節(jié)點中,50% 以上的BEOL區(qū)域是為EPE保留的;設(shè)備擴(kuò)展受到EPE擴(kuò)展的限制而且需要節(jié)點對節(jié)點EPE下降30%(圖 3)。

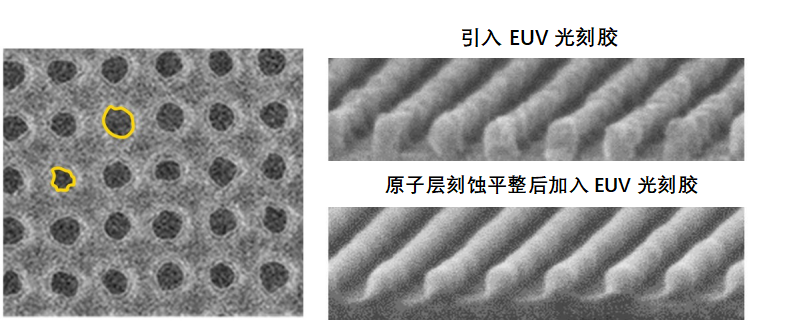

原子層刻蝕有助于減少這些隨機缺陷的影響。因為它在自限性步驟中逐層進(jìn)行,而且因為工藝步驟將化學(xué)活性物質(zhì)與高能離子相分離,因此原子層刻蝕不會產(chǎn)生傳統(tǒng)的刻蝕工藝中出現(xiàn)的粗糙的鑲邊層。更重要的是,原子層刻蝕與原子層沉積的重復(fù)循環(huán),能夠降低EUV中隨機缺陷引起的粗糙度。凹凸表面比平面具有較高的表面體積比,這就導(dǎo)致在原子層刻蝕的過程中凸面被整平,而在原子層沉積的過程中凹面被填充。不僅隨機缺陷非常小,而且在這一平整工藝過程中去除和沉積的層也非常薄,大約為半納米。事實表明,這一工藝降低了CER并提高了小尺寸孔的CD均勻度。同樣,它也降低了LER、改進(jìn)了CDU,清除了細(xì)小的(小于10nm)線寬和距離中棘手的短路缺陷(圖 4)。

圖 4. 左圖 – 黃色輪廓線表示EUV光刻技術(shù)中隨機變化引起的光刻膠中孔的局部不均勻。右圖 – 原子層刻蝕與原子層沉積重復(fù)循環(huán)能夠顯著降低光刻膠線的粗糙度。(Imec測試結(jié)構(gòu))

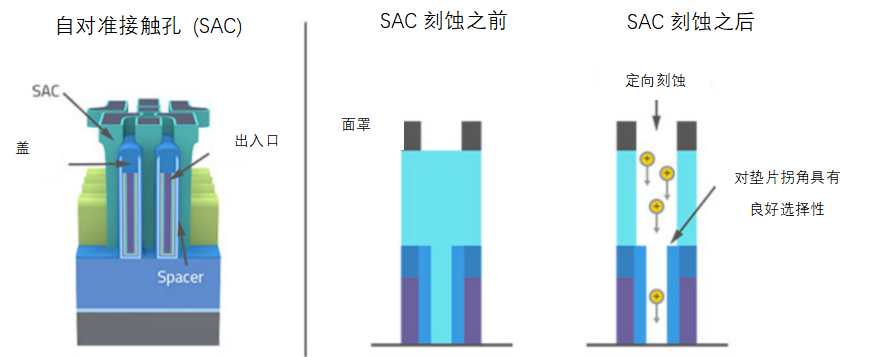

自對準(zhǔn)接觸孔刻蝕

自對準(zhǔn)接觸孔 (SAC) 通過將源極和漏極接點定位到距離柵極更近的位置而實現(xiàn)持續(xù)的縮放。在這一工藝中,柵極通過橫向氮化硅間隔層和上覆的覆蓋層與源極和漏極接點實現(xiàn)隔離。SAC刻蝕是最具挑戰(zhàn)性的刻蝕工藝之一,它可以在接觸點沉積之前去除相鄰的二氧化硅。它必須具有高度選擇性,從而清除氧化物并使氮化硅墊片保持完整。在連續(xù)刻蝕工藝中,選擇性是通過沉積一個薄的氟碳聚合物涂層來實現(xiàn)的。在刻蝕過程中,氧化物中的可用氧分會燒掉聚合物中的碳,從而使刻蝕繼續(xù)進(jìn)行。而當(dāng)聚合物覆蓋氮化物時,沒有氧分可用,而刻蝕則被抑制。問題存在于氮化硅墊片的頂處。在暴露角度為45?-70?時,濺射速率最大;因此,在拐角處的刻蝕速度比在平面上快,而且隨著拐角變得更加圓滑,防護(hù)聚合物就更難粘附。拐角處的過度圓滑和腐蝕最終將導(dǎo)致柵極與源極/漏極之間的短路。

原子層刻蝕 (ALE) 通過將防護(hù)層的沉積與刻蝕步驟進(jìn)行隔離,從而解決這一問題(圖 5)。沉積過程中不存在離子,因此在沉積過程中存在最小濺射,且聚合物可以均勻地沉積在包含拐角的位置上。在刻蝕循環(huán)過程中,只有離子 (Ar+)存在,氧化物中的氧燒掉聚合物,而氟碳聚合物中的氟腐蝕氧化物。當(dāng)聚合物消失時,氟也隨之消失,如果偏壓功率低于氮化硅的濺射閾值,則刻蝕停止。在氮化物上,沒有氧氣存在,使聚合物基本保持完整,氟的含量極低,使刻蝕得到抑制。ALE降低了拐角的圓滑度,使聚合物厚度變薄,因此可以使用更薄的墊片。ALE使用自限性半循環(huán)將表面改性步驟與主動刻蝕步驟相分離,與連續(xù)刻蝕工藝相比提供了更大的靈活性和更好的控制。(值得一提的是,通過調(diào)節(jié)各種工藝參數(shù),可以對選擇性進(jìn)行逆轉(zhuǎn),優(yōu)先刻蝕氮化物而非氧化物。)

圖 5. 自對準(zhǔn)接觸孔采用一個橫向墊片將柵極與源漏接觸孔相隔離。ALE避免在墊片上角過度刻蝕,這在連續(xù)刻蝕工藝中很常見。

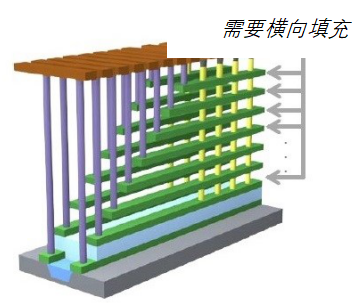

3D NAND字線的鎢沉積

3D NAND利用垂直整合極大地增加了存儲設(shè)備的存儲密度。以往,結(jié)構(gòu)局限于兩個維度,通過減小尺寸從而限制密度;如今,結(jié)構(gòu)在第三個維度中得以擴(kuò)展。這些設(shè)備包括非常規(guī)幾何圖形以及極高的深寬比特征,這帶來了獨有的工藝挑戰(zhàn)。

其中最具挑戰(zhàn)性的是向字線中填充導(dǎo)電鎢。3D NAND交替堆疊氧化物和氮化物介電層,當(dāng)前一代中有多達(dá)96層,更高層數(shù)還在研發(fā)中(圖 6)。密集排列且具有高深寬比的孔滲透至這些層中,按照高深寬比通道將排列分為字線。為了創(chuàng)建存儲單元,必須移除氮化物層并以鎢進(jìn)行替換。這種鎢必須通過深(垂直深度 50:1)通道引入,然后橫向擴(kuò)散,從而以無空洞的超共形沉積方式填充(之前的)氮化物水平面(橫向比約 10:1)。原子層沉積能夠一次沉積一個薄層,這就確保了均勻填充,并防止因堵塞而產(chǎn)生的空隙。

一種成功的方法就是在填充工藝中添加形狀選擇性抑制劑,防止在填充較高深寬比結(jié)構(gòu)之前,出現(xiàn)較低深寬比結(jié)構(gòu)中的過度沉積。由內(nèi)而外的ALD工藝可以完全填充橫向(水平)線且不留空隙,同時最大限度地減少了垂直通道中的沉積,從而提升了電氣性能和工藝成品率。

圖 6. 3D NAND采用復(fù)雜的高深寬比結(jié)構(gòu)。創(chuàng)建字線需要超共形鎢沉積,而這必須填充垂直和水平空間且不留空隙。

結(jié)語

原子層刻蝕與沉積工藝?yán)米韵扌苑磻?yīng),提供原子級的控制。工藝產(chǎn)量提升、從更小的結(jié)構(gòu)中移除的材料減少、以及對原子級控制的需求不斷增長,這些因素都重新引起了人們對原子層刻蝕的興趣。原子層工藝提供的控制水平,確保其在當(dāng)前乃至未來的半導(dǎo)體制造業(yè)中將發(fā)揮越來越重要的作用。

編輯:hfy

-

半導(dǎo)體行業(yè)

+關(guān)注

關(guān)注

10文章

403瀏覽量

41133 -

3d nand

+關(guān)注

關(guān)注

4文章

93瀏覽量

29382

發(fā)布評論請先 登錄

半導(dǎo)體制造中的高溫氧化工藝介紹

半導(dǎo)體制冷機chiller在半導(dǎo)體工藝制程中的高精度溫控應(yīng)用解析

半導(dǎo)體boe刻蝕技術(shù)介紹

半導(dǎo)體制造關(guān)鍵工藝:濕法刻蝕設(shè)備技術(shù)解析

最全最詳盡的半導(dǎo)體制造技術(shù)資料,涵蓋晶圓工藝到后端封測

半導(dǎo)體薄膜沉積技術(shù)的優(yōu)勢和應(yīng)用

ALD和ALE核心工藝技術(shù)對比

半導(dǎo)體制造里的ALD工藝:比“精”更“精”!

原子層沉積(ALD, Atomic Layer Deposition)詳解

【「大話芯片制造」閱讀體驗】+ 芯片制造過程和生產(chǎn)工藝

半導(dǎo)體晶圓制造工藝流程

半導(dǎo)體濕法和干法刻蝕

半導(dǎo)體制造過程解析

評論