在過去兩年了,得益于自己的設(shè)計(jì)優(yōu)勢還有臺(tái)積電先進(jìn)制程的加持,AMD在處理器的地位日益攀升,并逐漸有了叫板Intel的底氣。據(jù)報(bào)道,AMD現(xiàn)在正在將更多的訂單轉(zhuǎn)向臺(tái)積電,以謀求更大的成功。而這無論對臺(tái)積電、AMD都是有利的,受傷的也許就只有格芯一個(gè)。 首先看TSMC方面,根據(jù)過往經(jīng)驗(yàn),他們大約每兩年就會(huì)提出一個(gè)前沿節(jié)點(diǎn)。2018年為7nm; 2020年達(dá)到5nm;2022年將達(dá)到3nm,依此類推。隨著工藝的成熟,每片晶圓的成本迅速下降。 對于客戶而言這是非常好的,是因?yàn)椴⒎敲總€(gè)人都能負(fù)擔(dān)得起先進(jìn)的流程,也不是每個(gè)人都需要最新技術(shù)所提供的性能。客戶轉(zhuǎn)向基于經(jīng)濟(jì)學(xué)的新工藝,對某些人來說,必須處于領(lǐng)先地位,而對于另一些人,只有在晶圓價(jià)格跌至一定水平時(shí)才有意義。隨著時(shí)間的流逝,采用率不斷增長,曾經(jīng)的領(lǐng)先優(yōu)勢已成為性能主流,然后成為主流,再到舊的滯后過程。 除非制程貫穿整個(gè)生命周期,并且在過程生命周期內(nèi)產(chǎn)能幾乎全部用盡,否則臺(tái)積電在過程中的投資不會(huì)產(chǎn)生有吸引力的投資回報(bào)。當(dāng)像Apple這樣的大型客戶主要使用領(lǐng)先的功能并且可能僅使用領(lǐng)先的一個(gè)節(jié)點(diǎn)但對較舊的技術(shù)沒有太多使用時(shí),這將成為一個(gè)挑戰(zhàn)。 例如,Apple將在2020年的型號(hào)中使用最新的5nm工藝,在較舊的型號(hào)中使用7nm工藝,但在較舊的節(jié)點(diǎn)中可能沒有任何有意義的數(shù)量。當(dāng)臺(tái)積電推出3nm節(jié)點(diǎn)時(shí),許多蘋果晶圓需求將在3nm / 5nm,而7nm的數(shù)量將直線下降。 一旦蘋果退出領(lǐng)先的流程,臺(tái)積電就必須找到其他可以使用該制程的客戶。但是,鑒于蘋果龐大的銷量,這種能力很難填補(bǔ)。臺(tái)積電需要一些大批量的應(yīng)用程序來填補(bǔ)容量泡沫。大量的PC,CPU和GPU可以滿足要求。例如,當(dāng)蘋果騰出7納米制程時(shí),AMD可以將該容量用于中端或低端CPU。當(dāng)AMD騰出該容量時(shí),Nvidia(可以將其用于主流或低端GPU。在Nvidia之后,物聯(lián)網(wǎng)設(shè)備制造商可以使用該容量。這是臺(tái)積電(TSMC)等代工企業(yè)的不變節(jié)奏。 臺(tái)積電也有幫助的一件事是,蘋果很可能為其留下的產(chǎn)能泡沫付出了高昂的代價(jià)。并非每個(gè)人都有蘋果的經(jīng)濟(jì)實(shí)力。對于AMD而言,如果AMD想要的是領(lǐng)先的能力,那么對于臺(tái)積電來說,尋找采用舊工藝的客戶將變得充滿挑戰(zhàn)。如果AMD能夠?yàn)槠湟羊v出的CPU的處理量帶來收益,那么臺(tái)積電的經(jīng)濟(jì)性將得到改善,臺(tái)積電也有可能為AMD提供更好的定價(jià),以幫助提高TSMC流程的利用率。 請注意,AMD不需要為其所有設(shè)備使用最先進(jìn)的功能。例如,該公司用于低端筆記本電腦和Chromebook的較便宜的CPU不需要先進(jìn)的工藝,因?yàn)槌杀緦τ谶@些芯片而言比性能更為重要。低端圖形芯片也是如此。利用容量泡沫,它通過將高端芯片轉(zhuǎn)移到較新的節(jié)點(diǎn)來制造,制造這些低端芯片可能對AMD有吸引力。 在臺(tái)積電上整合越來越多的設(shè)計(jì)可以簡化AMD的運(yùn)營,也減少了工程工作量。AMD工程師必須使用更少的流程,這也可以幫助公司優(yōu)化設(shè)計(jì)。 盡管GlobalFoundries過去一直是一個(gè)有能力的合作伙伴,但它發(fā)現(xiàn)領(lǐng)先的產(chǎn)能競爭非常昂貴,并且減少了對先進(jìn)工藝的投資。隨著時(shí)間的流逝,這種動(dòng)態(tài)將迫使AMD將越來越多的設(shè)計(jì)轉(zhuǎn)移到臺(tái)積電,因?yàn)镚lobalFoundries可能不再是新設(shè)計(jì)的可行選擇-即使在低端。 還要注意,即使在高端HEDT和服務(wù)器CPU解決方案方面,AMD僅選擇將TSMC 7nm工藝用于計(jì)算芯片,而不是用于IO芯片(請參見下圖)。

如圖所示,AMD的I/O芯片采用14nm工藝制造,原因有二。第一個(gè),也是更廣為人知的是,IO芯片不會(huì)從7nm工藝中受益良多,而將其保留在GlobalFoundries 14nm工藝中更具成本效益(有人猜測AMD也使用TSMC 14nm工藝來制造I/O芯片);第二個(gè)是鮮為人知且未經(jīng)證實(shí)的問題,那就是AMD可能需要許可特殊的IO/設(shè)計(jì),這些設(shè)計(jì)在AMD設(shè)計(jì)Zen 2時(shí)可用,只有14nm而不是7nm。 隨著時(shí)間的流逝,所需的第三方I/O設(shè)計(jì)可能會(huì)使用TSMC的 7nm技術(shù)制造。如果是這樣的話,將IO芯片遷移到7nm并使用增加的晶體管密度來添加新功能對于AMD的下一代產(chǎn)品來說可能是有意義的。 在臺(tái)積電制造計(jì)算機(jī)和I/O die可能會(huì)提高AMD的運(yùn)營效率。由于臺(tái)積電一直在尋求發(fā)展其封裝業(yè)務(wù),因此本文所述的這一舉措也可能為臺(tái)積電從AMD贏得部分或全部封裝業(yè)務(wù)奠定基礎(chǔ)。如果是這樣,這還可以幫助減少復(fù)雜多芯片設(shè)備的AMD制造周期。 考慮到上述因素,將增量業(yè)務(wù)從GlobalFoundries轉(zhuǎn)移到TSMC是AMD業(yè)務(wù)的順理成章的進(jìn)展,隨著時(shí)間的流逝,很可能會(huì)降低AMD的運(yùn)營和產(chǎn)品成本。隨著時(shí)間的流逝,AMD的運(yùn)營支出將下降,利潤率將增加。 對于臺(tái)積電來說,這也是有利的,因?yàn)榕_(tái)積電在晶圓代工領(lǐng)域的市場份額不斷增長,并且在理想的前沿工藝業(yè)務(wù)中增加了收入。

責(zé)任編輯:xj

原文標(biāo)題:AMD將更多訂單轉(zhuǎn)向臺(tái)積電

文章出處:【微信公眾號(hào):EDA365】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

-

處理器

+關(guān)注

關(guān)注

68文章

19312瀏覽量

230035 -

amd

+關(guān)注

關(guān)注

25文章

5470瀏覽量

134234

原文標(biāo)題:AMD將更多訂單轉(zhuǎn)向臺(tái)積電

文章出處:【微信號(hào):eda365wx,微信公眾號(hào):EDA365電子論壇】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評(píng)論請先 登錄

相關(guān)推薦

史上首次,AMD在數(shù)據(jù)中心市場的銷售額超過了英特爾!

AMD全新處理器擴(kuò)大數(shù)據(jù)中心CPU的領(lǐng)先地位

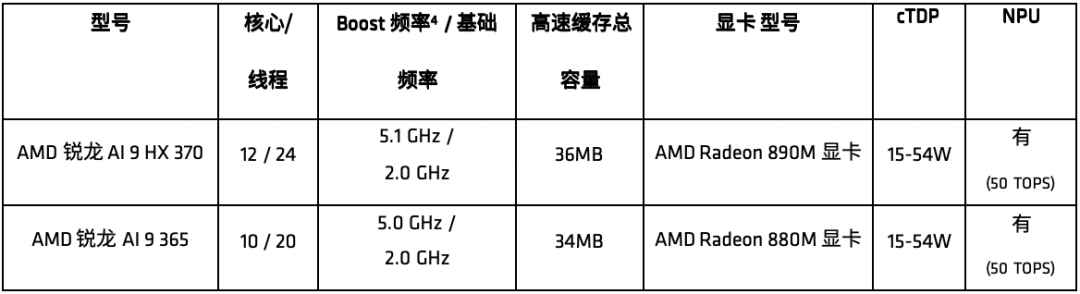

AMD推出全新銳龍AI 300系列處理器

AMD穩(wěn)固合作,贏得索尼PS6處理器芯片設(shè)計(jì)合同

第五代AMD EPYC處理器預(yù)計(jì)下半年發(fā)布

使用STM32F407ZGT6的設(shè)備無法連接到AMD處理器的電腦上,怎么處理?

研華工控機(jī)購買指南:Intel vs AMD工控機(jī)處理器(CPU)怎么選?

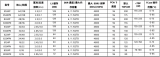

AMD推出全新AMD銳龍和EPYC處理器,擴(kuò)大數(shù)據(jù)中心和PC領(lǐng)域領(lǐng)先地位

超微發(fā)布新款AMD H13代CPU服務(wù)器產(chǎn)品

AMD推AI PC新處理器,挑戰(zhàn)英偉達(dá)與英特爾領(lǐng)先地位

AMD EPYC 8004系列處理器優(yōu)勢介紹

Intel處理器全球份額高達(dá)78%!是AMD的六倍還多!

AMD在處理器的地位日益攀升,并逐漸有了叫板Intel的底氣

AMD在處理器的地位日益攀升,并逐漸有了叫板Intel的底氣

評(píng)論