在嵌入式系統處理器中有相當一部分處理器不帶SPI接口,但基丁SPI接口的設備非常豐富,此外,SPI設備的不同以及處理器對GPIO口位尋址是否支持各處理器各有不同,因而不同處理器中軟件模擬GPIO也各不相同。若能提供一種通用可配置可移植的GPIO模擬SPI總線的驅動則能很方便快捷的訪問SPI設備,從而提高整個嵌入式系統的開發效率。本文針對GPIO口位尋址與否給出方面,給出了一種可配置GPIO模擬SPI總線的方法并詳細介紹了其設計與實現過程,且具有代碼小可移植性強使用方便等特點。

1 GPIO規范

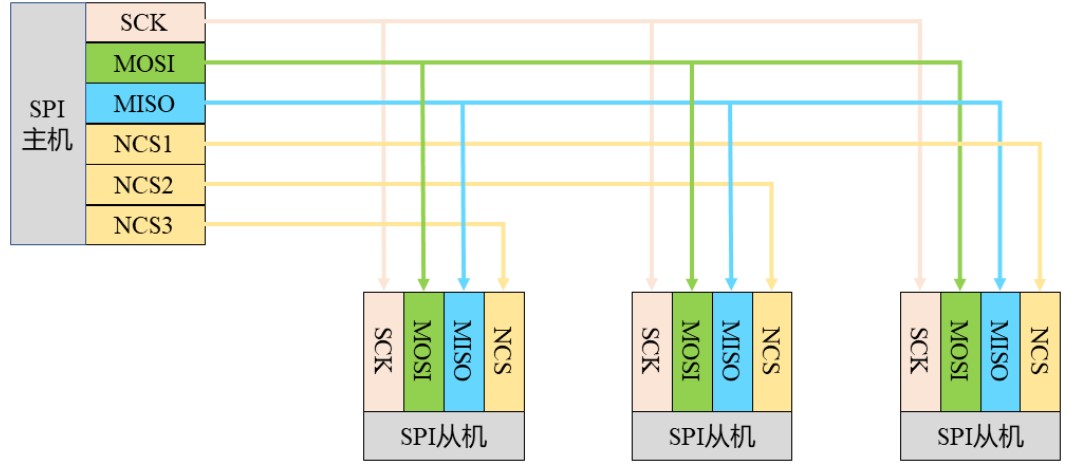

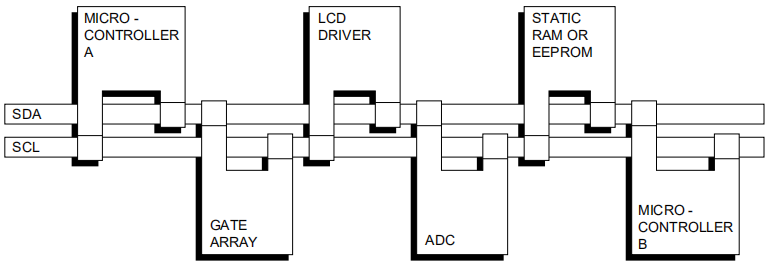

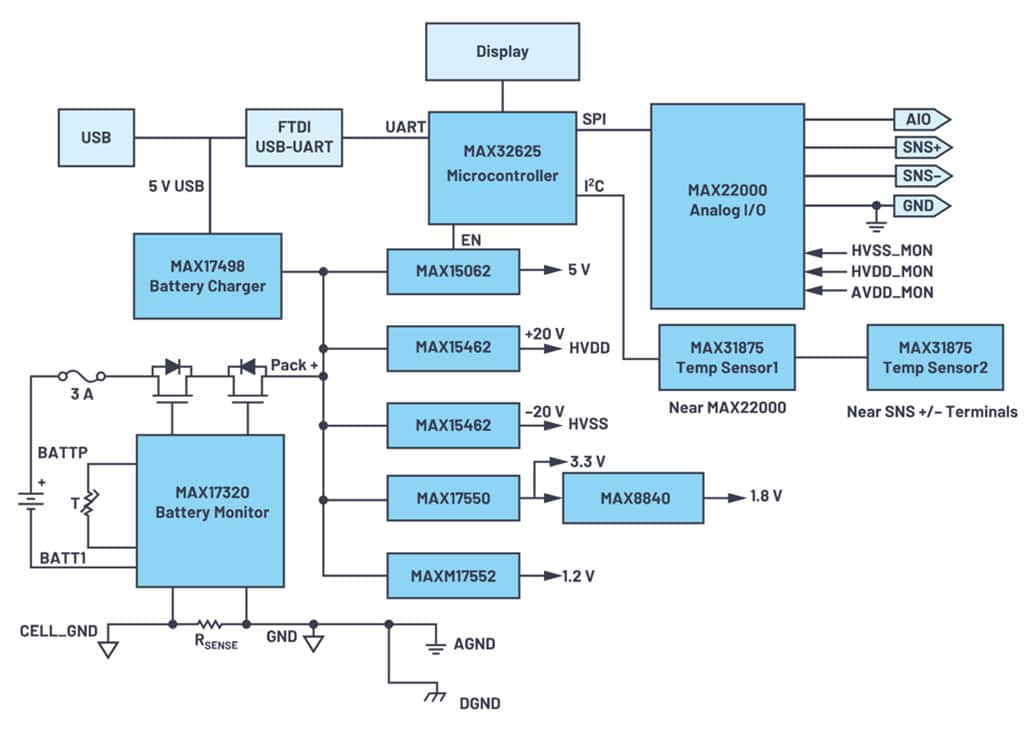

SPI是一個全雙工的串行接口。它設計成可以在一個給定總線上處理多個互聯的主機和從機。在一定數據傳輸過程中,接口上只能有一個豐機和一個從機能夠通信。在一次數據傳輸中,主機總是向從機發送一個字節數據,而從機也總是向主要發送一個字節數據。可以使MCU與各種外圍設備以串行方式進行通信以交換信息。由于SPI總線一共只需3~4位數據線和控制線即可實現與具有SPI總線接口功能的各種I/O器件進行接口,而擴展并行總線則需要8根數據線、8~16位地址線、2~3位控制線,岡此,采用SPI總線接口可以簡化電路設計,節省很多常規電路中的接口器件和I/O口線,提高設計的可靠性。在基于SPI總線接口構成的通信網絡中,通信可由主節點發起,也可由從節點發起。當主節點發起通信時,它可主動對從節點進行數據的讀寫操作。工作過程敘述如下:首先選中要與之通信的從節點(通常片選端為低有效),而后送出時鐘信號,讀取數據信息的操作將在時鐘的上升沿(或下降沿)進行。每送出八個時鐘脈沖,從節點產生一個中斷信號,該中斷信號通知上節點一個字節已完整接收,可發送下一個字節的數據。SPI接口網絡主從點需完成給出片選信號及時鐘信號,它可主動的與各從節點進行信息的交流;而在從節點主動要求服務的情況下,它卻是一種半主動的形式。由SPI接口技術構成的網絡接口信號線(CLK、MOSI、MISO、/SS和INT)如果輔之以相應完備的通信協議,其服務功能必然會增強,相比于485等主從式分布網絡而言,其通信速率也應有較人的提高。

2 GPIO模擬SPl

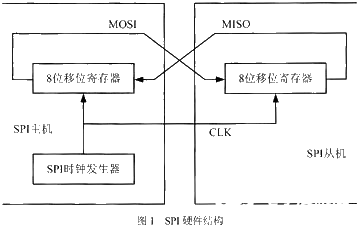

2.1 SPI硬件結構

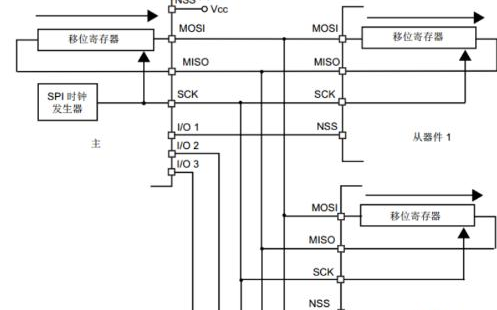

SPI接口在內部硬件實際上足兩個簡單的移位寄存器,傳輸的數據為8位,在主器件產生的從器件使能信號和移位脈沖下,按位傳輸,高位在前,低位在后,SPI內部硬件結構如圖1所示。

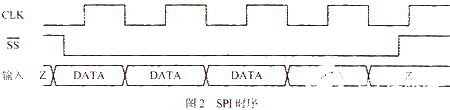

2.2 SPI時序

在SCLK的下降沿上數據改變,同時一位數據被存入移位寄存器,SPI時序如圖2所示。

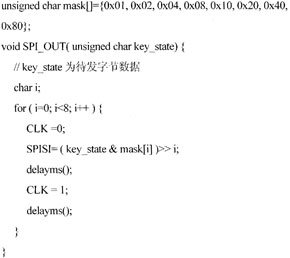

2.3 SPI寫過程模擬

采用掩碼方式實現位控制。

3 可配置GPIO設計與實現

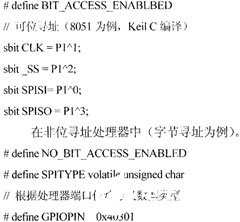

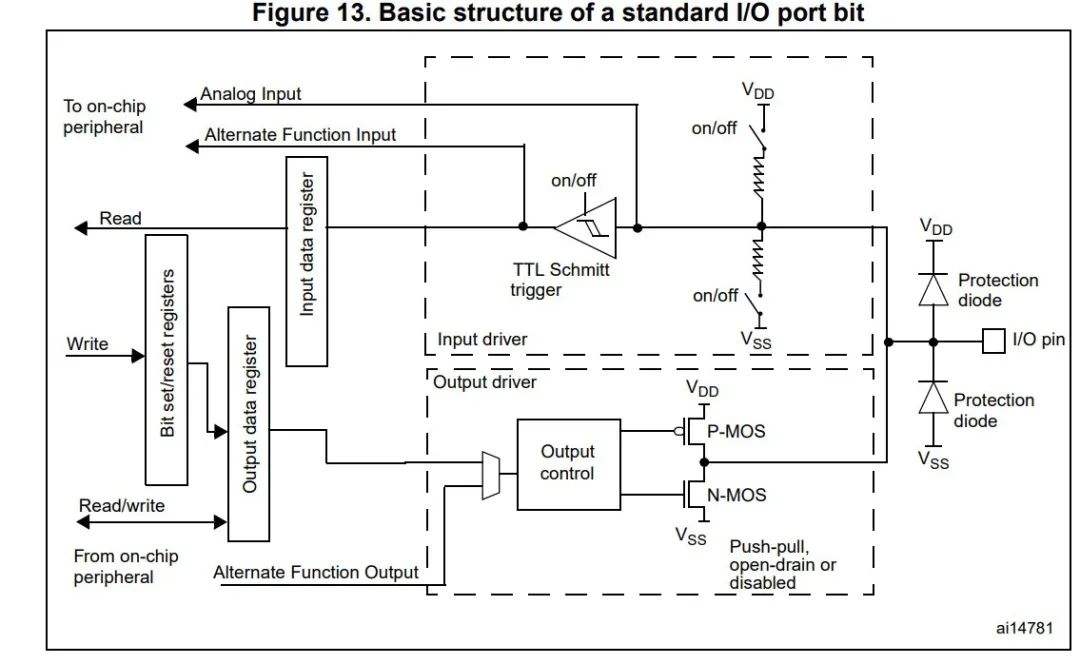

GPIO端口可分為支持位尋址和不支持位尋址,需由程序移植人員根據處理器及編譯器情況定義GPIO對應的SPI接口,相關文件在SPIHARD.H中。

3.1 GPIO配置

3.2 實現配置的可移植部分

與GPIO口尋址方式無關性代碼的實現。

以上實現在EPSON S1C33L11、AT89C52、SPCE061A及PHILIPS ARM LPC2106上都得到驗證。

責任編輯:gt

-

處理器

+關注

關注

68文章

19259瀏覽量

229653 -

接口

+關注

關注

33文章

8575瀏覽量

151019 -

SPI

+關注

關注

17文章

1706瀏覽量

91507

發布評論請先 登錄

相關推薦

基于GPIO模擬的SPI接口驅動設計與實現

GPIO模擬I2C總線的驅動設計與實現

基于Avalon總線的可配置LCD控制器IP核的設計

一種高速可配置實時總線的開發及其應用

兼容I2C總線和可配置模擬輸出的PAC192

UG-753:使用片上基準電壓源和SPI接口評估8通道、12位、可配置的ADC/DAC/GPIO AD5592R

STM32 SPI配置及深入解析

STM32F103+TM1638 SPI驅動,非GPIO模擬SPI

軟件可配置模擬 I/O 的設計理念

可配置GPIO模擬SPI總線的設計和實現過程分析

可配置GPIO模擬SPI總線的設計和實現過程分析

評論