在過(guò)去的幾年中,諸如“多線程”,“多處理”和由此衍生出的市場(chǎng)術(shù)語(yǔ)等術(shù)語(yǔ)已開(kāi)始作為現(xiàn)有電子設(shè)計(jì)自動(dòng)化(EDA)軟件的功能出現(xiàn)。同時(shí),廉價(jià)的計(jì)算資源的可用性(最好地體現(xiàn)在當(dāng)今可用的多核中央處理器(CPU)中)可以提供一種經(jīng)濟(jì)有效的方式來(lái)減少EDA軟件的運(yùn)行時(shí)間。

物理設(shè)計(jì)和物理驗(yàn)證軟件是需要此類(lèi)技術(shù)的計(jì)算密集型EDA應(yīng)用程序的示例。一個(gè)示例是典型的蒙版,其中可能包含數(shù)十億個(gè)物理幾何形狀。必須創(chuàng)建掩模布局中的每個(gè)幾何圖形,設(shè)計(jì)自定義庫(kù),然后放置和布線,并將其組裝成完整的芯片。每種幾何形狀都必須經(jīng)過(guò)驗(yàn)證,以符合鑄造廠的制造要求,同時(shí)還要面對(duì)越來(lái)越多的復(fù)雜設(shè)計(jì)規(guī)則。對(duì)于現(xiàn)代設(shè)計(jì),單CPU運(yùn)行時(shí)間很容易超過(guò)數(shù)百小時(shí)。顯然需要并行處理。

兩種眾所周知的趨勢(shì)-設(shè)計(jì)復(fù)雜性和制造復(fù)雜性-每年都使挑戰(zhàn)變得更大。例如,從90納米(nm)遷移到65納米工藝節(jié)點(diǎn)的設(shè)計(jì)人員發(fā)現(xiàn)設(shè)計(jì)檢查的復(fù)雜性增加了3倍。過(guò)渡到45納米和40納米的過(guò)程更加復(fù)雜,因?yàn)橹圃旃に囎杂啥鹊慕档褪乖O(shè)計(jì)規(guī)則檢查(DRC)的設(shè)計(jì)和驗(yàn)證軟件變得更加復(fù)雜。復(fù)雜的線路末端以及通過(guò)由亞波長(zhǎng)光驅(qū)動(dòng)的配置規(guī)則光刻問(wèn)題就是很好的例證。現(xiàn)在,單個(gè)度量是規(guī)則,方程式或模型中包含的一組復(fù)雜度量。

由于需要并行設(shè)計(jì)和分析來(lái)避免設(shè)計(jì)進(jìn)度表的延遲,因此計(jì)算負(fù)擔(dān)更加復(fù)雜。進(jìn)行物理設(shè)計(jì)然后運(yùn)行單獨(dú)的物理驗(yàn)證階段也不再足夠。由于制造規(guī)則的復(fù)雜性,在物理設(shè)計(jì)過(guò)程中需要進(jìn)行所有層,規(guī)則和簽核檢查。如果不這樣做,在完成布局布線后,設(shè)計(jì)團(tuán)隊(duì)將清理DRC或布局與原理圖(LVS)錯(cuò)誤,這將導(dǎo)致代價(jià)高昂的設(shè)計(jì)延遲,從而在引入并發(fā)時(shí)增加了另一層次的復(fù)雜性。

最后,按時(shí)交付項(xiàng)目的需求至關(guān)重要-尤其是在今天,開(kāi)始的設(shè)計(jì)較少,掩膜成本較高且如果錯(cuò)過(guò)了市場(chǎng)窗口,財(cái)務(wù)后果將非常嚴(yán)重。

隨著復(fù)雜度的增加,設(shè)計(jì)時(shí)間必須保持恒定,如果不能改善的話(huà)。所有公司都希望事半功倍。

當(dāng)今的目標(biāo)設(shè)計(jì)是在40納米處,頂層具有1億個(gè)單元實(shí)例,并且具有內(nèi)存和模擬/混合信號(hào)內(nèi)容的混合。有效設(shè)計(jì)和驗(yàn)證的計(jì)算復(fù)雜度增加了6倍,這使得使用傳統(tǒng)流程幾乎無(wú)法完成65納米設(shè)計(jì)變得極為耗時(shí)。

交付解決方案需要新的軟件架構(gòu),該架構(gòu)必須具有靈活的靈活性,以實(shí)現(xiàn)跨大量CPU內(nèi)核的線性可伸縮性,以及強(qiáng)大的數(shù)據(jù)模型,可以在設(shè)計(jì)和驗(yàn)證之間進(jìn)行并發(fā)。

所需的解決方案

硬件供應(yīng)商面臨這樣的現(xiàn)實(shí),即由于功率限制而無(wú)法持續(xù)增加時(shí)鐘頻率,因此已經(jīng)采用并行機(jī)制來(lái)提高性能。考慮在多插槽主板中使用多核CPU。圖形處理器單元(GPU)是高度并行的單指令多數(shù)據(jù)(SIMD)機(jī)器,并且具有適當(dāng)?shù)膽?yīng)用程序編程接口(API)(例如NVIDIA的CUDA接口或AMD的ATIStream)是通用計(jì)算的潛在強(qiáng)大解決方案。

針對(duì)軟件供應(yīng)商的解決方案是有效地利用這些資源,這取決于軟件使用硬件的能力以可負(fù)擔(dān)的方式加速計(jì)算,也就是說(shuō),無(wú)需昂貴的定制硬件解決方案。當(dāng)需要大量?jī)?nèi)存,軟件被約束為只能在一臺(tái)計(jì)算機(jī)上運(yùn)行或者需要昂貴的自定義互連時(shí),會(huì)產(chǎn)生成本。

例如,可以以低于5,000美元的價(jià)格購(gòu)買(mǎi)配置合理的八核x86Linux計(jì)算機(jī),該計(jì)算機(jī)具有雙CPU和64GB內(nèi)存。將內(nèi)存占用空間增加到此之外是很昂貴的-達(dá)到128GB或更高的成本會(huì)使該基本配置的成本達(dá)到40,000美元或更高。

理想的解決方案將在標(biāo)準(zhǔn)配置(64GB)或低端配置(32GB或16GB)的四核或八核Linux計(jì)算機(jī)的標(biāo)準(zhǔn)網(wǎng)絡(luò)上線性擴(kuò)展。線性可伸縮性意味著在四臺(tái)計(jì)算機(jī)上運(yùn)行將比在兩臺(tái)計(jì)算機(jī)上運(yùn)行快4倍。幸運(yùn)的是,如今此類(lèi)Linux計(jì)算場(chǎng)很普遍,負(fù)載共享工具(LSF)或GRID分布式計(jì)算可用于動(dòng)態(tài)調(diào)度大量軟件應(yīng)用程序的作業(yè),從合成和電路仿真到物理設(shè)計(jì)和驗(yàn)證。

物理驗(yàn)證的參考解決方案

物理驗(yàn)證工具在設(shè)計(jì)的布局上執(zhí)行幾何分析,以驗(yàn)證可制造性。DRC是這些分析的很大一部分,一個(gè)簡(jiǎn)單的示例是檢查一根導(dǎo)線到另一根導(dǎo)線的間距。

傳統(tǒng)的物理驗(yàn)證工具依賴(lài)于標(biāo)準(zhǔn)的“數(shù)據(jù)庫(kù)”方法進(jìn)行此類(lèi)計(jì)算。該技術(shù)很簡(jiǎn)單-設(shè)計(jì)師以快速可搜索的數(shù)據(jù)結(jié)構(gòu)表示布局,并查詢(xún)相鄰的幾何形狀以檢查導(dǎo)線之間的距離。

跨多個(gè)CPU內(nèi)核加速這種類(lèi)型的計(jì)算似乎微不足道-設(shè)計(jì)人員可以并行計(jì)算許多導(dǎo)線的距離。實(shí)際上,如果所有CPU都在同一臺(tái)計(jì)算機(jī)上并且該計(jì)算機(jī)具有足夠的內(nèi)存來(lái)完全表示布局,則此方法可以很好地?cái)U(kuò)展。

不幸的是,設(shè)計(jì)的大小使得這兩個(gè)假設(shè)現(xiàn)在都無(wú)效。首先,如果規(guī)則復(fù)雜,則簡(jiǎn)單的分而治之的方法將不起作用。在65納米和45/40納米,基于連接的新檢查很常見(jiàn),以反映需要電連接以確保可制造性和可靠性。

其次,幾何形狀的數(shù)量使得一臺(tái)機(jī)器沒(méi)有足夠數(shù)量的CPU內(nèi)核來(lái)滿(mǎn)足周轉(zhuǎn)時(shí)間要求。通過(guò)計(jì)算,在標(biāo)準(zhǔn)Linux網(wǎng)絡(luò)上從一臺(tái)計(jì)算機(jī)到另一臺(tái)計(jì)算機(jī)查詢(xún)數(shù)據(jù)庫(kù)效率很低。

最后,布局?jǐn)?shù)據(jù)庫(kù)的大小(在許多40nm設(shè)計(jì)中為100GB以上)使得數(shù)據(jù)庫(kù)方法需要使用昂貴的高內(nèi)存硬件來(lái)使用此計(jì)算方法。有些工具需要256GB的計(jì)算機(jī)。

最近,計(jì)算機(jī)科學(xué)家宣傳了一種稱(chēng)為數(shù)據(jù)流或流架構(gòu)的不同方法。在進(jìn)行物理驗(yàn)證的情況下,布局不表示為數(shù)據(jù)庫(kù),而是表示為幾何流,這在很大程度上類(lèi)似于MP3文件是聲音流而不是音符集合。

流方法的優(yōu)點(diǎn)是它對(duì)多核,多CPU和多計(jì)算機(jī)設(shè)置友好。由于不再依賴(lài)于內(nèi)存數(shù)據(jù)庫(kù),因此處理核在何處不再重要-它們可以位于不同的裸片,不同的封裝,不同的主板或不同的機(jī)器上。

流架構(gòu)支持并行性,并行性可以從一個(gè)內(nèi)核擴(kuò)展到四個(gè)內(nèi)核,從16個(gè)內(nèi)核擴(kuò)展到64個(gè)內(nèi)核,甚至更高。作為獨(dú)立物理驗(yàn)證軟件的指南,需要在16個(gè)核上實(shí)現(xiàn)線性可擴(kuò)展性,以在65nm節(jié)點(diǎn)上實(shí)現(xiàn)有效的周轉(zhuǎn)時(shí)間。對(duì)于45/40-nm,需要32核到64核的可伸縮性,而有效的32/28-nm全芯片驗(yàn)證將需要128核。

第二個(gè)優(yōu)點(diǎn)是,由于沒(méi)有中央布局?jǐn)?shù)據(jù)庫(kù),流傳輸體系結(jié)構(gòu)的內(nèi)存使用率較低。正如大多數(shù)設(shè)計(jì)人員所知,即使將內(nèi)存使用量減少2倍,也可以使現(xiàn)有硬件的快速運(yùn)行與死機(jī)并需要昂貴的硬件升級(jí)或?qū)е螺^長(zhǎng)的計(jì)劃延遲之間產(chǎn)生差異。流技術(shù)使設(shè)計(jì)人員能夠?qū)⒋笮蛻?yīng)用程序用于需要大內(nèi)存的應(yīng)用程序(例如,簽核時(shí)序分析程序),并可以將標(biāo)準(zhǔn)硬件用于高效的流應(yīng)用程序。

第三個(gè)優(yōu)點(diǎn)是,即使在單個(gè)CPU內(nèi)核上,它們也可以比傳統(tǒng)數(shù)據(jù)庫(kù)方法更快地運(yùn)行。從本質(zhì)上講,數(shù)據(jù)庫(kù)方法涉及從CPU到主內(nèi)存數(shù)據(jù)庫(kù)的隨機(jī)查詢(xún)。計(jì)算機(jī)算法可以提高這種查詢(xún)的算法復(fù)雜度(例如O(logn),其中n是幾何數(shù))。CPU等待內(nèi)存請(qǐng)求返回的查詢(xún)速度受到阻礙-從L1緩存到L2緩存再到主內(nèi)存,甚至可能到磁盤(pán)交換。

流體系結(jié)構(gòu)使所有數(shù)據(jù)保持本地化(通常在CPU緩存限制之內(nèi)),這比獲取主內(nèi)存至少提供10倍的優(yōu)勢(shì)。盡管并非所有時(shí)間都在花費(fèi)EDA軟件來(lái)等待內(nèi)存提取,但很明顯,流技術(shù)可用于甚至提高單CPU效率。

流式架構(gòu)的一個(gè)缺點(diǎn)就是它的強(qiáng)度。因?yàn)闆](méi)有集中的內(nèi)存數(shù)據(jù)庫(kù),所以需要非本地化數(shù)據(jù)的操作可能會(huì)很復(fù)雜。例如,如果所需的計(jì)算是從設(shè)計(jì)中獲取兩個(gè)隨機(jī)對(duì)象,則假定數(shù)據(jù)已加載到內(nèi)存中,則大型存儲(chǔ)計(jì)算機(jī)上的數(shù)據(jù)庫(kù)方法將更快。

物理驗(yàn)證應(yīng)用程序-從DRC(包括基于天線和連接性的檢查,到LVS到電氣規(guī)則檢查),都可以進(jìn)行流計(jì)算。對(duì)于基于連接的操作(例如天線檢查或電壓相關(guān)的網(wǎng)絡(luò)檢查),每個(gè)網(wǎng)絡(luò)都可以可視化為相互連接的幾何流。

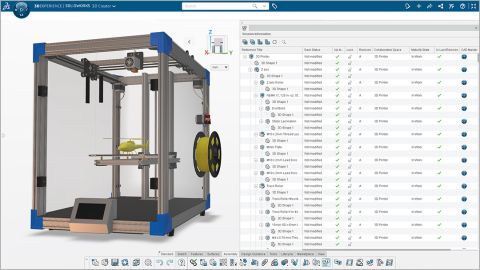

用于物理驗(yàn)證的流傳輸架構(gòu)的一個(gè)示例是Magma的QuartzDRC和QuartzLVS。與傳統(tǒng)的物理驗(yàn)證工具不同,Quartz是針對(duì)大型并行計(jì)算而編寫(xiě)的。大多數(shù)其他工具都依賴(lài)于在1980年代和1990年代設(shè)計(jì)該軟件時(shí)普遍適用于計(jì)算服務(wù)器環(huán)境的架構(gòu)。

在這里,CPU內(nèi)核的數(shù)量從一個(gè)或基線增加到64個(gè)。相對(duì)速度繪制在Y軸上。線性可擴(kuò)展的應(yīng)用程序遵循45度線-4倍于CPU數(shù)量4倍的速度。如圖所示,流工具可以在標(biāo)準(zhǔn)LSF環(huán)境中線性擴(kuò)展。相比之下,只要所有計(jì)算都可以在同一臺(tái)機(jī)器上完成,傳統(tǒng)的數(shù)據(jù)庫(kù)方法就可以合理地?cái)U(kuò)展。超過(guò)一定點(diǎn)后,可伸縮性就會(huì)減弱,并最終達(dá)到飽和,在這種情況下為8到16。

但是,流計(jì)算不是萬(wàn)能的。因?yàn)槲恢煤吐肪€是高度交互的并且涉及許多不同的服務(wù),從寄生建模到時(shí)序和噪聲分析,所以集中式數(shù)據(jù)結(jié)構(gòu)/數(shù)據(jù)庫(kù)是最有效的。對(duì)于此類(lèi)應(yīng)用,對(duì)算法設(shè)計(jì)的仔細(xì)關(guān)注也可以實(shí)現(xiàn)大規(guī)模并行性。

流計(jì)算的另一個(gè)挑戰(zhàn)是利用非傳統(tǒng)核心。在上面的示例中,Quartz使用IBM,Intel和AMD的微處理器中常見(jiàn)的標(biāo)準(zhǔn)CPU內(nèi)核。

NVIDIA和AMD的GPU中發(fā)現(xiàn)的專(zhuān)用內(nèi)核缺乏CPU內(nèi)核的通用計(jì)算能力。專(zhuān)用的EDA應(yīng)用程序已移植到GPU,包括英特爾在內(nèi)的圖形提供商的未來(lái)路線圖都指向功能更強(qiáng)大的GPU內(nèi)核。

責(zé)任編輯:tzh

-

處理器

+關(guān)注

關(guān)注

68文章

19259瀏覽量

229655 -

cpu

+關(guān)注

關(guān)注

68文章

10855瀏覽量

211592 -

eda

+關(guān)注

關(guān)注

71文章

2755瀏覽量

173207

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

eda在機(jī)器學(xué)習(xí)中的應(yīng)用

EDA在物聯(lián)網(wǎng)設(shè)計(jì)中的應(yīng)用

AI助力國(guó)產(chǎn)EDA,挑戰(zhàn)與機(jī)遇并存

云平臺(tái)在大規(guī)模設(shè)備管理和數(shù)據(jù)分析中的作用

AI+EDA加速雙向賦能,引領(lǐng)萬(wàn)物智能時(shí)代的創(chuàng)新

奧比中光攜最新3D視覺(jué)感知相機(jī)亮相日本最大規(guī)模AI展

PSoC63在CM0和CM4之間拆分BLE堆棧有什么好處?

購(gòu)買(mǎi)正版SOLIDWORKS軟件有哪些好處?

專(zhuān)用集成電路都是大規(guī)模的嗎為什么呢

為昕原理圖設(shè)計(jì)EDA軟件(Jupiter)試用

大規(guī)模數(shù)據(jù)中心網(wǎng)絡(luò)演進(jìn)的七大主流趨勢(shì)

eda工具軟件有哪些 EDA工具有什么優(yōu)勢(shì)

eda是什么軟件如何用

GGII預(yù)計(jì)2024快充大規(guī)模應(yīng)用元年將至

對(duì)話(huà)國(guó)產(chǎn)EDA和IP廠商,如何攻克大規(guī)模數(shù)字電路設(shè)計(jì)挑戰(zhàn)?

在EDA中運(yùn)用大規(guī)模軟件有什么好處?

在EDA中運(yùn)用大規(guī)模軟件有什么好處?

評(píng)論