描述了在實時嵌入式系統開發中遇到的與CACHE有關的問題?對引起這些問題的原因——CACHE和RAM的不一致性進行了討論?最后,提出了解決問題的方法?

隨著社會的發展?人們生活水平的提高,人們對嵌入式計算機應用的要求也越來越高?因此,對嵌入式系統的性能要求也越來越高?明顯體現在嵌入式系統的CPU速度的不斷提高上?但問題也隨之而來,嵌入式CPU的主頻不斷地提高,一方面加強了CPU的處理能力,另一方面,在速度上造成了與慢速的系統存儲器極不相配的情況,從而影響了整個系統的性能?

為了解決這個問題,引入了CACHE技術?CACHE是一種高速緩沖存儲器,是為了解決CPU和主存之間速度不匹配而采用的一項重要技術?通過在主存和高速CPU之間設置一個小容量的高速存儲器,在其中存放CPU常用的指令和數據,CPU對存儲器的訪問主要體現在對SRAM的存取,CPU可以不必加等待狀態而保持高速操作?

采用CACHE技術,解決了CPU與主存之間速度不匹配的問題;但它又帶來了一些其它問題,如本文將提到的一致性問題?

1 問題的發現與原因

在進行某嵌入式系統項目的開發過程中,有一個環節需要使用DMA方式進行數據傳輸?當程序運行后,發現傳到目的地的數據塊中經常會有一些錯誤的字節?如:數據本應為00 01 02 03 04 05 06 07 08 09 0A 0B 。..(16進制),結果卻是00 01 02 03 00 00 00 00 08 09 0A 0B 。..?在某些環節也出現了類似的問題?例如,通過HDLC通道向外發送數據,發送的總是緩沖區初始化時的內容,實際要發送的數據總是發不出去,但使用調試工具看內存中的數據,卻是正確的?

經過一段時間的調試,發現出現這種現象的環節都使用了DMA傳輸數據?在通過HDLC通道發送數據的例子中,HDLC通道內部也是用DMA方式從內存直接讀數據并向外發送?經過分析,認為問題的原因是出在CACHE上,是由于CACHE數據與內存數據的不一致性造成的?

所謂CACHE數據與內存數據的不一致性,是指:在采用CACHE的系統中,同樣一個數據可能既存在于CACHE中,也存在于主存中,數據一樣則具有一致性,數據若不一樣就叫做不一致性?具體表現在兩個方面:

(1)更新時可能CACHE中的數據更新,而主存未更新,則造成數據丟失;

(2)在有DMA控制器的系統和多處理器系統中,有多個部件可以訪問主存?這時,可能其中有些部件是直接訪問主存,也可能每個DMA部件和處理器配置一個CACHE?這樣,主存的一個區塊可能對應于多個CACHE中的一個區塊?于是會產生主存中的數據被某個總線部件更新過,而某個CACHE中的內容未更新,造成數據過時?

2 問題的分析

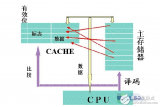

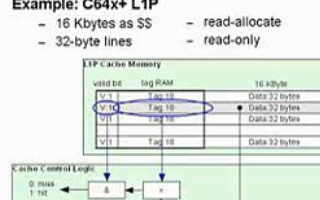

要解釋這個問題,首先要了解CACHE的工作模式?CACHE的基本工作模式有兩種:write-through模式和 copyback模式?在write-through模式下,所有的寫操作都寫入CACHE和RAM,保證了CACHE和RAM的一致?然而,每次對RAM都有寫操作會使處理器的處理能力降低,并且占用總線帶寬?在copyback模式下,寫操作只寫入CACHE,不寫入RAM,從而提高了處理器性能和總線帶寬?copyback模式下,CACHE中的內容只有在需要的時候才寫到RAM中?當CACHE中無可用空間時,一般使用最近最少使用算法(LRU)來決定哪一個CACHE項被替換?copyback模式提供了很高的系統性能,但是需要更多的一致性作保證?為了便于理解,給出一個使用了CACHE的系統的邏輯框圖,如圖1所示?

該系統中兩個地方會發生CACHE的不一致性:

(1)數據CACHE / RAM

數據CACHE與RAM之間的問題源于處理器和其他總線控制器對RAM的異步讀寫訪問?DMA設備和其他總線控制器對RAM的訪問是引起CACHE一致性問題的主要原因,這個問題可以通過在程序中加入一些代碼來解決?

(2)共享CACHE LINE

當一個CACHE LINE被兩個以上的線程共享時,也會產生一致性問題?當某個線程使一個CACHE LINE無效時,這個CACHE LINE中的一些項可能屬于另外一個線程?這個問題也可以通過一定的方法來避免,只要在分配內存時大小是CACHE LINE大小的整數倍即可?

在哈佛體系結構?copyback模式和無軟件干預的前提下,最佳的保持一致性的方法就是使用具有總線監聽能力的硬件?將CACHE?RAM?DMA設備和其它所有的總線主控設備都連到一個物理總線上,以使CACHE可以對該總線上的總線交互過程進行監聽,CACHE將對總線上的地址周期和控制(讀/寫)比特監聽,數據周期則被延遲到需要時才進行?當CACHE中的一項被一個異步操作修改時,該CACHE項就會被標為無效?如果處理器對一個已經被標為無效的CACHE項進行訪問時,CACHE就會從RAM中重新載入有效數據?在copyback模式下,處理器對CACHE進行寫操作時,RAM相應地址中的內容就變成過時?如果另外一個設備想訪問RAM中的這部分內容,CACHE就會搶占該訪問周期,將有效的數據寫入RAM?然后被搶占的訪問周期重新開始并將讀到RAM中的有效數據?但是,目前提供監聽能力的板子并不多?

3 解決的方法

根據上面的分析和討論,可見問題正是由數據CACHE / RAM的不一致性引起的?雖然關掉CACHE就可以解決一致性的問題,并且能夠減小程序開發的復雜度?但是一個高性能的系統是需要CACHE的,關掉CACHE會大大降低系統的性能?因此,本文僅討論在程序中加入代碼來克服一致性問題的方法?

可以采用以下幾種加入代碼的方法來解決一致性的問題?本文使用WIND RIVER公司的嵌入式實時多任務操作系統VxWORKS,下面的函數都是VxWORKS提供的 :

(1)對于時間上不是那么關鍵的程序段,可以先用下面的代碼維護數據CACHE的一致性?

cacheInvalidate DATA_CACHE address bytes

/ 輸入緩沖區/

。..

cacheFlush DATA_CACHE address bytes

/輸出緩沖區/

(2)對于時間上比較關鍵的程序段采用如下原則:在每次使用輸出緩沖區前將其更新;在每次使用輸入緩沖區前使其無效?

將緩沖區標示為“non-cacheable”可以防止一致性問題,這需要MMU支持?在分配緩沖區時,將其標示為“non-cacheable”即可?然而,動態緩沖區在釋放時要標為“cacheable”,否則內存總會產生大量的緩沖區碎片?

下面給出一個高性能的驅動程序例子,它把更新/無效的概念進行了擴展?不是對整個CACHE系統,而是對每一個緩沖區都這樣做?即通過分配對CACHE安全的緩沖區,在一個緩沖區的基礎上操作,從而防止了不需要的更新/無效操作?在這個例子中使用了CACHE庫中的函數cacheDMAMalloc? ,宏CACHE_DMA_INVALIDATE和CACHE_DMA_FLUSH實現一致性?在第4行調用函數cacheDMAMalloc 后,如果指針返回為非空,則說明分配到了一塊對于一致性問題來說是安全的緩沖區?

第7行驅動程序在緩沖區中寫入要傳給外部設備的數據,在第9行準備傳給外設之前,驅動程序必須更新數據CACHE以保證要傳的數據是在內存中,而不是在CACHE中?

當驅動程序準備讀外設傳給內存的數據,在第13行驅動程序處理這些數據之前,必須使數據CACHE中對應于輸入緩沖區的那部分無效以消除這些包含過時內容的條目?之后,驅動程序才能安全地處理從內存中取來的輸入數據?

1: STATUS drvExample pBuf

2: void pBuf / 緩沖區指針 /

3: { /*

4: pBuf = cacheDMAMalloc BUF_SIZE

5: if pBuf == NULL

6: return ERROR /內存分配失敗/

7: /其它初始化代碼和向發送緩沖區填數據/

8: CACHE_DMA_FLUSH pBuf BUF_SIZE

9: drvWrite pBuf /向外設發送數據/

10: …… / 其它代碼 /

11: drvWait /等待外設來的數據/

12: CACHE_DMA_INVALIDATE pBuf BUF_SIZE

13: / 處理外設來的數據 /

14: cacheDMAFree pBuf /釋放內存 /

15: return OK

16:}

責任編輯:gt

-

處理器

+關注

關注

68文章

19265瀏覽量

229670 -

嵌入式

+關注

關注

5082文章

19111瀏覽量

304845 -

存儲器

+關注

關注

38文章

7484瀏覽量

163769

發布評論請先 登錄

相關推薦

中央處理器與高速緩沖存儲器之間的聯系

高速緩沖存儲器的作用解析

高速緩沖存儲器的特點解說

高速緩沖存儲器的作用是什么_有什么特點

高速緩沖存儲器基礎知識詳細介紹

基于CACHE高速緩沖存儲器技術在嵌入式系統中的應用

基于CACHE高速緩沖存儲器技術在嵌入式系統中的應用

評論