不同類型的DMA

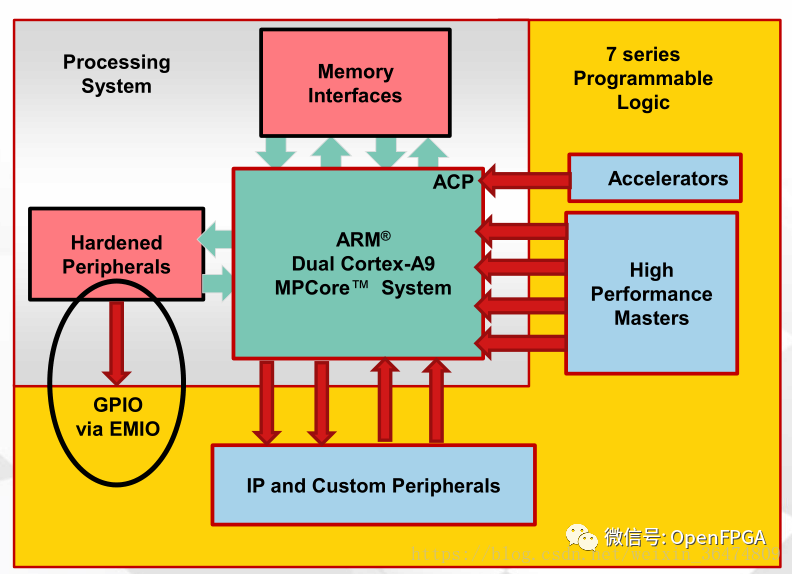

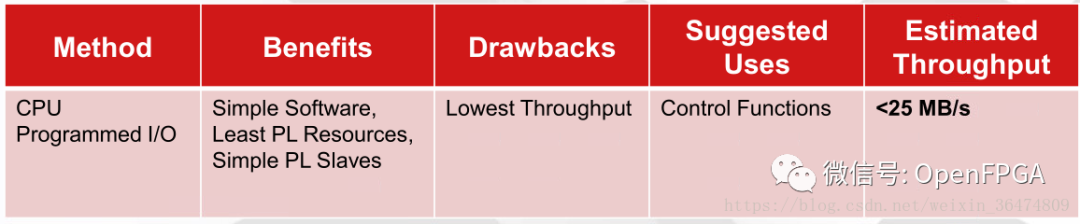

GPIO

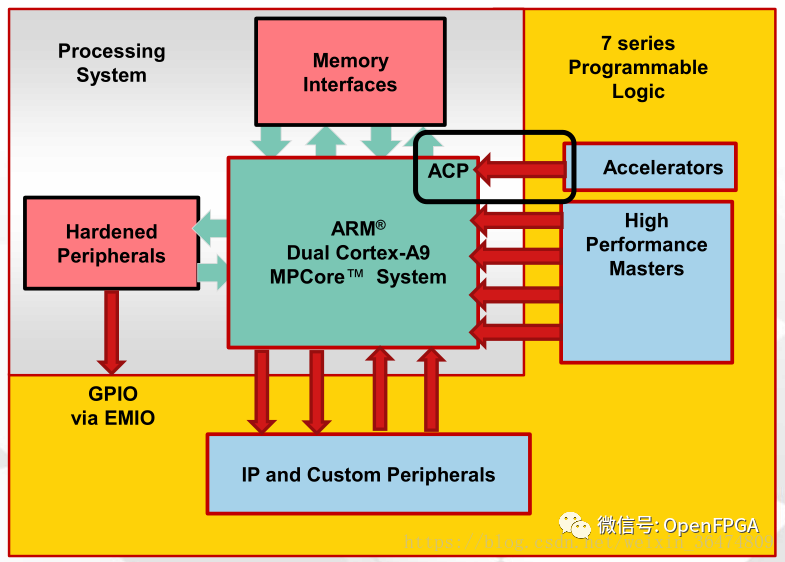

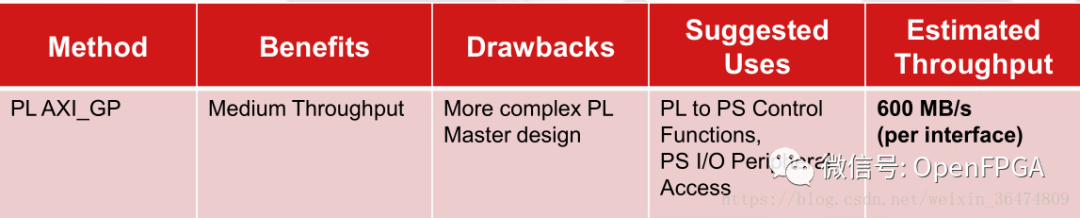

PL general purpose AXI

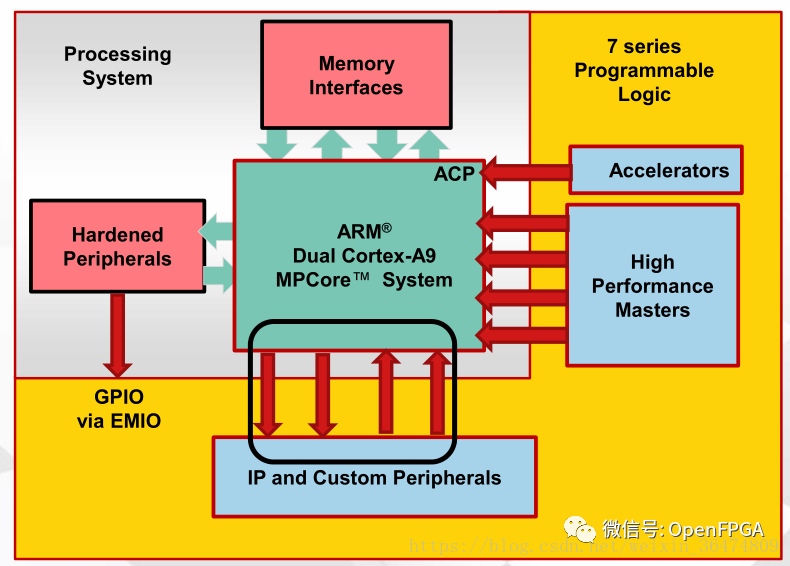

GP AXI utlilizing PS DMAC

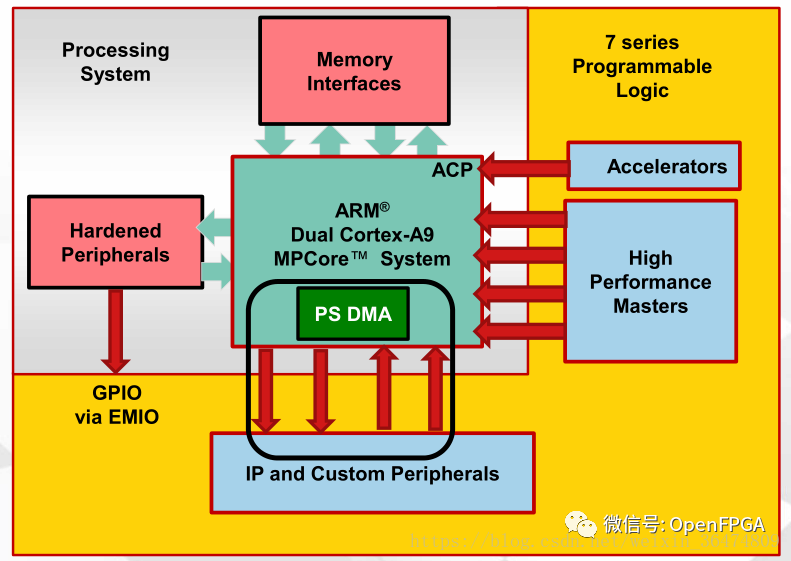

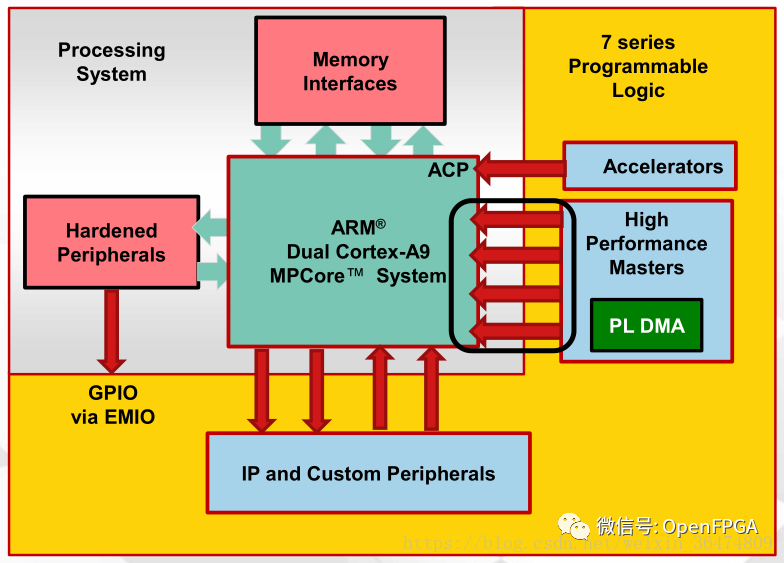

ACP w/DMA

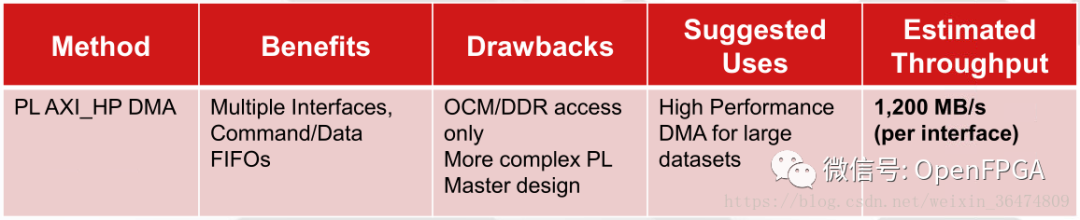

幾種DMA的總結(jié)

ZYNQ中不同應(yīng)用的DMA 幾個(gè)常用的 AXI 接口 IP 的功能(上面已經(jīng)提到): AXI-DMA:實(shí)現(xiàn)從 PS 內(nèi)存到 PL 高速傳輸高速通道 AXI-HP<---->AXI-Stream 的轉(zhuǎn)換 AXI-FIFO-MM2S:實(shí)現(xiàn)從 PS 內(nèi)存到 PL 通用傳輸通道 AXI-GP<----->AXI-Stream 的轉(zhuǎn)換 AXI-Datamover:實(shí)現(xiàn)從 PS 內(nèi)存到 PL 高速傳輸高速通道 AXI-HP<---->AXI-Stream 的轉(zhuǎn)換,只不過這次是完全由 PL 控制的, PS 是完全被動(dòng)的。 AXI-VDMA:實(shí)現(xiàn)從 PS 內(nèi)存到 PL 高速傳輸高速通道 AXI-HP<---->AXI-Stream 的轉(zhuǎn)換,只不過是專門針對(duì)視頻、圖像等二維數(shù)據(jù)的。 AXI-CDMA:這個(gè)是由 PL 完成的將數(shù)據(jù)從內(nèi)存的一個(gè)位置搬移到另一個(gè)位置,無需 CPU 來插手。 涉及到DMA主要包括AXI Centralized DMA、AXI Video DMA和AXI DMA,詳細(xì)的描述及IP核如下圖所示:

圖4?39 幾種DMA應(yīng)用 具體的描述如下表: 表4?19 幾種應(yīng)用DMA描述

| 類型 | 接口名稱 | 數(shù)據(jù)位寬 | 接口類型 | 功能描述 | 關(guān)鍵特性 |

| AXI Centralized DMA | control | 32 | AXI4-lite slave | CPU通過總線對(duì)DMA內(nèi)部的源地址寄存器、目的地址寄存器、控制寄存器、狀態(tài)寄存器和傳輸數(shù)據(jù)長度寄存器等進(jìn)行初始化。 | a兼容總線AXI4、AXI4-lite接口協(xié)議; bAXI4數(shù)據(jù)寬度支持32、64、128、256、512、1024; cAXI4-Stream 數(shù)據(jù)寬度支持8、16、32、64、128、256、512、1024; d可選的數(shù)據(jù)重組引擎; e獨(dú)立且異步的數(shù)據(jù)通道操作; g可選S/G模式傳輸和普通模式傳輸; h可選存儲(chǔ)轉(zhuǎn)發(fā)。 |

| Scatter/gather | 32 | AXI4 master | 從系統(tǒng)內(nèi)存讀取和更新DMA傳輸數(shù)據(jù)的配置信息,根據(jù)配置信息初始化CDMA傳輸參數(shù),執(zhí)行S/G傳輸模式;它卸載了CPU控制傳輸,實(shí)現(xiàn)硬件自動(dòng)化。 | ||

| data read | 32、64、128、256、512、1024 | AXI4 master | 根據(jù)源地址從系統(tǒng)內(nèi)存中讀取數(shù)據(jù)。 | ||

| data write | 32、64、128、256、512、1024 | AXI4 master | 根據(jù)目的地址向系統(tǒng)內(nèi)存中寫入數(shù)據(jù)。 | ||

| AXI Video DMA | control | 32 | AXI4-lite slave | 訪問VDMA內(nèi)部的寄存器,對(duì)DMA內(nèi)部的源地址寄存器、目的地址寄存器、控制寄存器、狀態(tài)寄存器和傳輸數(shù)據(jù)長度寄存器等進(jìn)行初始化。 | a 高帶寬直接存儲(chǔ)的視頻數(shù)據(jù)流; b 具有二維DMA傳送操作; c 獨(dú)立且異步讀取和寫入通道操作; d 同步耦合幀緩沖區(qū); e 支持最大32幀緩沖區(qū); f 支持動(dòng)態(tài)時(shí)鐘頻率的變化; g 配置突發(fā)傳輸數(shù)據(jù)的大小與行緩沖區(qū)的深度; h 處理器可訪問的初始化、中斷、狀態(tài)和管理寄存器; i 兼容AXI4、AXI4-lite、AXI4-stream接口協(xié)議; j 可選的S/G傳輸模式和普通模式傳輸。 |

| Scatter/gather | 32 | AXI4 master | 從系統(tǒng)內(nèi)存讀取和更新DMA傳輸數(shù)據(jù)的配置信息,根據(jù)配置信息初始化VDMA傳輸參數(shù),執(zhí)行S/G傳輸模式;它卸載了CPU控制傳輸,實(shí)現(xiàn)硬件自動(dòng)化。 | ||

| data memory mapped read(mm2s) | 32、64、128、256、512、1024 | AXI4 master | 根據(jù)源地址從系統(tǒng)內(nèi)存中讀取數(shù)據(jù)。 | ||

| data memory mapped write(s2mm) | 32、64、128、256、512、1024 | AXI4 master | 根據(jù)目的地址向系統(tǒng)內(nèi)存中寫入數(shù)據(jù)。 | ||

| data stream out | 8、16、32、64、128、256、512、1024 | AXI4-Stream master | 從VDMA側(cè)到兼容AXI4-Stream流接口的數(shù)據(jù)傳輸;數(shù)據(jù)位寬必須不大于data memory mapped 數(shù)據(jù)的位寬。 | ||

| data stream in | 8、16、32、64、128、256、512、1024 | AXI4-Stream slave | 從兼容AXI4-Stream流接口到VDMA側(cè)的數(shù)據(jù)傳輸;數(shù)據(jù)位寬必須不大于data memory mapped 數(shù)據(jù)的位寬。 | ||

| AXI DMA | Control | 32 | AXI-lite Slave | 訪問DMA內(nèi)部的寄存器,對(duì)DMA內(nèi)部的源地址寄存器、目的地址寄存器、控制寄存器、狀態(tài)寄存器和傳輸數(shù)據(jù)長度寄存器等進(jìn)行初始化。 | a 兼容AXI4-lite AXI4、AXI4-Stream總線接口協(xié)議; b 可選的普通傳輸模式和S/G模式; c 數(shù)據(jù)寬度可至1024; d 可選AXI控制流和狀態(tài)流; e 兩通道是獨(dú)立、全雙工的。 |

| AXI Memory Map Read Master | 32、64、 128、 256、512、 1024 | AXI4 Master | 根據(jù)源地址從系統(tǒng)內(nèi)存中讀取數(shù)據(jù)。 | ||

| AXI Memory Map write Master | 32、64、 128、 256、512、 1024 | AXI4 Master | 根據(jù)目的地址向系統(tǒng)內(nèi)存中寫入數(shù)據(jù)。 | ||

| Scatter/ Gather | 32 | AXI4 Master | 從系統(tǒng)內(nèi)存讀取和更新DMA傳輸數(shù)據(jù)的配置信息,根據(jù)配置信息初始化DMA傳輸參數(shù),執(zhí)行S/G傳輸模式;它卸載了CPU控制傳輸,實(shí)現(xiàn)硬件自動(dòng)化。 | ||

| Data Stream Out | 32、64、 128、 256、512、 1024 | AXI4- Stream Master | 從DMA側(cè)到兼容AXI4-Stream流接口的數(shù)據(jù)傳輸;數(shù)據(jù)位寬必須不大于data memory mapped 數(shù)據(jù)的位寬。 | ||

| Data Stream In | 32、64、 128、 256、512、 1024 | AXI4- Stream Slave | 從兼容AXI4-Stream的流接口到DMA側(cè)的數(shù)據(jù)傳輸;數(shù)據(jù)位寬必須不大于data memory mapped 數(shù)據(jù)的位寬。 | ||

| AXI Control Stream Master | 32 | AXI4- Stream Master | 控制memory to stream的數(shù)據(jù)流 | ||

| AXI Status Stream Slave | 32 | AXI4- Stream Slave | AXI4-Stream側(cè)傳入數(shù)據(jù)流的狀態(tài) |

責(zé)任編輯:xj

原文標(biāo)題:AXI總線詳解-不同類型的DMA

文章出處:【微信公眾號(hào):OpenFPGA】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

-

dma

+關(guān)注

關(guān)注

3文章

560瀏覽量

100548 -

AXI總線

+關(guān)注

關(guān)注

0文章

66瀏覽量

14261

原文標(biāo)題:AXI總線詳解-不同類型的DMA

文章出處:【微信號(hào):Open_FPGA,微信公眾號(hào):OpenFPGA】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

AMBA AXI4接口協(xié)議概述

【CAN總線知識(shí)】全面了解CAN總線協(xié)議

Xilinx NVMe AXI4主機(jī)控制器,AXI4接口高性能版本介紹

Linux項(xiàng)目開發(fā),你必須了解Systemd服務(wù)!

有關(guān)PL端利用AXI總線控制PS端DDR進(jìn)行讀寫(從機(jī)wready信號(hào)一直不拉高)

SoC設(shè)計(jì)中總線協(xié)議AXI4與AXI3的主要區(qū)別詳解

FPGA通過AXI總線讀寫DDR3實(shí)現(xiàn)方式

你以為的RAM不是你以為的RAM~

PCIe-AXI-Cont用戶手冊(cè)

PCIe控制器(FPGA或ASIC),PCIe-AXI-Controller

為什么有的RS485總線兩端必須安裝有源終端電阻?

漫談AMBA總線-AXI4協(xié)議的基本介紹

你必須了解的AXI總線詳解

你必須了解的AXI總線詳解

評(píng)論