單個LFPAK器件

本節將檢查影響單個LFPAK器件在不同配置的pcb上的熱性能的因素。從這一點開 始,當討論疊層或結構從器件中去除熱量的能力時,使用短語“熱性能”。為了全面了解影響熱性能的因素,我們將從最簡單的一層疊層的PCB開始,然后系統地向PCB中添加更多的層。

實驗設計1:單層PCB

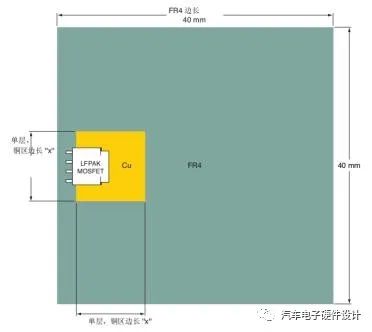

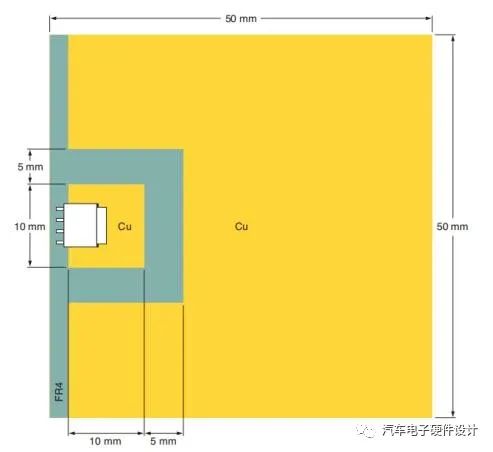

最簡單的PCB疊層是單層銅;一個一層層疊。在實驗設計1中,我們將檢驗器件結溫(Tj)隨頂層銅面積的變化。參見圖1。

圖1所示。單個的器件;一層層疊

圖1展示了MOSFET器件,該器件安裝在邊長為“x”的第一層銅的正方形區域上,

FR4的尺寸為40mmx40mm。與此布局相對應的三種可能的電路配置如圖2所示。

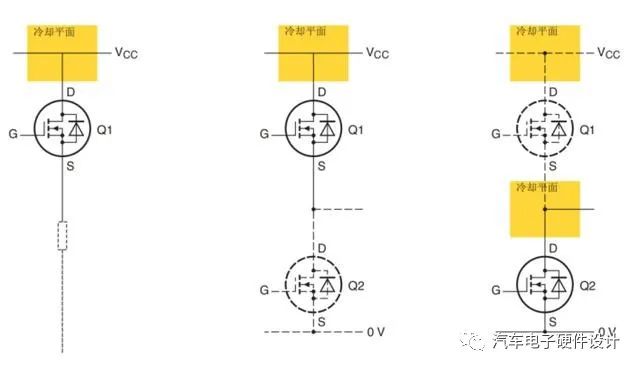

a.高邊負載開關設置:MOSFET

b.半橋設置:MOSFET,Q1和Q2

c.半橋設置:MOSFET,Q2和Q1

圖2所示。圖1布局的三種可能的電路配置。

圖2(a)顯示了MOSFET Q1配置為高邊負載開關,其漏極片連接到VCC平面(黃色)。圖2(b)和圖2(c)展示了MOSFETs Q1和Q2連接在半橋結構中。這兩種器件都是主要的通過連接到漏極的冷卻平面,盡管對于Q2來說,這個平面相當于半橋的中點,而不是電源平面。通過將平面附加到MOSFET源極上,還可以實現少量的額外冷卻,盡管源極引腳并不是從封裝中獲得的主要熱路徑,因此額外的好處是最小的。

一般來說,主要的熱路徑是通過封裝漏極片,進入任何連接到這個連接的平面,這是本指南中要考慮的配置。

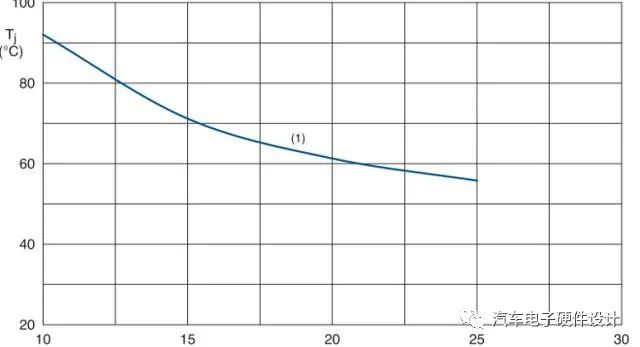

通過對不同尺寸的“x”進行實驗設計,我們可以確定器件結溫度(Tj)隨銅面積的變化情況。結果如圖3所示。記住環境溫度是20℃。

圖3所示。器件結溫度與第一層頂銅面邊長“x”

圖3的圖形有兩個顯著的特征:

?Tj在很大程度上取決于邊長“x”,即第1層銅的面積

?頂層銅為MOSFET提供加熱的能力顯示了“邊際遞減規律”。換句話說,我們不能為了繼續減少Tj而在第一層增加更多的銅面積。相反,從曲線的形狀我們可以得出這樣的結論:無論在第1層提供的多少銅面積,Tj永遠不會低于50℃。

第4.1.1節指出,實際上有兩個限制溫度不能超過:MOSFET的Tj和PCB材料的TPCB的溫度。對于表面安裝的MOSFETs,最大TPCB點通常出現在MOSFET漏極片上,正如人們可能期望的那樣。對于LFPAK封裝中的MOSFETs,TPCB通常會比Tj小0.5℃,因此我們可以合理地說TPCB≈Tj。這將對LFPAK封裝的其余實驗設計作出假設。

如果環境溫度保持在45℃以下,即使是第1層銅面積的較小區域也不會出現PCB降解的問題。

FR4尺寸對實驗設計的影響

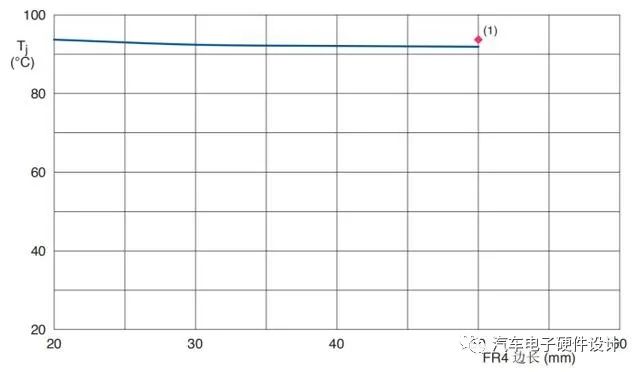

第4.3.1節中FR4 PCB面積的選擇可能看起來既隨意又不能代表實際應用中的PCB尺寸。然而,在這一節中,我們將看到光禿的FR4面積對器件(Tj)幾乎沒有影響。為了證明這一原理,我們對20mmx20mm、30mmx30mm、50mmx50mm的FR4尺寸進行了額外的實驗設計,第1層銅面積固定在10mmx10mm。結果如圖4所示。

圖4:結溫與FR4邊長

圖4的結果表明裸FR4的尺寸對器件Tj幾乎沒有影響。這與圖3的結果形成了鮮明的對比,在圖3中我們改變了第1層銅面積。當我們比較時,兩組結果之間的差異很容易理解銅和FR4的熱導率;銅的導熱系數約為380w /(m.K),而FR4的導熱系數僅為0.6W/(m.K)。由于熱導率是一種衡量熱量如何輕易地通過一種物質的指標,因此很明顯,即使是增加大面積的FR4(這是一種糟糕的熱導體)也遠不如增加更小面積的高導熱銅有效。我們可以通過在模型中添加1層銅的不連通區域來進一步說明FR4的絕緣特性,如圖5所示。

圖5:在50mm×50mm FR4板上增加一層銅

圖5顯示了50mm×50mm的FR4布局,其中1層大部分區域都充滿了大量的銅。在器件周圍留下了5mm的間隙,其封裝為10mmx10mm的銅面積。雖然我們可能已經預料到額外的第1層銅會對器件Tj造成重大影響,但事實并非如此。由于設備周圍的隔離間隙和中間FR4的導熱性差,熱能無法利用額外的“散熱”區域。FR4以這種方式“隔離”熱源的能力很重要,將在第4.4節“兩個LFPAK器件”和第4.5節“四個LFPAK器件”中再次實驗設計。

責任編輯人:CC

-

pcb

+關注

關注

4354文章

23421瀏覽量

406842 -

LFPAK

+關注

關注

0文章

4瀏覽量

7778

原文標題:PCB熱設計之實驗設計1

文章出處:【微信號:QCDZYJ,微信公眾號:汽車電子工程知識體系】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

PCB提高中高功耗應用的散熱性能

PCB熱設計概述

PCB外殼對PCB熱設計的影響因素

研究不同的模式對PCB設計熱性能的影響

不同的PCB和器件配置對熱行為的影響

an-2026PCB設計簡單開關電源模塊的熱性能的影響

評論