封裝是將芯片的“裸芯”通過膜技術及微細加工技術,固定在框架或基板上,完成粘貼及連接,通過引出接線端子,完成對外的電器互聯。隨著集成電路產業的發展,流片加工工藝越來越先進,單片集成度越來越高,引出端數目也越來越多,傳統四周排布 PAD 的方式,無論是 in-line 或是 stagger,都可能無法滿足間隔要求。同時,很多大規模電路功耗較大、所集成的外設速率越來越高,例如高速 SERDES 接口,傳輸速率高達 12.5GHz,致使傳統的引線鍵合(wire bond)封裝技術,由金線帶來的寄生參數無法滿足設計指標要求,從而必須采用倒裝焊封裝技術手段,來滿足較多的引出端數目、較大的供電能力,以及超高的速率要求。

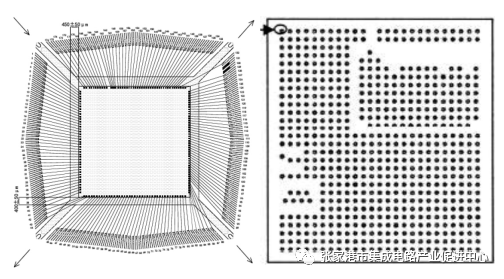

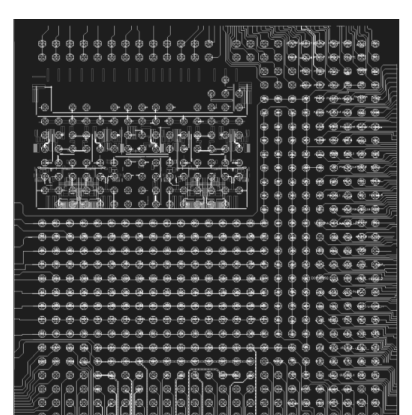

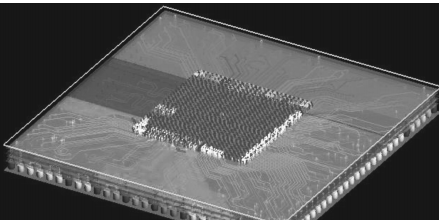

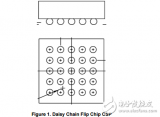

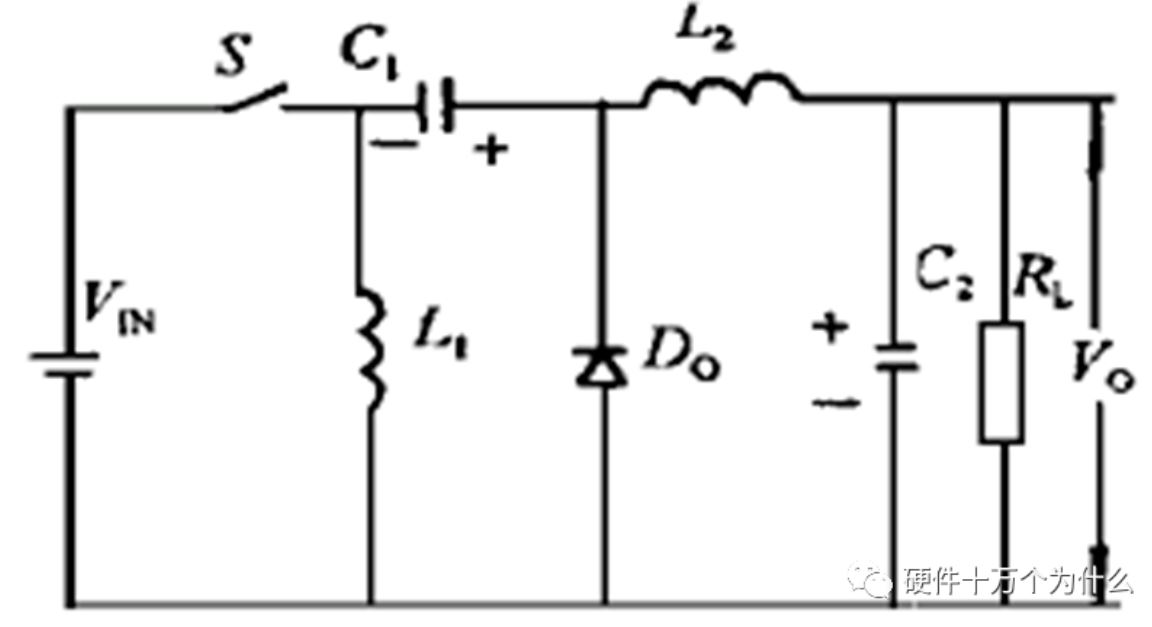

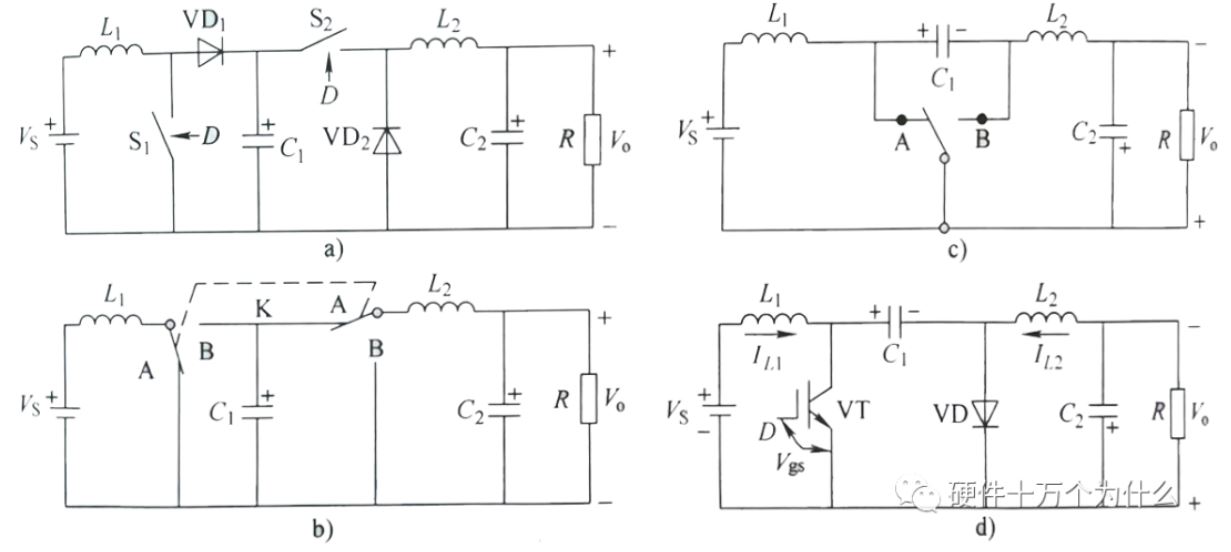

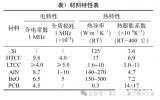

Wire bond 封裝和倒裝焊封裝的區別,一是,前者引出端為四周引出方式,倒裝焊封裝的引出端為內部二維矩陣排布,二者的封裝鍵合圖如圖 1 所示。

圖 1 引線封裝和倒裝焊封裝示意圖

二是,倒裝焊封裝由四周排布擴展至二維矩陣排布,從而使得引出端數量大幅增加,理論引出端數量對比見表 1。

表 1 封裝技術引出端理論數量對比

待封裝的是一顆超大規模集成電路芯片,集成了 12.5Gbps 高速 Serdes 硬核,DDR 硬核,LVDS 接口,以及業務處理所需的數據接口。實現工藝為中芯國際(SMIC)65nm,面積達到了 7000 mm×7500mm,管芯引出端數量接近 700 個,封裝形式為 CBGA272。

由于整個芯片封裝過程中,需要物理版圖工程師、Foundry 工程師,與封裝廠商三部分高度協同設計。不同身份的設計師,在數據交互時,各自理解不同,容易產生工作冗余迭代,影響效率。所以,將芯片封裝過程所涉及的工作內容進行了梳理,展開來進行闡述。

管芯設計內容

此部分主要工作由物理版圖設計師完成,針對倒裝焊設計與傳統引線鍵合設計的區別進行了闡述。

1)版圖布局設計

如圖 2 所示,倒裝焊封裝的 IO 雖然是二維矩陣式(area-IO)排布,但需要注意的是在物理設計時,引出端可以依舊選擇四周排布的方式(peripheral-IO)。

圖 2 芯片 TOP 層版圖

例如本芯片集成的 Serdes 核為硬核形式,IP 設計師給出了圖形信息以供走線互連。其他部分的 IO 將按照傳統布局方式進行連接。另外,由于本芯片功耗未超過 1W,壓降效果不明顯,故無需像 FPGA 管芯的設計,從內部做垂直形狀的 IO。

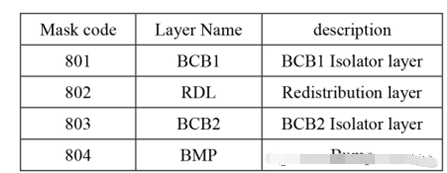

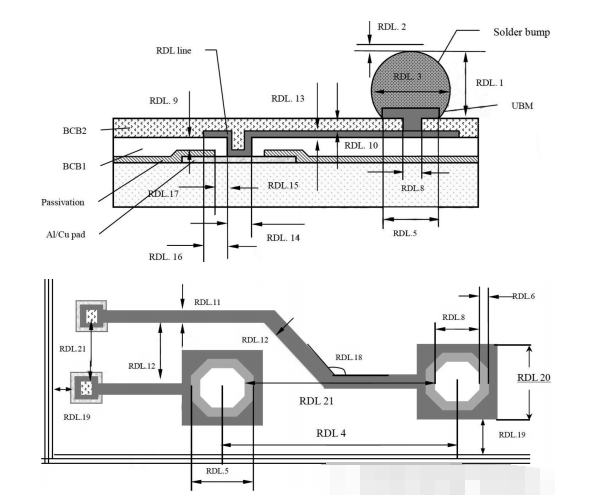

2)重布線層設計

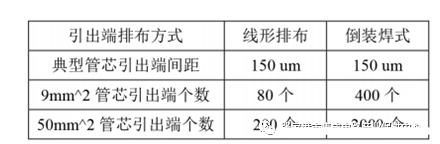

重布線層(RDL,Redistribute Layer)。其為倒裝焊設計獨有的層,用來對管芯引腳重新走線,最大化的增加引出端數量。在 SMIC 65nm 加工工藝中,重布線層的掩膜板層命名見表 2。

表 2 SMIC 掩膜板代碼和層命名規則

在設計時,需要參考 SMIC 的設計規則,主要規則如表 3 和圖 3 所示。

表 3 SMIC RDL 層布線規則

圖 3 RDL 層設計規則圖

表 3 顯示了具體規則數值。例如 RDL 布線間距(trace space)不得小于 12um,每個 bump 間距(bump pitch)不得小于 150um 等等規則。

本芯片的目標設計時,結合 BGA272 的封裝形式,其 RDL 層布線如圖 4 所示。

圖 4 芯片 RDL 層版圖

完成了整個重布線層版圖設計,形成了最終的 GDSII 文件,就可以提交流片數據。

3)版圖數據提交

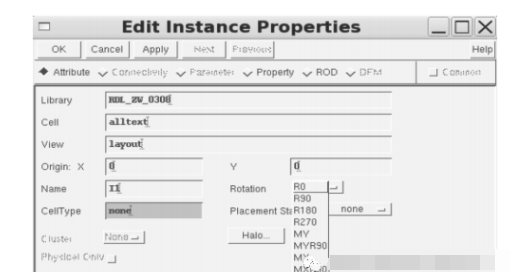

圖 5 顯示了版圖工具中翻轉、鏡像的設置界面,基此,單顆管芯設計完成后,要提交的版圖數據包括:一是需要整理出整顆管芯的尺寸,每個引出端的坐標,是否預留了劃片道等信息。二是將該信息交付到流片工程師,完成整版的拼版,此時需要注意的是倒裝焊由于是“倒裝”的焊接到基板上,需要特別注意是否存在版圖鏡像、翻轉的操作。

圖 5 版圖工具中翻轉、鏡像的設置界面

封裝設計內容

1)封裝信息交互

當完成了目標的 RDL 設計之后,就可以提交流片廠商進行 Wafer 的加工生產了,并進行相關封裝信息交互。流片廠商會反饋各種信息,其中有些是需要提供給后道封裝的。包括晶片初始厚度、目標減薄厚度,劃片道寬度、焊盤尺寸與開口尺寸等信息。

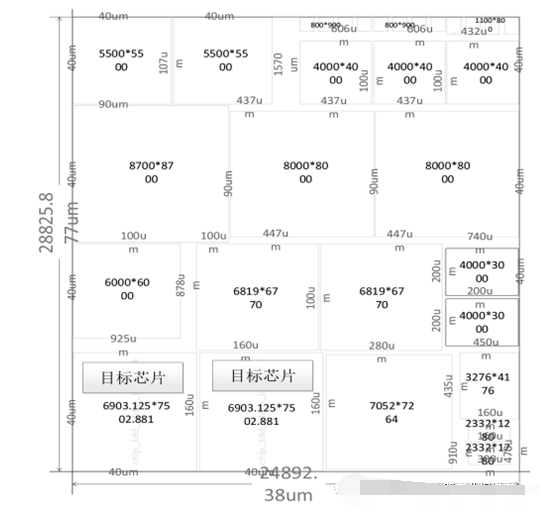

2)UBM 層制作注意事項

凸塊底部金屬(UBM)層一般為第三方加工廠制作,需要基于整張 Wafer 進行 MASK 設計,需要精度較高的 Floorplan 圖(見圖 6),以及倒裝焊目標芯片的 IO 坐標。將在版圖中測量出的間距信息提供至 UBM 廠商,完成 0.01um 級別精度的 MASK 制作。

圖 6 UBM 廠商所需的 layout 圖

3)基板及外殼制作內容

圖 7 是基板走線示意圖,從中看出,基板(substrate)設計,與高速 PCB 設計規則類似,主要需要考慮電地及信號的走線,避免串擾,盡可能的降低層數,以便節省成本。

圖 7 基板走線示意圖

完成了基板設計,如圖 8 所示,要結合封裝形式進行仿真。

圖 8 封裝仿真模型

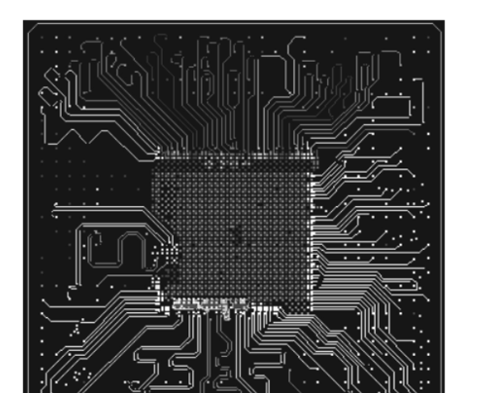

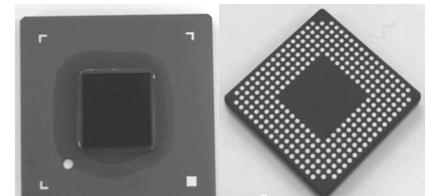

4)封裝芯片成品

最終完成封裝形式為 CBGA272 的倒裝焊封裝的芯片實物(見圖 9),完成了 bump 植柱,未植焊接球。

圖 9 芯片實物照片

總結

毫無疑問,技術沒有先進和落后一分,只有是否適用于當前產品。倒裝焊封裝設計復雜度較高,帶來了更長的設計周期,增加了研發成本;加工步驟的增多,帶來了生產成本的增加;先進的片內封裝技術,例如 UBM、基板,都需要進行錫料焊接,虛焊等因素導致良率降低,并且測試排查手段只能通過 X 光進行觀測,反饋迭代周期、成本都較長。

當決定采用倒裝焊封裝后,每個環節的銜接交互都需要格外謹慎,保障芯片最終達到設計目標。

責任編輯人:CC

-

芯片

+關注

關注

459文章

51778瀏覽量

431579 -

封裝

+關注

關注

128文章

8220瀏覽量

144161

發布評論請先 登錄

相關推薦

倒裝芯片和晶片級封裝技術及其應用

Flip-Chip倒裝焊芯片原理與優點

倒裝芯片CSP封裝

評論