現代電子設計和芯片制造技術正在飛速發展,電路的復雜度、元器件布局以及布線密度、開關速度、時鐘和總線頻率等各項指標參數都呈快速上升趨勢。當上升時間超過傳輸延時的1/6時,反射、串擾、振蕩以及傳輸線效應等涉及到的時序、信號完整性(SI)、EMI等一系列問題決定著產品設計的成敗。特別是DDR2系統,可支持高達9.6 GB/s的帶寬(FB-DIMMs),時鐘頻率高達0.9 GHz,高速DDR2系統的信號完整性和時序問題,己經成為設計能否成功的關鍵因素之一。因此,在印制電路板(PCB)設計完成之前,運用仿真工具對PCB進行板級的信號完整性仿真和時序分析,進行分析和設計的優化,可以發現調試過程中可能產生的問題,從而可節約成本、縮短產品的設計周期。

1 模型的選取

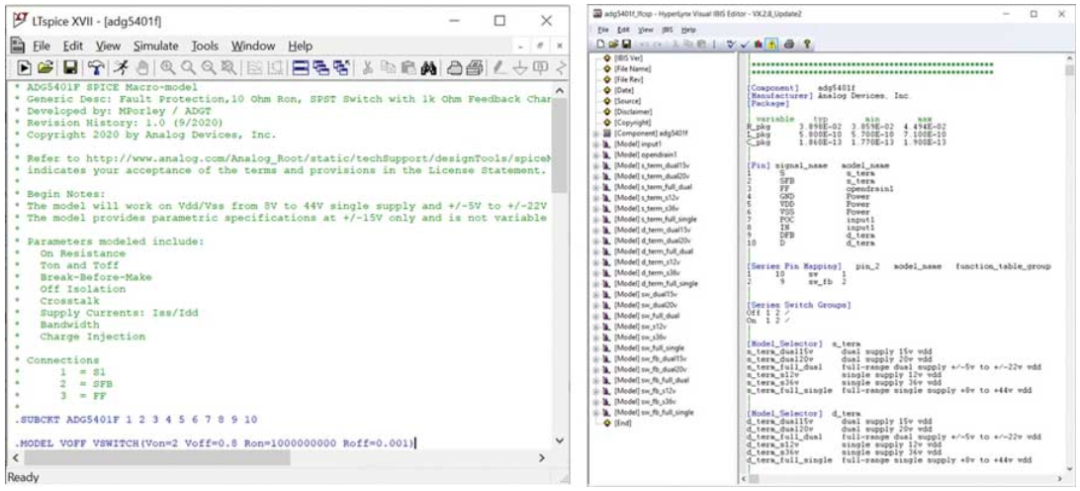

在基于計算機分析信號完整性和時序分析的過程中,建立實際驅動IC的模型十分關鍵。目前主要有三種可以用于PCB板級信號完整性分析的模型:SPICE模型、IBIS模型和AMS模型。

IBIS模型由于采用IN和V/T表的形式來描述I/O單元和引腳的特性,不但方便易得,而且不依賴于不同的仿真工具,計算量較小。

SPICE模型需要IC廠商提供詳細、準確描述I/O單元的內部設計和晶體管制造參數這些涉及到知識產權的機密數據,所以SPICE模型不易獲取。其分析精度主要取決于模型參數的來源(即數據的精確性)以及模型方程式的適用范圍。使用不同仿真工具進行SPICE模型仿真時,會產生不同的分析精度。

AMS建模語言與IBIS模型同樣也是數據形式來描述IC的特性,可以應用在多種不同類型的仿真工具中。AMS模型在PCB板級信號完整性分析中的可行性和計算精度毫不遜色于SPICE和IBIS模型,但目前支持的仿真工具還不是很多。

綜合比較上述三種模型,由于IBIS模型的方便、快捷、具有必要的精確度以及精度不依賴于仿真工具的優點,本文選取IBIS模型進行仿真。

2 仿真工具的選取

Mentor公司推出的仿真工具其功能十分強大,Hyperlynx可進行多電路板分析,包括趨膚效應、電介質損耗效應、損耗傳輸線效應的精確模擬,具有數千兆位信號的內部符號干擾圖表分析功能;可為多位激勵源、抖動、眼圖和眼罩定義區域;可以建立隨頻率變化的過孔模型而進行分析;進行差分信號模擬和分析來對包括差分阻抗和不同終端負載的優化;Terminator Wizard能夠分析并計算出使用包括串聯終端、并聯、并聯交流電和差分最佳的終端方案;通過輻射法和傳輸線電流分析來發現EMC故障問題;支持所有的PCB布線和布局程序。

Hyperlynx還可方便地采用IBIS或HSPICE模型進行仿真,自帶7 000個通用IC模型庫,或根據數據簿信息運用可視化IBIS編輯器允許測試和編輯IBIS模式來創建用戶的模型。Hyperlynx還具有界面友好、方便易用的優點。綜合Hyperlynx的優點,本文選取Hyperlynx進行仿真分析。

3 設計實例

下面給出應用Hyperlynx7.7前仿真工具Linesim和級仿真工具Boardsim利用IBIS模型對基于MIPS架構的XLS606 CPU的信號線進行分析。

CPU的最大外頻為1 GHz,內存選用Micron公司的DDR2-800,信號線走中間層,參考上下兩層地,因為信號工作頻率達到400 MHz,故布線密度大,很容易出現信號完整性問題。

布線前仿真可以根據PCB對信號完整性的要求,幫助設計者合理布置元器件、規劃系統時鐘網絡以及確定關鍵線網的端接策略。在布線過程中跟蹤設計,隨時反饋布線效果,確定PCB布線的約束規則,如參數設置和布線約束等(這里不詳細敘述)。

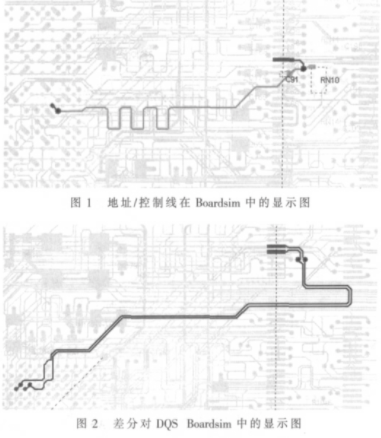

在運用CAD設計工具設計得出具有關鍵元件布局和關鍵網絡的走線的基本元素的PCB后,綜合考慮如電氣、電磁兼容性(EMC)等因素對信號完整性(SI)的影響以及這些因素之間的相互作用,從而進行Boardsim布線后的仿真分析與驗證。下面選取一些重要的DQ、DQS、MA網絡進行分析。在進行完整PCB的布線后,可以通過Boardsim導入PCB文件。圖1為地址/控制線在Boardsim中的顯示圖,圖2為差分對DQS在Boardsim中的顯示圖。

在相關網站上下載該處理器和該型號內存的IBIS模型。根據JESD79-2C DDR2 SDRAM SPECIFICATION的說明要求,可以知道地址/命令/控制信號以及DQS差分對或時鐘信號的DC和AC工作標準對DDR2-800要求如表1所示。根據上述指標可以得出眼圖的數據,然后設置疊層編輯器來設置特性阻抗值,導入CPU以及存儲器的IBIS模型,根據實際設計設置網絡中上拉電阻以及濾波電容的實際值,可以讀出有效特性阻抗值Z0=54.3 Ω,以及每位周期的值。因為信號頻率為400 MHz,所以每位周期設置為1.25 ns。

從圖3眼圖可以看出,信號在不同DIMM內部和外部的信號質量是不同的,在沒有端接電阻以及布線、阻抗調整的情況下,運行400 MHz的頻率信號十分差,眼圖的寬度、高度、上升斜率等關鍵指標都不符合JEDEC對DDR2-800的DC/AC規范。

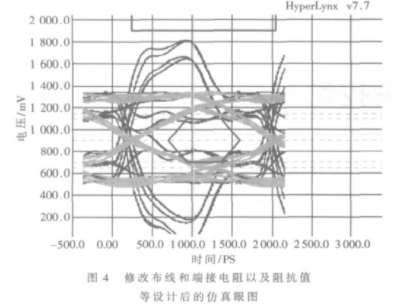

圖4為修改Layout布線和端接電阻以及阻抗值等設計后的仿真眼圖,從圖4可以明顯直觀地看到,修改之后信號狀況大大改觀,而且可以直接讀出眼寬、高電平值、低電平值、采樣眼寬等信號眼圖的重要數據,以便于確定硬件和PCB設計。

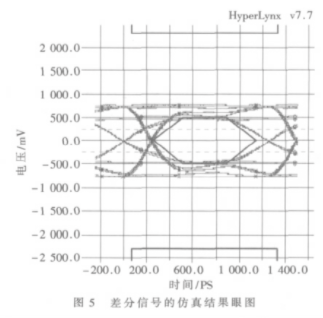

同理,可以對重要的差分信號和時鐘信號進行仿真。而DDR2中新增加的ODT(On Die Termintation)功能在仿真中可以得到體現。通過不設置以及設置ODT的值,可以直觀地在眼圖以及客觀地在仿真結果數據一欄中得出合成差分信號的質量。圖5為差分信號的仿真結果眼圖。

通過眼圖和數據,可以確定最優差分阻抗和ODT值的設置。

高速信號的PCB優化設計,可以在PCB的設計階段,運用Hyperlyxn仿真工具和IBIS驅動模型,對高速信號設計中的關鍵信號進行完整性仿真和時序分析、EMI仿真、分析和優化,可以發現PCB制好后調試中可能出現的問題,從而可以節約成本、縮短產品的設計時間。

責任編輯:gt

-

pcb

+關注

關注

4324文章

23159瀏覽量

399330 -

元器件

+關注

關注

112文章

4746瀏覽量

92718 -

仿真

+關注

關注

50文章

4124瀏覽量

133875

發布評論請先 登錄

相關推薦

基于HyperLynx VX.2.4的IBIS-AMI仿真測試臺構建方案

阻抗匹配中的Hyperlynx應用

IBIS 模型

請問有人知道IBIS模型怎么使用嗎?

高速互連IBIS仿真模型概述

Hyperlynx仿真:Xilinx官網下的Ibis模型里面怎么沒有引腳的編號

在Hyperlynx中使用Xilinx Artix IBIS模型時,IO模型不可選是怎么回事

hyperlynx問題討論

求助,請發送在Hyperlynx軟件中進行SI分析所需的IBIS模型

AN4803 在STM32微控制器上使用IBIS高速SI仿真和使用HyperLynx-SI進行板級仿真

能否利用器件的IBIS模型對器件的邏輯功能進行仿真?

巧用SPICE與IBIS,為您的電路仿真選擇更合適的模型

基于Hyperlynx仿真工具和IBIS驅動模型實現系統設計

基于Hyperlynx仿真工具和IBIS驅動模型實現系統設計

評論