LTE(Long Term Evolution)是3GPP展開的對UMTS技術(shù)的長期演進(jìn)計(jì)劃。LTE具有高數(shù)據(jù)速率、低延遲、分組傳送、廣域覆蓋和向下兼容等顯著優(yōu)勢,在各種“準(zhǔn)4G”標(biāo)準(zhǔn)中脫穎而出,最具競爭力和運(yùn)營潛力。運(yùn)營商普遍選擇LTE,為全球移動(dòng)通信產(chǎn)業(yè)指明了技術(shù)發(fā)展的方向。設(shè)備制造商亦紛紛加大在LTE領(lǐng)域的投入,其中包括華為、北電、NEC和大唐等一流設(shè)備制造商,從而有力地推動(dòng)LTE不斷前進(jìn),使LTE的商用相比其他競爭技術(shù)更加令人期待。

Turbo碼以其接近香農(nóng)極限的優(yōu)異糾錯(cuò)性能被選為LTE標(biāo)準(zhǔn)的信道編碼方案之一。對Turbo編譯碼器進(jìn)行FPGA集成設(shè)計(jì),能夠加速LTE的商用步伐,具有廣闊的應(yīng)用前景。在不同的信道環(huán)境中,通信系統(tǒng)對信息可靠性和數(shù)據(jù)實(shí)時(shí)性具有不同的指標(biāo)要求,實(shí)際應(yīng)用中必須對二者進(jìn)行適當(dāng)折中。因此,硬件設(shè)計(jì)一種糾錯(cuò)性能與譯碼時(shí)延可靈活配置的Turbo碼編譯碼器更具商業(yè)價(jià)值。

Altera公司推出的功率優(yōu)化、性能增強(qiáng)的Stratix III系列產(chǎn)品采用了與業(yè)界領(lǐng)先的Stratix II系列相同的FPGA體系結(jié)構(gòu),含有高性能自適應(yīng)邏輯模塊(ALM),支持40多個(gè)I/O接口標(biāo)準(zhǔn),具有業(yè)界一流的靈活性和信號完整性。Stratix III FPGA和Quartus II軟件相結(jié)合后,為工程師提供了極具創(chuàng)新的設(shè)計(jì)方法,進(jìn)一步提高了性能和效能。Stratix III L器件邏輯單元較多,為幀長可配置Turbo碼編譯碼器的FPGA設(shè)計(jì)提供了便利條件。

Turbo碼的誤碼性能在很大程度上取決于信息幀長,信息幀越長,譯碼性能越好,代價(jià)是譯碼延時(shí)的增大。基于這一點(diǎn),本設(shè)計(jì)提出一種幀長可配置的Turbo碼編譯碼器的FPGA實(shí)現(xiàn)方案,詳細(xì)介紹了該系統(tǒng)中交織器的工作原理,并對時(shí)序仿真結(jié)果和功能實(shí)現(xiàn)情況進(jìn)行了分析,為LTE標(biāo)準(zhǔn)下Turbo編譯碼專用集成芯片的開發(fā)提供了參考。

1 幀長可配置的Turbo編譯碼器的系統(tǒng)結(jié)構(gòu)

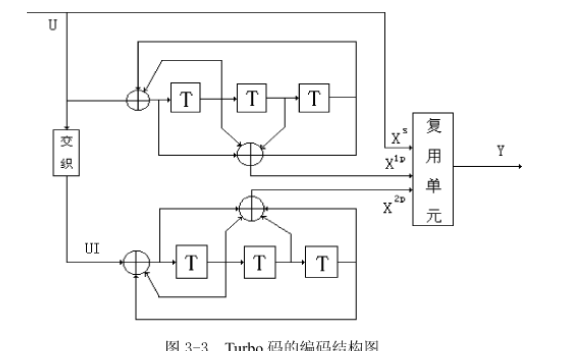

LTE標(biāo)準(zhǔn)中,信道編碼主要采用Tail Biting(咬尾)卷積碼和Turbo編碼兩種方案。其中Turbo碼碼率為1/3,由兩個(gè)生成多項(xiàng)式系數(shù)為(13,15)的遞歸系統(tǒng)卷積碼(RSC)和一個(gè)QPP(二次置換多項(xiàng)式)隨機(jī)交織器組成,采用典型的PCCC編碼結(jié)構(gòu)。

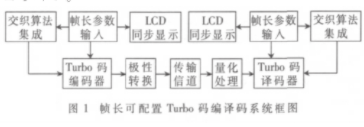

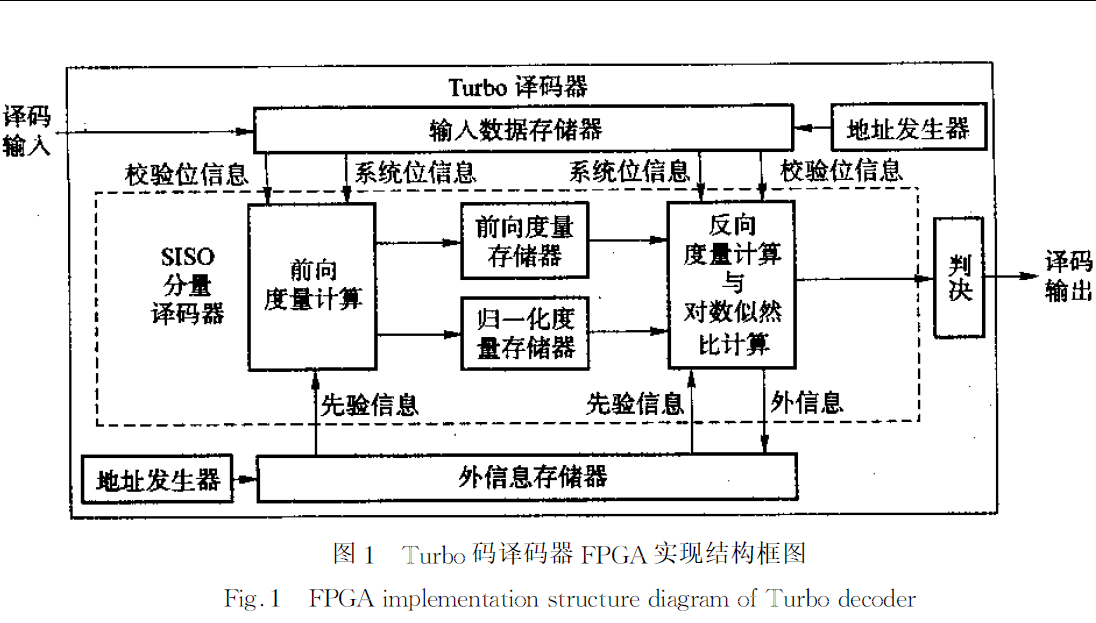

根據(jù)Turbo碼編譯碼結(jié)構(gòu)原理可知,信息幀長關(guān)鍵取決于交織深度的大小,如果交織器能夠根據(jù)不同幀長參數(shù)自動(dòng)植入不同的交織圖樣,并對其他模塊進(jìn)行相應(yīng)參數(shù)控制,即可實(shí)現(xiàn)設(shè)計(jì)功能。由此得到可配置Turbo編譯碼器的設(shè)計(jì)思想:在編譯碼之前,由鍵盤電路輸入信息幀長,系統(tǒng)據(jù)此對編譯碼器進(jìn)行初始化,主要包括設(shè)置電路中存儲(chǔ)器的深度,計(jì)算、存儲(chǔ)交織圖樣,并通過LCD同步顯示幀長信息;初始化過程結(jié)束時(shí)輸出狀態(tài)標(biāo)志位,編譯碼器進(jìn)入準(zhǔn)備狀態(tài),一旦有數(shù)據(jù)輸入,即啟動(dòng)編譯碼流程。由此得到Turbo編譯碼器系統(tǒng)結(jié)構(gòu)圖如圖1所示。

圖1的Turbo碼編譯碼器中,所有有關(guān)信息長度的參數(shù)均設(shè)置為輸入變量,包括存儲(chǔ)器深度、計(jì)數(shù)器周期等,以方便配置。

2 FPGA功能模塊的設(shè)計(jì)與實(shí)現(xiàn)

2.1 交織模塊的設(shè)計(jì)

交織器是Turbo編譯碼器的主要構(gòu)成部分之一,其能否根據(jù)幀長參數(shù)產(chǎn)生相應(yīng)的交織圖樣也是本設(shè)計(jì)的關(guān)鍵所在。LTE標(biāo)準(zhǔn)中規(guī)定交織器采用QPP偽隨機(jī)交織方案,交織長度范圍為40“6 114,該方案對不同幀長產(chǎn)生不同的交織圖樣,能夠有效改善碼字的漢明距離和碼重分布。假設(shè)輸入交織器的比特序列為d0,d1,…,dK-1,其中K為信息序列幀長,交織器輸出序列d′0,d′1,…,d′K-1。則有:

參數(shù)f1和f2取決于交織長度K,具體值可參見參考文獻(xiàn)。

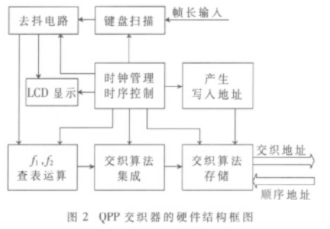

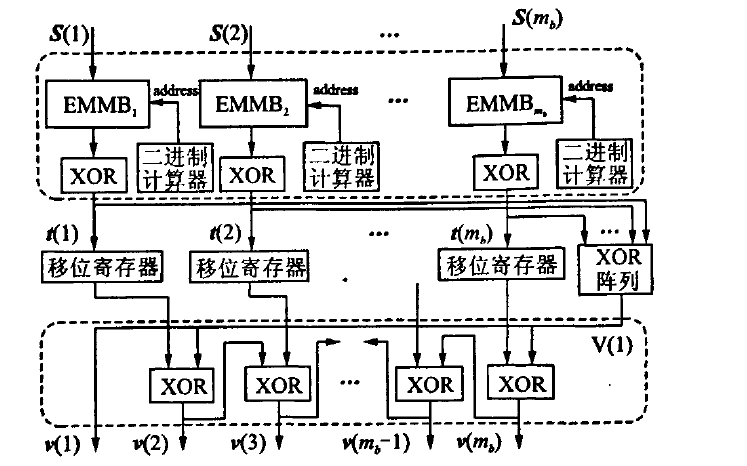

傳統(tǒng)交織器的FPGA設(shè)計(jì)一般采用軟件編程的方法。根據(jù)通信協(xié)議,將所確定幀長的交織圖樣預(yù)先計(jì)算出來,生成存儲(chǔ)器初始化文件(.mif或.hex格式)載入到ROM中。這樣雖然降低了硬件復(fù)雜度,卻不能自行配置編碼幀長,缺乏靈活性和通用性。因此,設(shè)計(jì)中將交織算法集成于FPGA內(nèi)部,需要改變信息幀長時(shí)啟動(dòng)交織器重新計(jì)算交織地址存儲(chǔ)于RAM中。QPP交織器的硬件結(jié)構(gòu)框圖如圖2所示。

圖2中,在系統(tǒng)初始化階段,由鍵盤電路采集輸入的信息幀長K,經(jīng)消抖處理,一路傳輸給LCD同步顯示模塊,另一路傳送到f1、f2運(yùn)算單元,查表得到f1、f2的值,提供給交織算法集成模塊。

交織算法集成單元是交織器設(shè)計(jì)的核心部分。主要功能是根據(jù)LTE協(xié)議標(biāo)準(zhǔn)以及參數(shù)K、f1、f2,在時(shí)序控制模塊的約束下,計(jì)算交織地址。運(yùn)算過程中,將FPGA不能綜合的對任意整數(shù)取余的運(yùn)算,均轉(zhuǎn)化為固定次數(shù)的加減循環(huán)操作,在時(shí)鐘管理模塊的控制下,采取小時(shí)鐘計(jì)算、大時(shí)鐘輸出的措施,保證交織數(shù)據(jù)的正確讀取。

計(jì)算交織地址的同時(shí)產(chǎn)生寫入地址,將交織地址順序存儲(chǔ)到雙口RAM中,由此完成了交織器的主體設(shè)計(jì)。隨后發(fā)送握手信號,可以開始Turbo碼編譯碼流程。

因?yàn)椴⒉皇敲繋畔⒕幾g碼時(shí)都需要運(yùn)行交織算法模塊,所以只是在初始化階段載入交織地址,使交織算法與編譯碼器分時(shí)工作。調(diào)用交織器模塊時(shí)只需將順序地址輸入到雙口RAM的讀地址端,便能得到既定幀長的QPP偽隨機(jī)交織地址,不會(huì)增加譯碼延時(shí)。得到交織圖樣以后即可進(jìn)行交織、解交織過程。

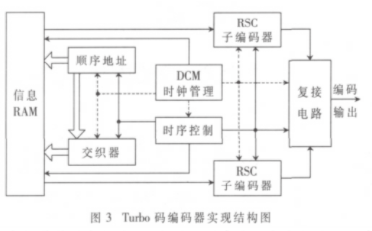

2.2 Turbo碼編碼器的設(shè)計(jì)

在完成交織模塊的基礎(chǔ)上對Turbo碼編碼器進(jìn)行FPGA設(shè)計(jì)。Turbo碼編碼器由RSC(遞歸系統(tǒng)卷積碼)子編碼器、交織器、復(fù)接電路等構(gòu)成,硬件實(shí)現(xiàn)框圖如圖3所示。

系統(tǒng)初始化完畢后,交織器已存儲(chǔ)有對應(yīng)幀長的交織圖樣,編碼器首先接收到一幀信息存儲(chǔ)于RAM中,開始信號啟動(dòng)編碼過程。在時(shí)鐘管理模塊和時(shí)序控制模塊的指引下,計(jì)數(shù)器產(chǎn)生順序地址,再按該順序地址訪問交織器得到交織地址,分別以順序地址和交織地址從存儲(chǔ)有信息序列的RAM中讀取數(shù)據(jù)進(jìn)入對應(yīng)的RSC進(jìn)行編碼,同時(shí)復(fù)接電路對信息位和校驗(yàn)位進(jìn)行并串轉(zhuǎn)換,一幀信息編碼完畢對子編碼器做歸零處理。

2.3 Turbo碼譯碼器的設(shè)計(jì)

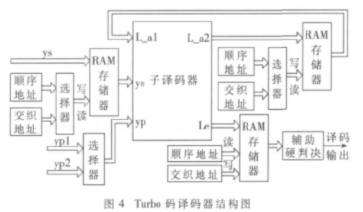

Turbo碼譯碼器相對于編碼器來說硬件結(jié)構(gòu)更加復(fù)雜,根據(jù)譯碼原理和交織器實(shí)現(xiàn)方式,得到譯碼器實(shí)現(xiàn)結(jié)構(gòu)圖如圖4所示。

為節(jié)省硬件資源,本文設(shè)計(jì)的Turbo碼譯碼器采用子譯碼器單核復(fù)用的結(jié)構(gòu)模式。當(dāng)子譯碼器模塊作為子譯碼器1時(shí),信息比特順序?qū)懭氪鎯?chǔ)器后順序讀出到子譯碼器中,L_a2以交織地址寫入存儲(chǔ)器,順序地址讀出作為子譯碼器1的先驗(yàn)信息,同時(shí)校驗(yàn)位選擇yp1,子譯碼器1根據(jù)3個(gè)輸入進(jìn)行SISO(軟輸入軟輸出)譯碼運(yùn)算,得到新的L_a2及L_e;此后子譯碼器作為子譯碼器2,以交織地址將ys從存儲(chǔ)器中讀出,L_a2以順序地址寫入存儲(chǔ)器,交織地址讀出作為子譯碼器2的先驗(yàn)信息,同時(shí)校驗(yàn)位選擇yp2,子譯碼器2根據(jù)3個(gè)輸入進(jìn)行SISO(軟輸入軟輸出)譯碼運(yùn)算,得到新的L_a2及L_e,完成一次迭代。在滿足迭代停止準(zhǔn)則以后,將L_e解交織后進(jìn)行硬判決,得到譯碼序列。

設(shè)計(jì)中,子譯碼器采用復(fù)雜度與性能折中的Max-Log-MAP譯碼算法。根據(jù)輸入的信息位、校驗(yàn)位及先驗(yàn)概率信息,在時(shí)序控制模塊的管理下,分別進(jìn)行分支轉(zhuǎn)移度量、前向狀態(tài)度量、后向狀態(tài)度量和對數(shù)似然比的計(jì)算及存儲(chǔ),以備下次譯碼運(yùn)算調(diào)用。

依據(jù)初始化分支轉(zhuǎn)移度量值,由(13,15)RSC的籬笆圖,找出當(dāng)前時(shí)刻前向狀態(tài)度量與前一時(shí)刻前向狀態(tài)度量的對應(yīng)關(guān)系,計(jì)算當(dāng)前時(shí)刻的前向狀態(tài)度量。依次遞推,為防止數(shù)據(jù)溢出范圍,每次迭代對其進(jìn)行歸一化處理,得到實(shí)現(xiàn)框圖如圖5所示。后向狀態(tài)度量與前向狀態(tài)度量具有相似的運(yùn)算結(jié)構(gòu),只是逆向遞推而已。

由對數(shù)似然比的定義,將得到的分支轉(zhuǎn)移度量、前向狀態(tài)度量和后向狀態(tài)度量代入運(yùn)算公式,對3種輸入?yún)⒘窟M(jìn)行組合運(yùn)算,然后取出“1”路徑8種狀態(tài)中的最小值和“0”路徑8種狀態(tài)的最小值,做差即得到Max-Log-MAP算法中的對數(shù)似然比。迭代數(shù)次后進(jìn)行輔助硬判決,解交織輸出即為傳回信宿的譯碼序列。

3 系統(tǒng)實(shí)現(xiàn)與仿真結(jié)果分析

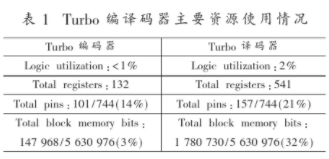

在Quartus Ⅱ開發(fā)工具上,以Stratix III 系列的EP3-SL150F1152C2為配置平臺,用Verilog HDL語言對上述各功能模塊進(jìn)行編程建模,調(diào)試統(tǒng)一后編譯綜合,得到編譯碼器主要硬件資源占用情況如表1所示。

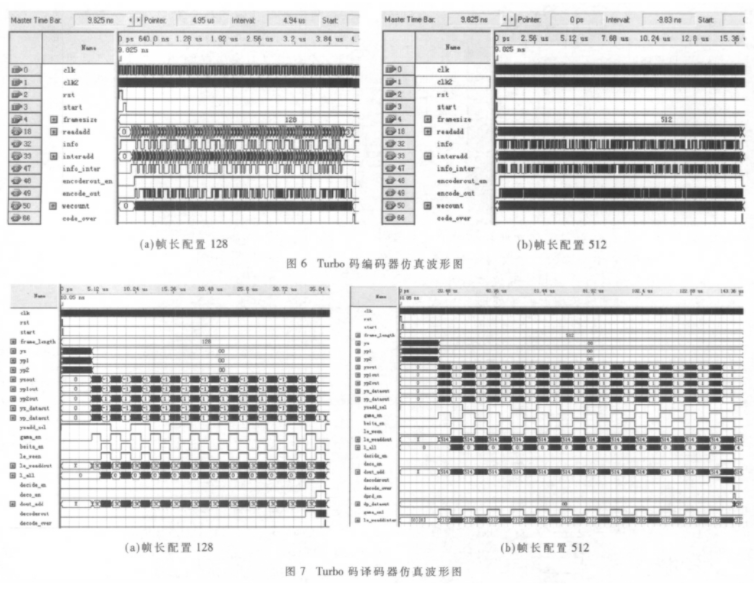

建立波形文件,分別對Turbo碼進(jìn)行時(shí)序仿真,得到信息幀長分別配置為128、512時(shí),Turbo碼編碼器的仿真波形如圖6(a)、圖6(b)所示。‘’

圖6中,每幀碼字序列的結(jié)尾,都有12個(gè)系統(tǒng)尾比特,以使編碼器寄存器回歸全零狀態(tài)。經(jīng)多次驗(yàn)證,與Matlab仿真數(shù)據(jù)進(jìn)行對比,結(jié)果正確。

將編碼碼字量化后存儲(chǔ)于ROM中,提供給譯碼器進(jìn)行時(shí)序仿真,得到信息幀長分別配置為128、512(碼字序列長度分別為396、1 548)時(shí),Turbo碼譯碼器的仿真波形如圖7(a)、圖7(b)所示。

圖7中,譯碼器首先根據(jù)幀長設(shè)置初始化交織圖樣,然后對系統(tǒng)碼字解復(fù)接,得到信息序列(ys)、校驗(yàn)位1(yp1)及校驗(yàn)位2(yp2),與外信息(L_all)一起輸入子譯碼器進(jìn)行SISO譯碼運(yùn)算,迭代6次以后判決得到譯碼結(jié)果(decoderout)。

設(shè)置不同的信息幀長,經(jīng)多次仿真驗(yàn)證,均能正確實(shí)現(xiàn)編譯碼功能。將程序下載配置到EP3SL150F1152C2中,利用VC軟件編寫測試窗口,進(jìn)行測試。結(jié)果顯示,本設(shè)計(jì)可以利用外圍鍵盤電路自行輸入幀長,進(jìn)行交織運(yùn)算,得到交織圖樣,并能正確實(shí)現(xiàn)Turbo編譯碼功能,達(dá)到了設(shè)計(jì)要求。

本設(shè)計(jì)以LTE為應(yīng)用背景,實(shí)現(xiàn)了一種可根據(jù)信道環(huán)境現(xiàn)場配置幀長的Turbo編譯碼的硬件方案。將QPP交織算法集成于FPGA內(nèi)部,充分利用其時(shí)鐘頻率高、速度快的優(yōu)勢,減小了外圍接口電路消耗。在系統(tǒng)初始化時(shí)進(jìn)行交織運(yùn)算,先于Turbo編譯碼進(jìn)程開始,兩者分時(shí)工作,協(xié)調(diào)統(tǒng)一,不會(huì)帶來額外的時(shí)延。所實(shí)現(xiàn)的Turbo碼編譯碼器是一種比較理想的通用型方案,為LTE標(biāo)準(zhǔn)下Turbo編解碼專用集成芯片的開發(fā)與推廣提供了參考。

責(zé)任編輯:gt

-

FPGA

+關(guān)注

關(guān)注

1630文章

21783瀏覽量

605023 -

存儲(chǔ)器

+關(guān)注

關(guān)注

38文章

7524瀏覽量

164147 -

譯碼器

+關(guān)注

關(guān)注

4文章

312瀏覽量

50405

發(fā)布評論請先 登錄

相關(guān)推薦

基于IP核的Viterbi譯碼器實(shí)現(xiàn)

急求基于FPGA的Turbo碼編譯碼器各模塊實(shí)現(xiàn)的 VHDL或verilog HDL程序

怎么設(shè)計(jì)Turbo簡化譯碼算法的FPGA?

突發(fā)通信中的Turbo碼編譯碼算法的FPGA實(shí)現(xiàn)

怎么實(shí)現(xiàn)BCH譯碼器的FPGA硬件設(shè)計(jì)?

怎么實(shí)現(xiàn)RS編譯碼器的設(shè)計(jì)?

基于Nios的通用編譯碼器的設(shè)計(jì)

LTE標(biāo)準(zhǔn)下Turbo碼編譯碼器的集成設(shè)計(jì)

短幀Turbo譯碼器的FPGA實(shí)現(xiàn)

基于FPGA的高速RS編譯碼器實(shí)現(xiàn)

基于FPGA 的LDPC 碼編譯碼器聯(lián)合設(shè)計(jì)

基于Turbo碼編譯碼算法的FPGA實(shí)現(xiàn)突發(fā)數(shù)據(jù)通信

Turbo碼的編譯碼基本原理和常用編譯碼算法分析及仿真程序

如何使用FPGA實(shí)現(xiàn)結(jié)構(gòu)化LDPC碼的高速編譯碼器

如何使用FPGA實(shí)現(xiàn)跳頻系統(tǒng)中的Turbo碼譯碼器

幀長可配置Turbo編譯碼器的系統(tǒng)結(jié)構(gòu)和應(yīng)用設(shè)計(jì)和實(shí)現(xiàn)

幀長可配置Turbo編譯碼器的系統(tǒng)結(jié)構(gòu)和應(yīng)用設(shè)計(jì)和實(shí)現(xiàn)

評論