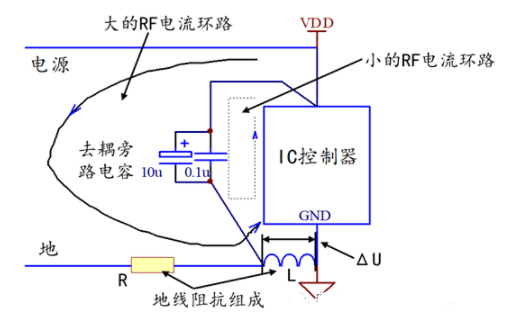

我們不時聽到客戶提出一個很好的問題。將去耦電容器放置在目標(biāo)IC附近是否重要?一般的經(jīng)驗法則是這樣說的,每個PCB設(shè)計者都知道這一點,甚至經(jīng)驗不足。

但是,在現(xiàn)實生活中的布線實踐中,通常很難在機(jī)械限制和電氣需求之間找到可接受的折衷方案。特別是如果我們不講幾個簡單的片狀電容器或一個低功率軌。如果是帶有50-100個去耦電容器的BGA封裝的FPGA或PHY怎么辦?

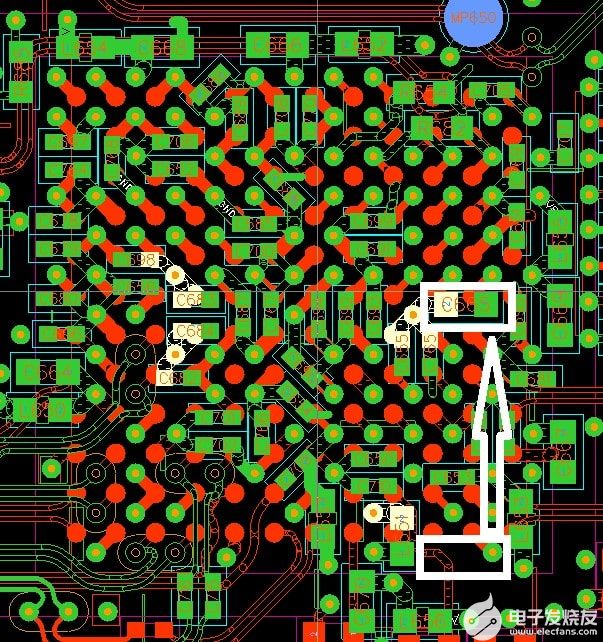

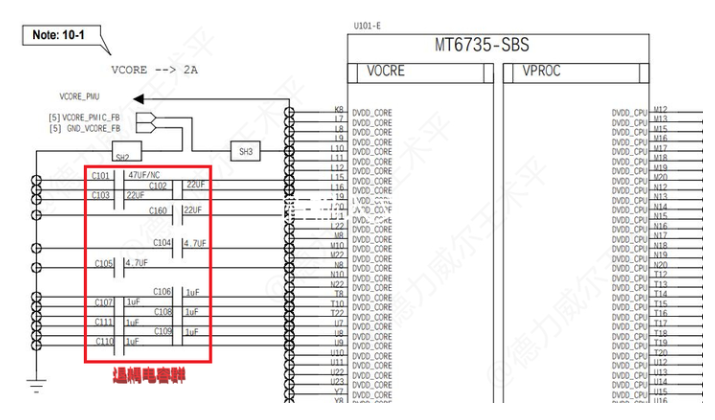

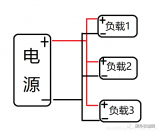

不久前,我們的工程師正在處理一個復(fù)雜的PCB項目,其中除其他外,還提出了這樣一個意想不到的挑戰(zhàn)。板上有一個帶有60個去耦電容器的10G以太網(wǎng)PHY。布局設(shè)計師試圖實現(xiàn)最高質(zhì)量的設(shè)計,他設(shè)法將幾乎所有電容器都非常靠近板背面IC的相應(yīng)引腳。但不是所有人。在這種情況下,通常將較小封裝和電容的電容器直接放置在引腳附近,而稍大一些的電容器則要稍遠(yuǎn)一些,但要盡可能接近電路板上的情況。因此,這是在給定項目中解決問題的方式:

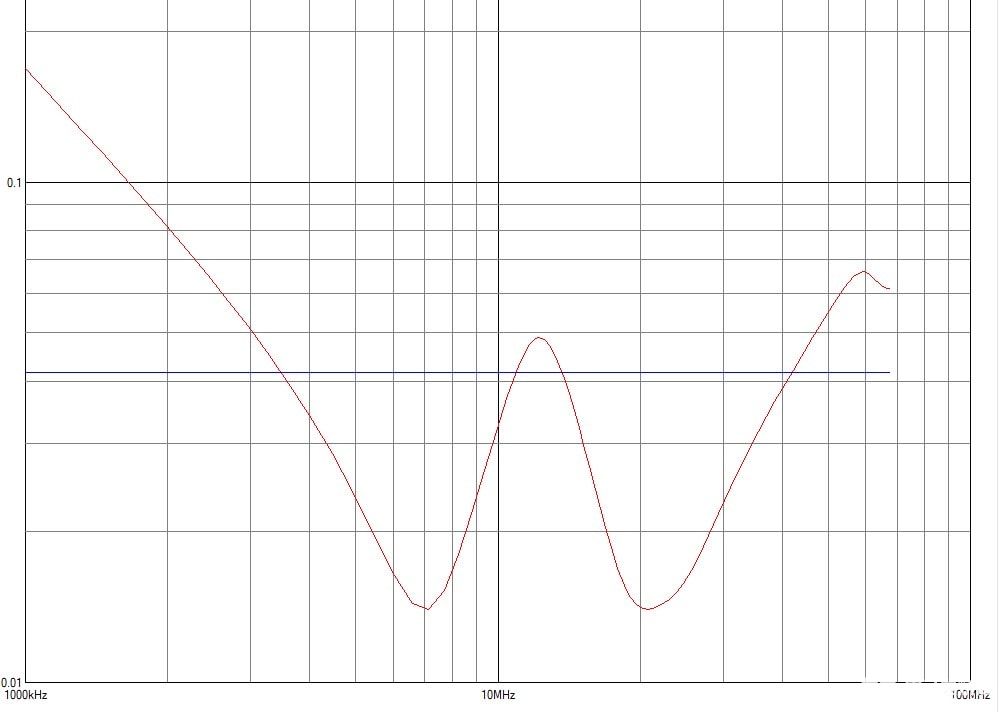

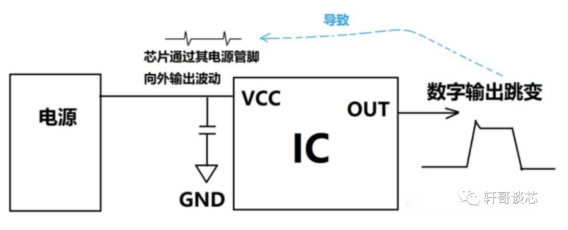

到目前為止,布局看起來還不錯。但是,在進(jìn)行電源完整性分析時在其中一個電源子網(wǎng)中,很明顯該電路的阻抗曲線在低頻時明顯高于目標(biāo)阻抗。這表明缺少“大”高電容去耦電容器。曲線如下所示:

這種情況可能導(dǎo)致以太網(wǎng)PHY電源設(shè)備出現(xiàn)問題。分析此問題后,決定稍微重新進(jìn)行PCB布置,然后將唯一的大電容器移至該子網(wǎng)的三個引腳之一。

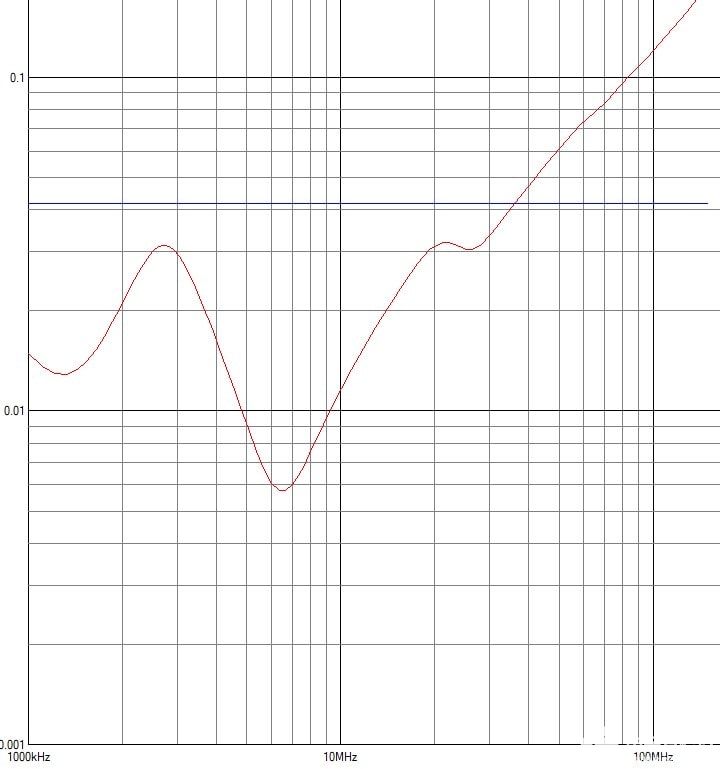

加上幾個小電容器的電容的微小變化以抑制第二個峰值,此措施可顯著改善結(jié)果,請參見下圖:

即使在此板中,也發(fā)現(xiàn)了如上所述的其他一些問題。本文中考慮的示例只是一個特例,清楚地表明了無條件地需要對具有高端IC(例如FPGA或PHY)的電路板以及具有大電流的電路板進(jìn)行功率完整性分析,從而避免出現(xiàn)實際問題。樣品。

另外,我們要強(qiáng)調(diào)的是,在實際設(shè)計中,即使嚴(yán)格按照制造商的建議執(zhí)行,也可能存在各種偏差,如果沒有適當(dāng)?shù)?/span>SI / PI仿真,這些偏差是無法預(yù)測的。

-

印制電路板

+關(guān)注

關(guān)注

14文章

954瀏覽量

40760 -

PCB線路板

+關(guān)注

關(guān)注

10文章

434瀏覽量

19877 -

PCB打樣

+關(guān)注

關(guān)注

17文章

2968瀏覽量

21696 -

華秋DFM

+關(guān)注

關(guān)注

20文章

3494瀏覽量

4459

發(fā)布評論請先 登錄

相關(guān)推薦

去耦電容的擺放位置和作用

巧了不是,原來你也不知道啥是去耦電容的“濾波半徑”啊!

微處理器電源引腳上的去耦電容應(yīng)用

去耦電容越大越好嗎,去耦電容值的選擇

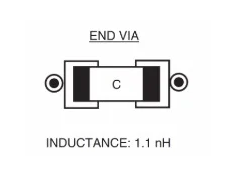

用于連接去耦電容器的過孔配置

分享PCB中的去耦電容設(shè)計

在PCB上正確放置去耦電容

在PCB上正確放置去耦電容

評論