引言

某系統中的H橋驅動電路需要采用2路脈沖寬度調制器(Pulse Width Modulation,PWM)信號來驅動一個電機,以控制其正、反兩個方向的運轉,且兩路信號必須有一定的時間間隔來避免驅動電流過大而損害驅動元件。為使其能靈活應用,針對系統要求,本設計的PWM控制器應具備以下功能:

(1)有3路獨立PWM輸出,每路輸出2個驅動信號,而且其周期、占空比、死區時間應可編程;

(2)對應10 MHz系統時鐘,周期為1μs~6.5536 ms;

(3)應用精簡地址線,以節省外圍引腳及地址資源的占用;

(4)能提供與8/16 bits單片機的雙向數據接口,并具有內置的地址/數據鎖存器(74lS373)。

1 PWM電路的結構規劃

在采用自頂向下(Top_Down)正向設計PWM器件的過程中,芯片的結構劃分和規格定制是整個設計的重要環節,因此合理的結構設計將決定整個設計的成敗。

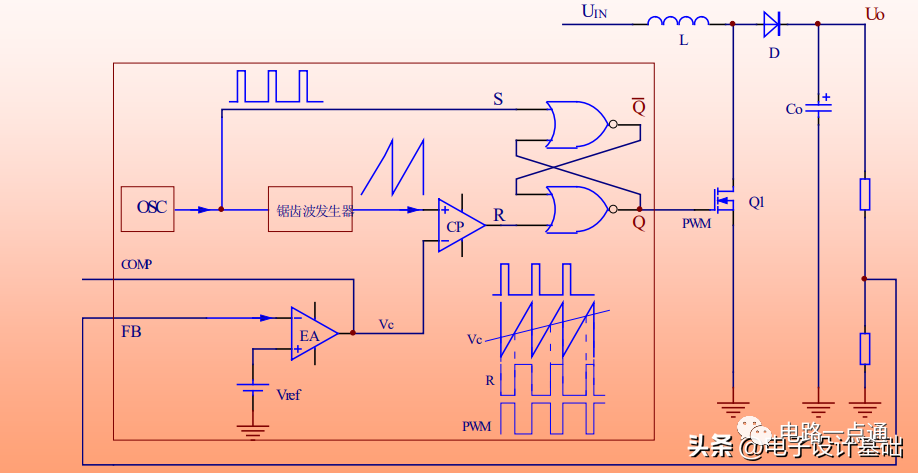

PWM 輸出信號的周期、脈寬、死區時間等參數可以通過加載內部的寄存器來實現,寫人PWM芯片的數據分為數據字與控制字兩部分。由內部控制邏輯 (ControlLogie)模塊來處理控制字信息,并譯碼產生各內部通道的內部信息寄存器片選信號。數據字則通過內部數據總線在各通道模塊來傳遞PWM 的特征信息數據。

PWM芯片內部各模塊可通過內部片選結合讀寫使能來完成數據交換。芯片與外圍控制器進行數據交換時,可采用雙模式接口 (8/16 bits),并可通過外置選擇引腳DataWidth來選配。

本芯片的核心是由3個完全獨立且相同的通道模塊 (Channel)構成。通道內部的數據接口用于完成外部讀寫邏輯(RWLogic)傳輸到內部數據總線的數據收發工作。PWM周期生成模塊 (ClkGen)則可依據寫入的周期信息,輸出PWM的周期控制信號。

PWM輸出由通道狀態機完成,當通道接收到PWM信息數據后,先進行數據校驗,合格的數據將在合適的條件下啟動狀態機,并在不同的狀態下完成PWM輸出。而不合格的數據則被忽略。

地址/數據鎖存依據通用 74LS373的邏輯功能,可以通過編寫一個完全可替代的L74LS373來實現。

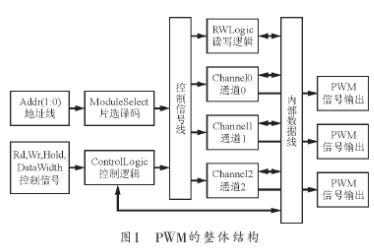

根據上述總體的構建思路,最終給出的芯片總體結構如圖 1所示。

2 PWM電路的結構設計

從圖1所示的PWM電路總體結構可以看出,該PWM電路主要由模塊片選譯碼、控制邏輯、讀寫邏輯、通道等四個模塊組成。

2.1 模塊片選譯碼

該模塊主要通過地址信號Addr與片選信號Cs_b的組合邏輯電路生成內部各子模塊的片選信號(ControlLogic,3個通道:Channel2,Channel1,Channel0)。

2.2 控制邏輯

該模塊主要產生通道內部Regs片選控制信號及各通道的輸出控制信號,同時完成精簡地址線的操作。

每個通道都包含各自獨立的4個16 bits的寄存器,包括正向信號長度、負向信號長度、死區長度、周期長度等。由于控制字寄存器為8 bits,因此.整個芯片至少占用3×4×2+1=25個地址(每個地址存儲8 bits數據),傳統做法至少需要5根地址線譯碼,而采用區分數據信息類型(控制字,數據字)的方式則可將地址線精簡到2根。相對單片機緊缺的外面地址資源來說,其好處是顯而易見的。具體來說,通過對寫人ControlRegister(控制字寄存器)的值進行分析,結合數據傳輸寬度生成內部Regs片選控制信號,就可以通過控制字信息來完成內部Regs的地址譯碼,同時反饋被操作的寄存器信息到RWLogic模塊,從而完成8/16bits的數據讀寫操作。

值得注意的是,由于PWM內部包含了3個完全一樣的獨立通道,因此,為了更方便的對控制字進行操作,通過對控制字寄存器的分析,可用控制邏輯電路自動將當前被操作通道的控制寄存器信息存儲在對應的控制寄存器中備份。這樣既方便在編程中靈活地操作各通道,又可避免讀寫過程中的誤修改非相干通道的控制信息。

2.3 讀寫邏輯

該模塊用于處理外部數據Data[15:0](包括外部為16位或8位數據總線連接方式)到內部DataInternal[15:0]的轉換。當DataWidth為1時,采用16 bits的數據傳輸;當DataWidth為0時,采用8 bits數據傳輸。通過PWM能完成對外部8 bits或16 bits的信息傳輸要求,準確的讀寫內部16bits的Regs。具體實現時,如采用16 bits傳輸,由于內部數據采用16 bits傳輸,可以采用每個地址對應16 bits數據,每個數據位一一對應的傳輸方式;而采用8 bits傳輸時,由于內部數據采用16bits傳輸,故可通過分析地址的奇偶特性來確定數據高低字節的存放,也就是通過ControlLogic反饋的字節選擇位,來使讀寫邏輯電路能夠自適應地把16 bits的Regs數據信息分割加載到合適的數據通道上,從而完成數據的輸入輸出控制。

為了精簡數據線,實現數據的雙向流通,本模塊通過片選和讀寫使能信號所控制的雙向三態門接口電路來隔離讀寫信息。

2.4 通道

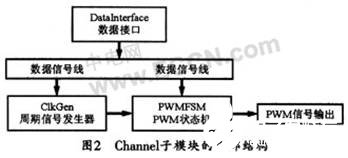

Channel 是PWM芯片的核心部分,每個Channel模塊都由3個子模塊組成,圖2所示是各Channel子模塊的內部結構圖。

2.5 數據接口

數據接口用于完成通道內寄存器的讀寫功能。該模塊通過組合通道片選、內部寄存器片選信號及模塊讀寫使能信號來產生各寄存器的讀寫使能信號。其讀寫操作可通過三態門與內部數據通道進行數據交換。

寫入本模塊的寄存器信息將進行數據校驗。只有校驗合格的數據才能載入內部寄存器的一級緩沖器(Buf)中,內部寄存器的一級緩沖器(Buffer)數據將輸出到PWMFSM模塊,以提供PWM的特征數據。

2.6 周期信號發生器

周期信號發生器可生成PWM的周期控制信號,其周期的長短由數據接口傳過來的周期寄存器值(CyeleReg)決定。該模塊將通過內部計數器計數時鐘,并與CycleReg比對,從而產生PWM的周期控制信號CycleScale。

2.7 狀態機

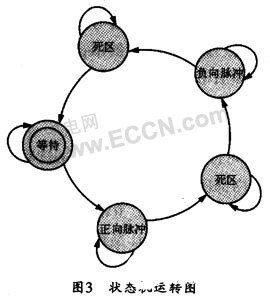

狀態機是產生PWM信號的核心功能模塊。通過加載Data Interface模塊接收到的通道內部寄存器Buffer值,由狀態機來進行運轉。PWMFSM模塊中包含有一個自運轉狀態機。當符合條件的寄存器值寫入Channel寄存器后,狀態機將在CycleScale信號的起始信息的引導下,在時鐘的上升沿將內部寄存器一級Buffer寫入到本模塊中的PWM 信息寄存器Buf中,以便在下一個運行周期內載入到PWM的狀態機中。狀態機啟動后,它將根據當前狀態輸出脈沖驅動信號。其狀態機的運轉圖如圖3所示。

其運轉流程如下:

(1)從復位或停止工作狀態進入IDLE狀態;

(2) 在合法的數據寫入通道寄存器且CycleScale的啟始信號被接收后,狀態機將當前通道內部寄存器Buffer的值載人狀態機定時器,同時進入正向脈沖狀態,以便準備輸出正向電機驅動信號;

(3)在正向脈沖狀態下,定時器開始減計數,直到到達完成正向驅動所需要的時間,同時在結束正向驅動的輸出后,進入死區狀態;

(4)在死區狀態,關閉正向、負向電機驅動信號,并通過定時器等待死區時間結束,然后進入負向電機驅動狀態 (負向脈沖);

(5)在負向脈沖狀態下,定時器開始減計數,直到到達完成負向驅動所需要的時間,到在結束負向驅動的輸出后,進入死區狀態;

(6)在死區狀態,關閉正向、負向電機驅動信號,并通過定時器等待死區時間結束,然后進入空閑等待狀態。等待下一次的啟動信號。

3 PWM編程

PWM的工作模式由外部引腳與內部控制字寄存器決定。

3.1PWM芯片的工作模式

PWM芯片的工作模式可由PWMh_b來設定:

當其為1時,為全局使能輸出,此時為正常工作模式,但各Channel工作模式可取決于其 PWMEN位的值;而當PWMh_b為0時,全局禁止輸出,此時整個芯片不工作,芯片進入低功耗模式,同時時鐘被禁止輸入到內部通道模塊。

3.2 PWM芯片的控制字寄存器

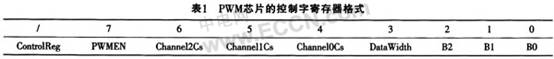

對于控制字寄存器ControlReg[7:0]:在其地址[A1,A0]=00的情況時,其操作格式如表1 所列。

由于控制字寄存器僅有一個,但實際各通道都有一個備份的控制字寄存器來控制對應的通道。因此并不會由于對某通道控制字的操作而影響其它無關的通道。本格式中的各位定義如下:

PWMEN:當芯片全局使能輸出時,此位可決定各通道PWM的輸出使能,當PWMh_b為1時,各通道的輸出正常,為0時,則通道禁止輸出;

Channel2Cs:選通 Channel2。使能對Channel2模塊的操作,并將控制字信息存儲到通道2的備份控制字;

ChannellCs:選通 Channell。使能對Channell模塊的操作,并將控制字信息存儲到通道1的備份控制字;

Channel0Cs:選通 Channel0。使能對Channel0模塊的操作,并將控制字信息存儲到通道0的備份控制字;

[B2,B1,B0]:內部寄存器片選譯碼。每個通道的PWM內部都有8個寄存器地址。通過ChannelX的選通結合[B2,B1,B0]的譯碼,可產生內部通道Regs的片選信號。

3.3 PWM編程

PWM芯片的引腳排列如圖4所示,當其在上電加載時鐘后,所有通道都禁止輸出。系統通過采樣DataWidth來確定外圍數據接口的寬度,如果采用16bits傳輸(DataWidth=1),則Data[15:0]都使用;如果采用8bits傳輸 (DataWidth=0),則僅使用Data[7:0],而將高8bits接地。

復位(Reset_b)結束后,在片選(Cs_b)有效的情況下,可以對芯片進行讀寫操作。對通道的一次完整的讀寫包括寫控制字與讀寫通道寄存器兩個過程,寫控制字選中通道內寄存器,讀寫通道寄存器則可獲取通道寄存器信息,只有當合理的數據寫入后,且在PWMH-_b有效(PWMH_b=1)時,PWM內部通道才使能輸出信號。一般情況下,各通道的輸出使能由各通道的控制字寄存器的 PWM_EN位決定。

采用控制字自動備份的方式可使控制字的編程更加靈活。它既可以使同一個類型的寄存器(不同通道)一起寫控制字,亦可對同一個通道一塊操作。但是所有控制字命令都可以在PWM的控制字命令列表中查詢。

4 PWM的仿真及驗證

PWM的仿真是PWM功能驗證的必要環節。可以Modelsim結合腳本文件進行仿真,并采用89C51結合FPGA驗證板對整個設計進行驗證。

4.1 PWM的仿真

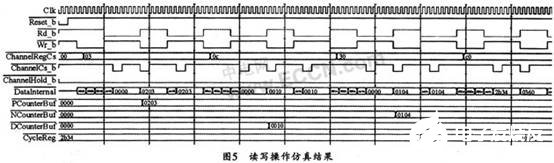

ModeslSim仿真主要觀察PWM電路的雙向IO端口以及PWM的Regs讀寫控制時序。對于雙向端口的數據交換,可以采用讀寫控制結合三態門來完好地解決。而對于大量的Regs讀寫操作,則應通過模擬單片機對外圍器件進行操作,并利用Task調用的方式來實現。本文的讀寫操作仿真結果如圖5所示。

從圖5可以看到,當采用16 bits讀寫時,各寄存器通過內部DataInternal數據總線的傳輸過程與電路設計要求完全一致。RWLogic與DataInterface模塊的功能完全符合設計預想。

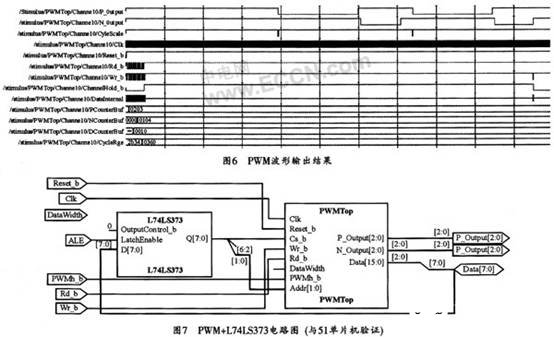

從圖6所示的PWM波形仿真結果可見,PWM輸出信號在ClkGen的 CycleScale信號控制下,其周期輸出編程設定的PWM波形與之完全一致,同時還能異步響應ChannelHold_b信號的輸出控制。

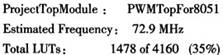

4.2 PWM的驗證

PWM的FPGA驗證可采用8 bits數據接口,并用89C51做外圍控制器(12 MHz)來對PWM進行操作。為了方便與單片機的接口,可將74LS373鎖存器內置到PWM中,其整個數字部分設計如圖7所示。

5 結束語

通過Synplify Pro編譯后,其最后的結果為:

該方案的整個電路設計占用FPGA資源的35%。對于51系列的單片機而言,該 PWM電路可運行的頻率遠遠超過系統頻率。因此,在讀寫時序上完全可以保證整個設計的可靠性。

如果將編譯后的pof文件下載到 APEX20KEEP20K100E TQ144-2X(Altera)fpga驗證板,并采用40 MHz的FPGA時鐘,那么,根據軟件仿真的步驟,再將讀寫操作轉換為單片機程序燒錄到單片機,就可通過示波器清楚的看到,其實際輸出與設計完全一致,非常好地實現了當初的設計要求。

責任編輯:gt

-

FPGA

+關注

關注

1630文章

21766瀏覽量

604604 -

控制器

+關注

關注

112文章

16412瀏覽量

178721 -

PWM

+關注

關注

114文章

5194瀏覽量

214347

發布評論請先 登錄

相關推薦

求解答!用STC89C51系列數字秒表

微控制器中的PWM模塊介紹

采用AT89C52單片機作為路燈控制系統的支路控制器

UCC38C42系列高速BiCMOS電流模式PWM控制器

如何將自定義邏輯從FPGA/CPLD遷移到C2000?微控制器

PWM控制器和逆變器的區別

PWM控制器與MPPT控制器的區別

基于FPGA的SPI Flash控制器的設計方案

BiCMOS 低功耗電流模式 PWM 控制器UCCx8C4x數據表

采用89C51結合FPGA驗證板實現PWM控制器的應用設計

采用89C51結合FPGA驗證板實現PWM控制器的應用設計

評論