在下一個PCB原型的PCB設計過程中,有幾個因素會影響走線的寬度,長度和樣式。本文將深入探討各種需要特定走線布局特征以及如何或何時將它們納入您的PCB設計的應用。

什么是走線寬度?

讓我們從基礎開始。跡線寬度到底是什么?為什么指定特定的跡線寬度如此重要?PCB走線的目的是將任何一種電信號(無論是模擬,數字還是電源)從一個結點連接到另一個結點。

結點可以是組件的引腳,較大跡線或平面的分支,也可以是用于探測的空焊盤或測試點。跡線寬度通常以密耳或數千英寸為單位。普通信號的標準走線寬度(無特殊要求)可能在7-12密耳范圍內,長達幾英寸,但是在定義走線的寬度和長度時,應考慮許多因素。

該應用程序通常會驅動PCB設計中的走線寬度和走線類型,并且在某個時候,通常在PCB制造成本,電路板密度/尺寸和性能方面保持平衡。如果電路板具有特定的設計要求,例如速度優化,噪聲或耦合抑制或高電流/電壓,則跡線的寬度和類型可能比優化裸PCB的制造成本或整體電路板尺寸更為重要。

PCB制造中與走線相關的規范

通常,以下與走線有關的規格開始增加裸露的PCB制造成本。

由于更嚴格的PCB公差和制造,檢查或測試PCB所需的高端設備,成本變得相當高:

l 跡線寬度小于5密耳(0.005英寸)

l 跡線間距小于5密耳

l 直徑小于8密耳的通孔

l 痕跡厚度小于或等于1盎司(等于1.4密耳)

l 差分對和受控長度或走線阻抗

結合了PCB占用空間的高密度設計,例如極細間距的BGA或高信號計數的并行總線,可能需要2.5密耳的走線寬度,以及直徑不超過6密耳的特殊類型的通孔,例如激光鉆孔的微通孔。相反,某些高功率設計可能需要非常大的走線或平面,從而消耗了整個層,并且澆注的盎司量比標準的要厚。在空間受限的應用中,可能需要非常薄的板,其中包含幾層并且有限的銅澆注厚度為半盎司(0.7密耳厚度)。

在另一些情況下,從一個外設到另一個外設進行高速通信的設計可能需要走線具有受控的阻抗以及彼此之間的特定寬度和間距,以最大程度地減少反射和電感耦合。或者設計可能需要一定的長度才能匹配總線中的其他相關信號。高壓應用需要某些安全功能,例如最小化兩個暴露的差分信號之間的距離,以防止產生電弧。無論特征或特性如何,跟蹤定義都很重要,因此讓我們探索各種應用程序。

各種走線寬度和厚度

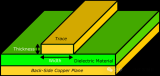

PCB通常包含多種走線寬度,因為它們取決于信號的需求(如圖1所示)。所示的較細跡線是針對通用TTL(晶體管-晶體管邏輯)電平信號的,對大電流或噪聲保護沒有特殊要求。

這些將是電路板上最常見的走線類型。

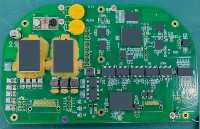

較粗的走線已針對電流承載能力進行了優化,可用于需要更高功率的外圍設備或與電源相關的功能,例如風扇,電動機以及向較低級別組件的常規電源傳輸。在圖的左上部分甚至顯示了一個差分信號(USB高速),其定義的特定間距和寬度可滿足90Ω的阻抗要求。圖2顯示了一塊稍微密集的電路板,該電路板具有6層,并且需要一個BGA(球柵陣列)組件,需要更細的走線。

PCB走線寬度如何計算?

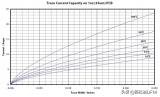

讓我們逐步完成為功率信號計算一定跡線寬度的過程,該功率信號將電流從一個功率組件傳遞到外圍設備。在此示例中,我們將計算用于直流電動機的電源路徑的最小走線寬度。功率路徑始于保險絲,穿過H橋(用于管理跨DC電機繞組的功率傳輸的組件),并終止于電機的連接器。直流電動機所需的平均連續最大電流約為2安培。

現在,PCB走線充當電阻器,走線越長和越窄,添加的電阻就越大。如果走線定義不正確,那么大電流可能會損壞走線和/或給電機帶來明顯的電壓降(導致速度降低)。圖3中所示的NetC21_2長約0.8英寸,最大需要承載2安培的電流。如果我們假設一些常規情況,例如1盎司銅的澆注量和正常運行期間的室溫,則需要計算最小走線寬度和在該寬度下的預期壓降。

如何計算PCB走線電阻?

以下是用于跡線面積的方程式:

面積[mils2] =(電流[Amps] /(k *(Temp_Rise [°C])^ b))^(1 / c),其中遵循IPC外部層(或頂部/底部)準則,k = 0.048, b = 0.44,c = 0.725。請注意,我們真正需要插入的唯一變量是current。

在下面的方程式中使用該區域將為我們提供必要的寬度,該寬度告訴我們承載電流而沒有任何潛在問題所需的走線寬度:

寬度[mils] =面積[mils ^ 2] /(厚度[oz] * 1.378 [mils / oz]),其中1.378與標準1盎司澆注厚度相關。

通過在上述計算中插入2安培電流,我們得到的走線最小值至少為30密耳。

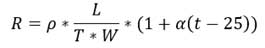

但這并不能告訴我們電壓降將是多少。這涉及更多,因為它需要計算走線的電阻,可以按照圖4所示的公式進行計算。

在該公式中,ρ=銅的電阻率,α=銅的溫度系數,T =跡線厚度,W =跡線寬度,L =跡線長度,t =溫度。如果將所有相關值插入30mils寬度的0.8英寸長的走線中,我們發現走線電阻約為0.03?并會降低約26mV的電壓,這對于該應用而言還可以。了解什么會影響這些值會很有幫助。

PCB走線間距和長度

對于具有高速通信的數字設計,可能需要特定的間距和調整的長度,以最大程度地減少串擾,耦合和反射。為此,一些常見的應用是基于USB的串行差分信號和基于RAM的并行差分信號。通常,USB 2.0將需要以480Mbit / s(USB高速等級)或更高的速度進行差分對路由。這部分是因為高速USB通常在低得多的電壓和差分下工作,從而使總信號電平更接近本底噪聲。

有路由高速USB線時要考慮三個重要的事情:線寬,引線間隔和走線長度。

所有這些都很重要,但是三個中最關鍵的是確保兩條走線的長度盡可能匹配。根據一般經驗,如果走線的長度彼此之間相差不超過50密耳(對于高速USB),則會顯著增加發生反射的風險,這可能會導致通信不良。90歐姆匹配阻抗是差分對布線的通用規范,要實現此目的,應在寬度和間距上優化走線。

圖5顯示了為高速USB接口布線的差分對的示例,該差分對在15 mil的間隔內包含12 mil寬的走線。

包含并行接口的基于內存的組件的接口(例如DDR3-SDRAM)在走線長度方面將受到更嚴格的限制。大多數高端PCB設計軟件將具有長度調整功能,可優化走線長度,以匹配并行總線中的所有相關信號。圖6顯示了具有長度調整的走線的DDR3布局的示例。

地面填充的跡線和平面

帶有噪聲敏感組件的某些應用(例如無線芯片或天線)可能需要一點額外的保護。設計帶有嵌入式接地過孔的走線和平面可以極大地幫助最大程度地減少附近走線或平面拾取的耦合以及爬入板邊緣的板外信號。

圖7顯示了一個藍牙模塊的示例,該模塊放置在板的邊緣附近,其天線(通過絲網印刷“ ANT”標記)在一條厚的走線外部,該走線包含連接到接地層的嵌入式過孔。這有助于將天線與其他板載電路和平面隔離。

這種通過地埋的走線(在這種情況下為多邊形平面)的另一種方法可用于保護板電路免受外界的板外無線信號的影響。圖8顯示了一個噪聲敏感的PCB,其沿板的周邊具有接地通孔嵌入式平面。

PCB布線的最佳實踐

許多因素決定著PCB領域的走線特性,因此在布線下一塊PCB時,請務必遵循最佳實踐,您會發現PCB晶圓廠成本,電路密度和整體性能之間達到平衡。

如果您正在尋找下一個PCB應用的報價,請與我們的專家團隊聯系,以幫助您以合適的價格準確獲得所需的東西。我們專注于PCB制造和PCB組裝,以適應典型的董事會無法制造或組裝的復雜設計。

讓我們來幫助您將您的設計變為現實。

-

印制電路板

+關注

關注

14文章

954瀏覽量

40760 -

PCB設計

+關注

關注

394文章

4683瀏覽量

85551 -

PCB打樣

+關注

關注

17文章

2968瀏覽量

21696 -

華秋DFM

+關注

關注

20文章

3494瀏覽量

4459

發布評論請先 登錄

相關推薦

pcb線寬銅厚與電流的關系大嗎

Xilinx 7系列FPGA PCB設計指導

什么是PCB走線寬度?影響走線寬度的關鍵因素有哪些

pcb走線厚度:打造更穩定、精準的PCB設計

PCB走線寬度定義與計算方法詳解

PCB走線寬度在PCB設計中的重要性

PCB走線寬度在PCB設計中的重要性

評論