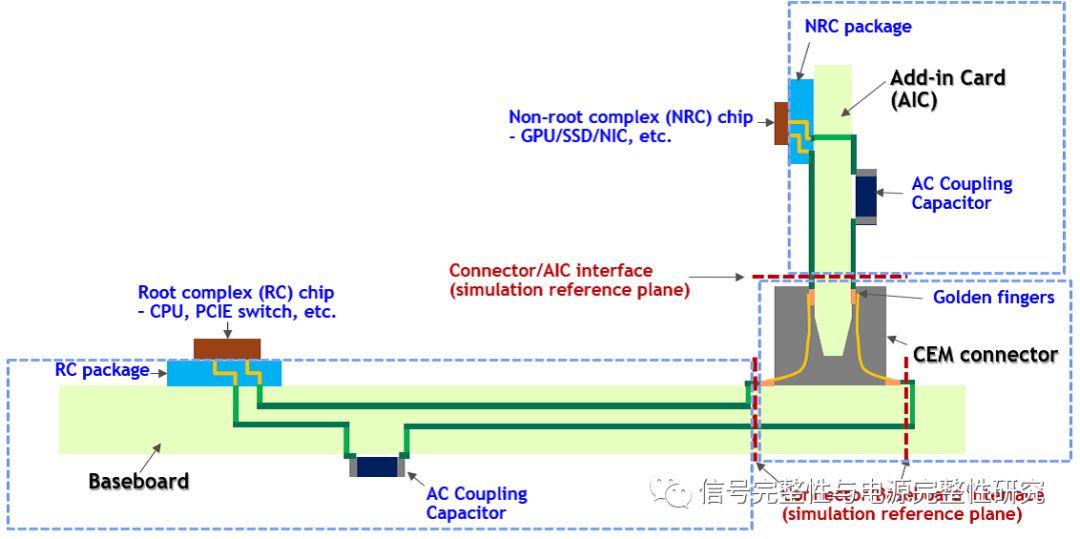

前言:PCIExpress base和CardElectro Mechanical(CEM)規范定義了用于桌面/服務器PCIe通道的拓撲結構。典型的通道包括Root Complex(CPU),Baseboard(主板),CEM連接器,Add-in Card(AIC)和Non-root complex(GPU / SSD / NIC)。交流耦合電容放置在靠近發射器的TX通道上。

PCIe Gen5相關規范預計將于2019年完成。數據速率從16 GT/s增加到32GT/s。該通道最多可包含2個CEM連接器,并且在母板和AIC上具有與Gen4類似的走線長度。(小于4 inch)

PCIE5.0 大致拓撲結構

本文討論了Gen5的新性能要求,并描述了在連接器和AIC上實現這些要求的關鍵設計因素,上一代Gen4的設計要求簡列如下:

1.使用更高等級的PCB材料,例如Megtron 6、 Megtron 7、IT-988G-SE材料需要多和加工廠溝通,其他要求可能具有挑戰性,如無鹵素、耐高溫、超大板要求。

2.必須保持CEM連接器的向后代的兼容性,同時提高其性能。

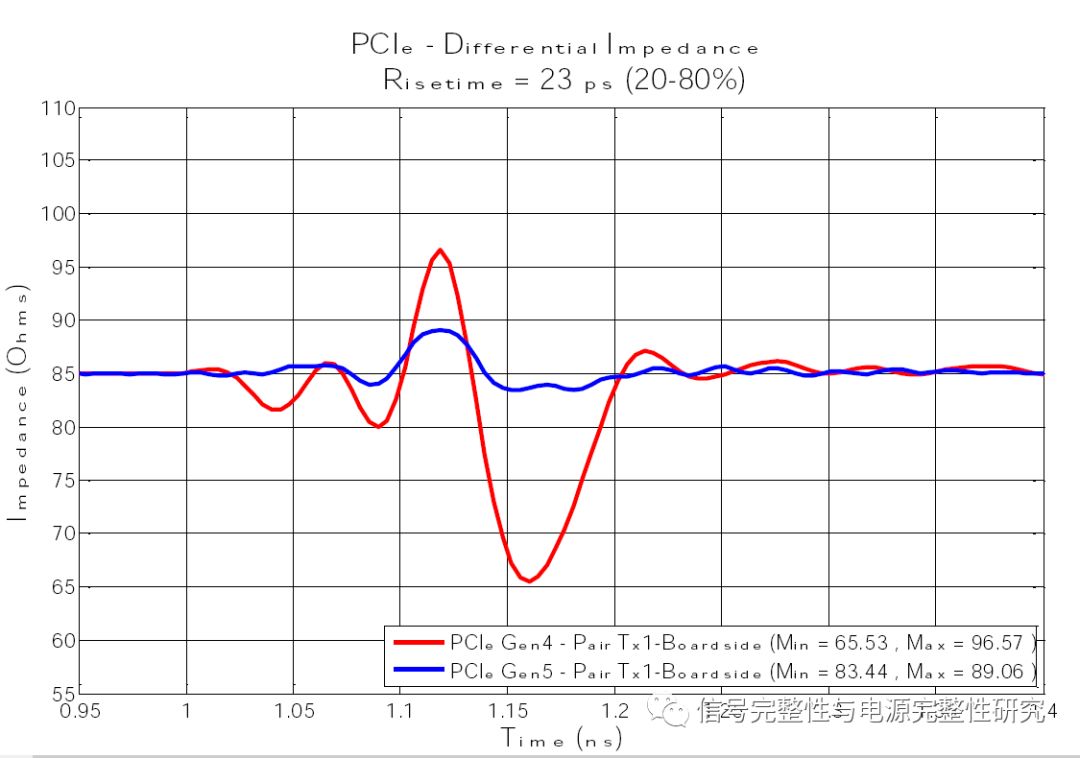

要使用以前的PCIeCard,CEM連接器的外部外殼尺寸必須保持不變。可以修改連接器的內部尺寸以實現所需的損耗和串擾預算,但仍必須保持與舊AIC的兼容性。在連接器內部,我們可以改變觸點的幾何形狀,以實現更好的插入損耗(IL)和回波損耗(RL),同時保持相同的形狀因子以保持向后兼容性。這改善了配合接口區域的阻抗,同時將串擾提高到-40dB以下的水平。我們還可以在設計中添加有損塑料材料,以抑制不需要的接地模式共振。

PCIe4 和PCIe 5 CEM連接器阻抗比對(Amphenol)

3.關于走線和VIA

對于AIC設計人員來說,第一個要問的關鍵問題是,“我們可以繼續使用Gen5 PCB的微帶走線技術嗎?”雖然Gen4中的大多數基板已經使用帶狀線,但典型的AIC仍然使用微帶來實現更簡單的布線,通常短于4inch,性能可接受。由于所有球柵陣列(BGA)焊盤,金手指和背面安裝的交流耦合電容都在表面層上,因此微帶線選擇可最大限度地減少通孔數量。歷史上,微帶通常表現出比帶狀線更低的損耗,因為通常使用更寬的線寬來保持85歐姆的阻抗。然而,對于Gen5速度,微帶線具有與帶狀線相當的損耗,并且在阻抗控制,銅表面粗糙度,遠端串擾和模式轉換方面比帶狀線差得多。微帶線對大批量生產(HVM),溫度和濕度變化也更敏感。相比之下,帶狀線需要更多的過孔用于層過渡,并且可能需要通過back drill減少stub。造成布線通道狹窄,這可能需要增加PCB層數。

4.對于差分線阻抗公差控制,要求最好在+-5%,保證PCB阻抗平滑。

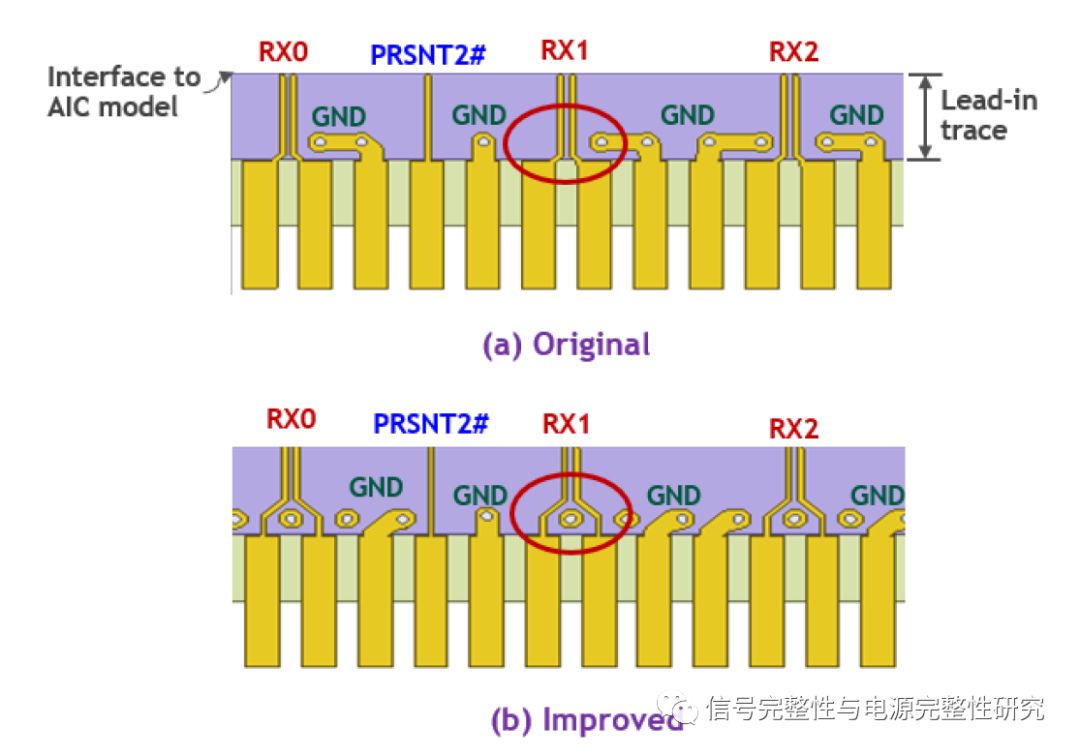

綜上所述:對于每個產品系列,所有這些因素之間的權衡導致不同的設計選擇。Gen5的回損目標也很難實現。通常,金手指和連接器接觸處造成了阻抗不匹配。為了解決這個問題,我們建議改進引入線的形狀和尺寸,以更好地保持阻抗并優化回波損耗,從而優化整體通道性能。

Gen5的新增設計規則分享如下:

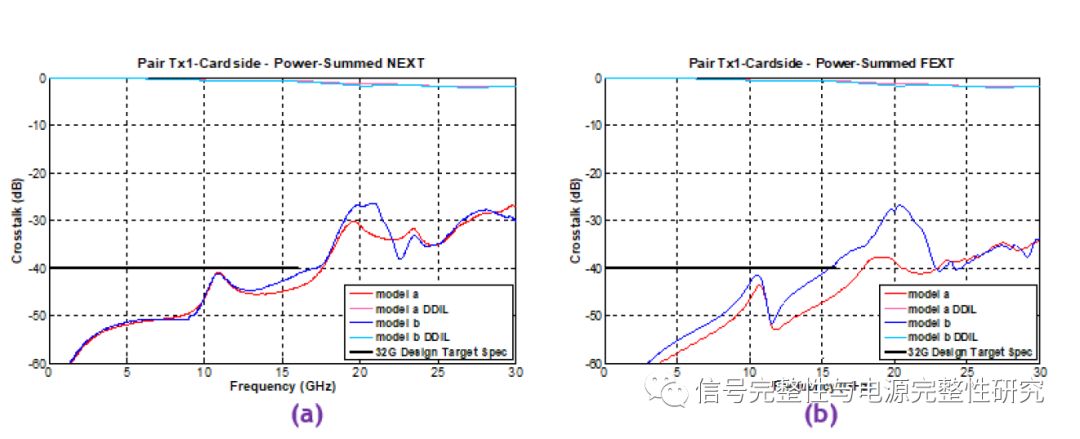

1.CEM連接器處的優化設計,如下圖是2中fanout的方式

2種CEM連接器的出線方式

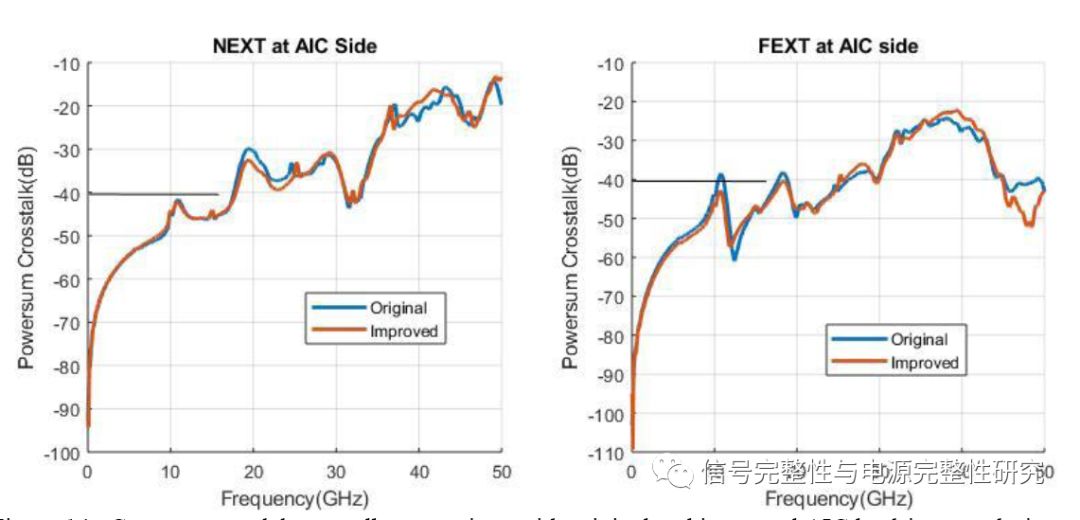

藍色線顯示原始結構的串擾,其中不包括額外的通孔。紅色線顯示了通過添加接地通孔可以實現的實質性改進,每個pin腳接另一端地,接地通孔用于改善接回流地路徑的整體完整性。

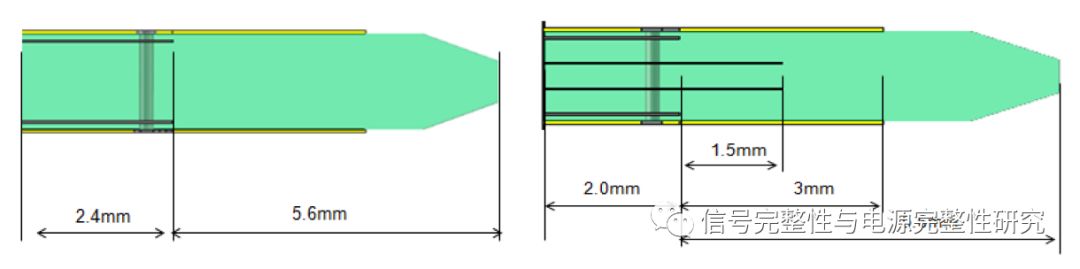

2.Add-in Card (AIC) 金手指部分尺寸的設計

PCIe 4 和PCIe 5AIC Card 尺寸比對

(Amphenol)

PCIe 4 和PCIe 5 AIC Card 內部尺寸比對

(Amphenol)

為了保持向后兼容性,根據PCIe Gen5規范,金邊指的前邊緣距離插卡邊緣依然是5.6 mm。連接區域與較舊的Gen4版本相同。 PCIe Gen4和Gen5的AIC形狀因子分別如上圖所示

為了減少NEXT,在PCIe Gen5附加卡的邊緣指區域下方增加了20.5mil的內部接地層。內部接地層位于PCB內部深處,并且不延伸到邊緣手指處。

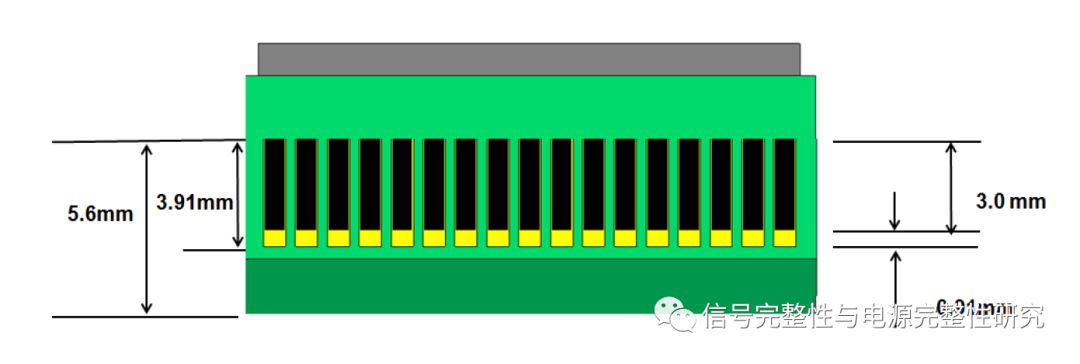

3. 金手指部分焊盤的設計

PCIe4 和PCIe 5 AIC Card 焊盤尺寸比對

對比Gen4和Gen5之間的AIC焊盤尺寸。 PCIe Gen5焊盤尺寸為3.91x0.7 mm(上圖中所示的黃色焊盤),PCIe Gen5的接觸焊盤已減小到3.0x0.6 mm(圖中所示的黑色焊盤)。更改接觸墊尺寸可將擦拭距離從2.5mm(PCIe Gen4 SMT)減小到1.6 mm(PCIe Gen5 SMT),滿足建議的最小擦拭距離1.43 mm且有足夠的緩沖。 根據PCB制造商的意見,只要尺寸公差不低于+/- 0.038 mm,手指尺寸的減小就不會產生任何成本影響。 這種公差可由頂級PCB供應商維護。

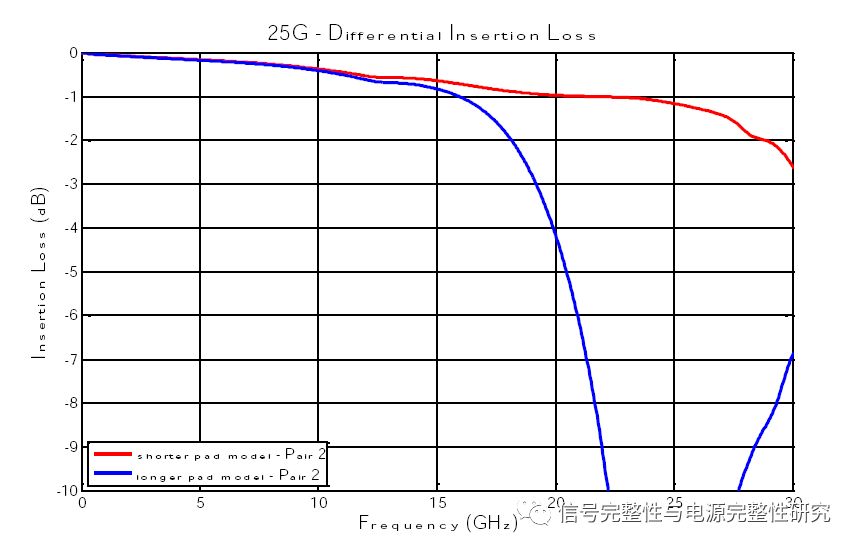

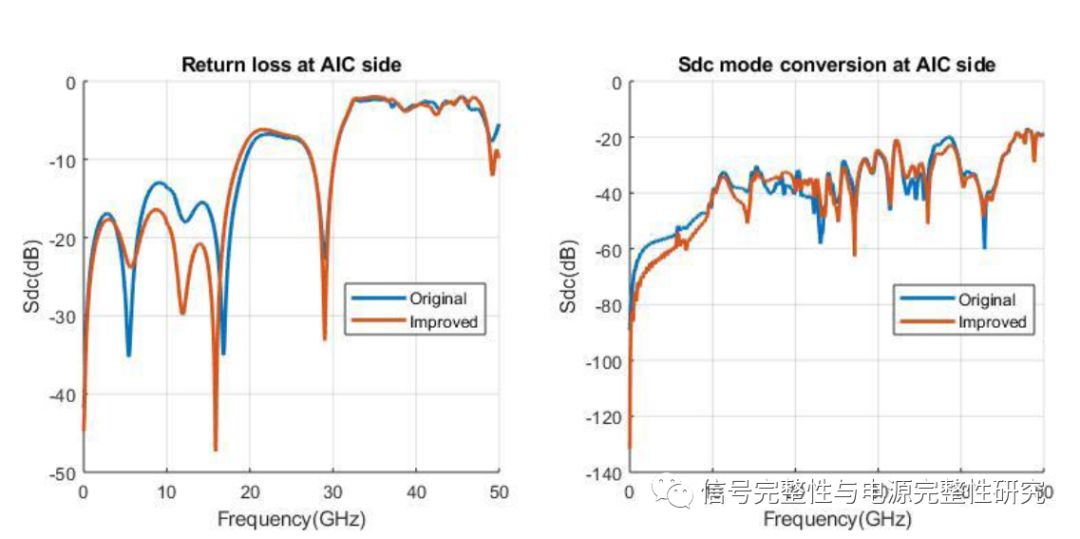

優化焊盤后損耗結果比對

4. AIC走線部分優化

使用上述優化結果,X-talk,插損,回損指標均有相應提高

5.使用帶狀線

微帶線設計時,仿真結果顯示出比帶狀線更差的X-talk,但對于具有20dB+損耗的全通道,它們在眼圖邊緣上的差異很小。

原文標題:SI-list【中國】PCIe Gen 5.0 PCB的設計與優化

文章出處:【微信公眾號:信號完整性與電源完整性研究】歡迎添加關注!文章轉載請注明出處。

責任編輯:haq

-

pcb

+關注

關注

4319文章

23080瀏覽量

397507 -

cpu

+關注

關注

68文章

10854瀏覽量

211583 -

服務器

+關注

關注

12文章

9123瀏覽量

85324

原文標題:SI-list【中國】PCIe Gen 5.0 PCB的設計與優化

文章出處:【微信號:si-list,微信公眾號:高頻高速研究中心】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

CDCDB800/803超低附加抖動、8路輸出PCIe Gen1至Gen5時鐘緩沖器

pcie 4.0與pcie 5.0的區別

在主板上優化PCIe通道設置

Xilinx 7系列FPGA PCIe Gen3的應用接口及特性

Kioxia發布PCIe 5.0 EDSFF E1.S SSD

使用TMUXHS4412多路復用器的PCIe?Gen 4.0應用布局指南

使用TI PCI-Express Gen5.0轉接驅動器進行眼圖掃描

PCIe 5.0 SerDes 測試

美光研發出世界首款PCIe Gen6 SSD

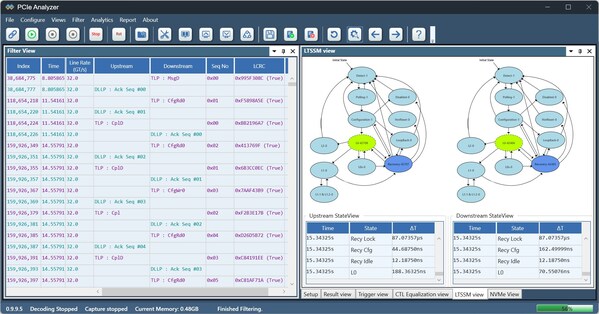

Prodigy Technovations推出功能強大的PCIe Gen5協議分析儀

HighPoint發布商用PCIe Gen5解決方案,最大可達960TB SSD容量

英韌科技:無AI不存儲,國產PCIe 5.0主控率先發力

下一代PCIe5.0 /6.0技術熱潮趨勢與測試挑戰

PCIe Gen5.0的設計與優化

PCIe Gen5.0的設計與優化

評論