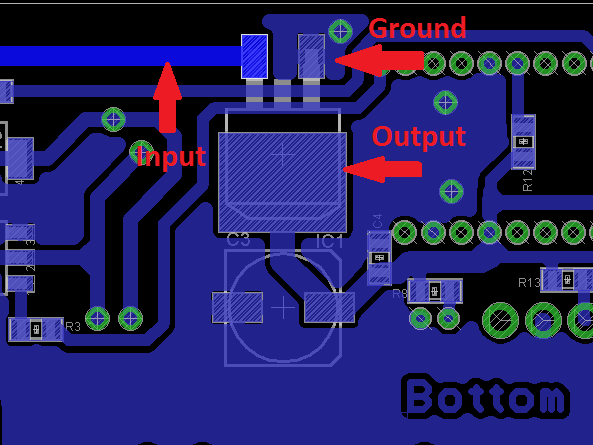

在我們學(xué)習(xí)嵌入式開發(fā)的過程中,PCB 布線是必不可少的。好的布線方式,輕則看著美觀、布局合理,重則可以節(jié)約生產(chǎn)成本,達到良好的電路性能和散熱性能,使元器件的性能達到最優(yōu)。今天,小編梳理了 PCB 設(shè)計中常見的布線方式,希望大家看后能有所啟發(fā)。

時鐘的布線

時鐘線是對 EMC 影響最大的因素之一。在時鐘線上應(yīng)少打過孔,盡量避免和其它信號線并行走線,且應(yīng)遠(yuǎn)離一般信號線,避免對信號線的干擾。同時應(yīng)避開板上的電源部分,以防止電源和時鐘互相干擾。

如果板上有專門的時鐘發(fā)生芯片,其下方不可走線,應(yīng)在其下方鋪銅,必要時還可以對其專門割地。對于很多芯片都有參考的晶體振蕩器,這些晶振下方也不應(yīng)走線,要鋪銅隔離。

走線角度

直角走線一般是 PCB 布線中要求盡量避免的情況,也幾乎成為衡量布線好壞的標(biāo)準(zhǔn)之一,那么直角走線究竟會對信號傳輸產(chǎn)生多大的影響呢?

從原理上說,直角走線會使傳輸線的線寬發(fā)生變化,造成阻抗的不連續(xù)。其實不管是直角走線,頓角,還是銳角走線,都可能會造成阻抗變化的情況。

直角走線的對信號的影響就是主要體現(xiàn)在三個方面:一是拐角可以等效為傳輸線上的容性負(fù)載,減緩上升時間;二是阻抗不連續(xù)會造成信號的反射;三是直角尖端產(chǎn)生的 EMI。

差分走線

差分信號和普通的單端信號走線相比,最明顯的優(yōu)勢體現(xiàn)在以下三個方面:

抗干擾能力強,因為兩根差分走線之間的耦合很好,當(dāng)外界存在噪聲干擾時,幾乎是同時被耦合到兩條線上,而接收端關(guān)心的只是兩信號的差值,所以外界的共模噪聲可以被完全抵消。

能有效抑制 EMI,同樣的道理,由于兩根信號的極性相反,他們對外輻射的電磁場可以相互抵消,耦合的越緊密,泄放到外界的電磁能量越少。

時序定位精確,由于差分信號的開關(guān)變化是位于兩個信號的交點,而不像普通單端信號依靠高低兩個閾值電壓判斷,因而受工藝,溫度的影響小,能降低時序上的誤差,同時也更適合于低幅度信號的電路。

蛇形線

蛇形線是 Layout 中經(jīng)常使用的一類走線方式。其主要目的就是為了調(diào)節(jié)延時,滿足系統(tǒng)時序設(shè)計要求。設(shè)計者首先要有這樣的認(rèn)識:蛇形線會破壞信號質(zhì)量,改變傳輸延時,布線時要盡量避免使用。但實際設(shè)計中,為了保證信號有足夠的保持時間,或者減小同組信號之間的時間偏移,往往不得不故意進行繞線。

審核編輯 黃昊宇

-

pcb

+關(guān)注

關(guān)注

4319文章

23080瀏覽量

397521

發(fā)布評論請先 登錄

相關(guān)推薦

AM62 PCB設(shè)計逃逸布線應(yīng)用說明

AM62x(AMC)PCB設(shè)計逃逸布線應(yīng)用說明

AM62Px PCB設(shè)計迂回布線

AM62x SiP PCB設(shè)計迂回布線

PCB設(shè)計與PCB制板的緊密關(guān)系

高速pcb布線規(guī)則有哪些

PCB線路板制造中常見的錯誤有哪些,如何避免?

PCB設(shè)計中的常見問題有哪些?

pcb電源布線規(guī)則分享 PCB電源布線的六大技巧

PCB設(shè)計工作中常見的錯誤有哪些?

pcb設(shè)計布局布線原則及規(guī)則

PCB設(shè)計必備:31條布線技巧

PCB設(shè)計常見布線方式梳理

PCB設(shè)計常見布線方式梳理

評論