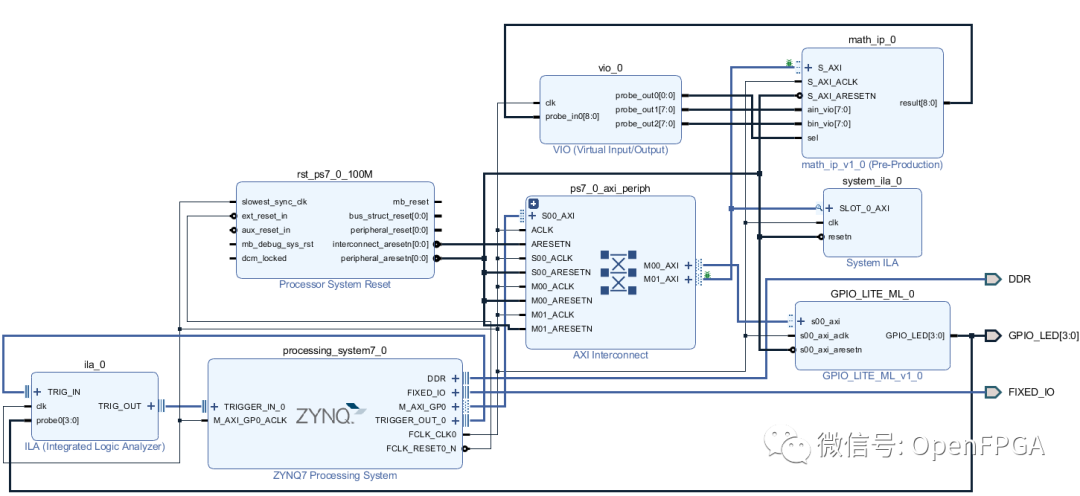

在《AXI-Lite 自定義IP》章節(jié)基礎(chǔ)上,添加ilavio等調(diào)試ip,完成后的BD如下圖:

圖4?53 添加測(cè)試信號(hào)

加載到SDK,并且在Vivado中連接到開(kāi)發(fā)板。

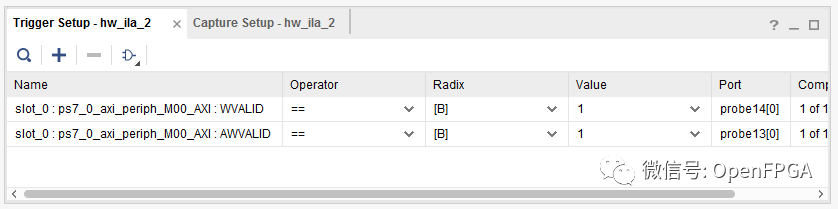

Trigger Setup,點(diǎn)擊“+”,選擇 AXI_WVALID,雙擊添加。設(shè)置 Radix 為 B,觸發(fā)條件 Value 為 1。

圖4?54 添加信號(hào)

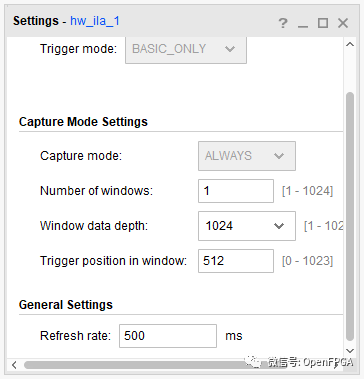

設(shè)置觸發(fā)位置為 512

圖4?55 設(shè)置觸發(fā)位置

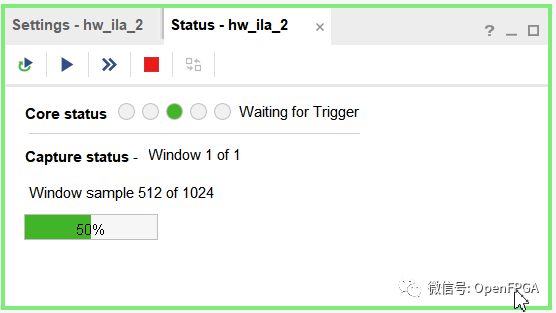

單擊運(yùn)行按鈕,啟動(dòng)觸發(fā),進(jìn)入等待觸發(fā)狀態(tài)。

圖4?56 等待觸發(fā)

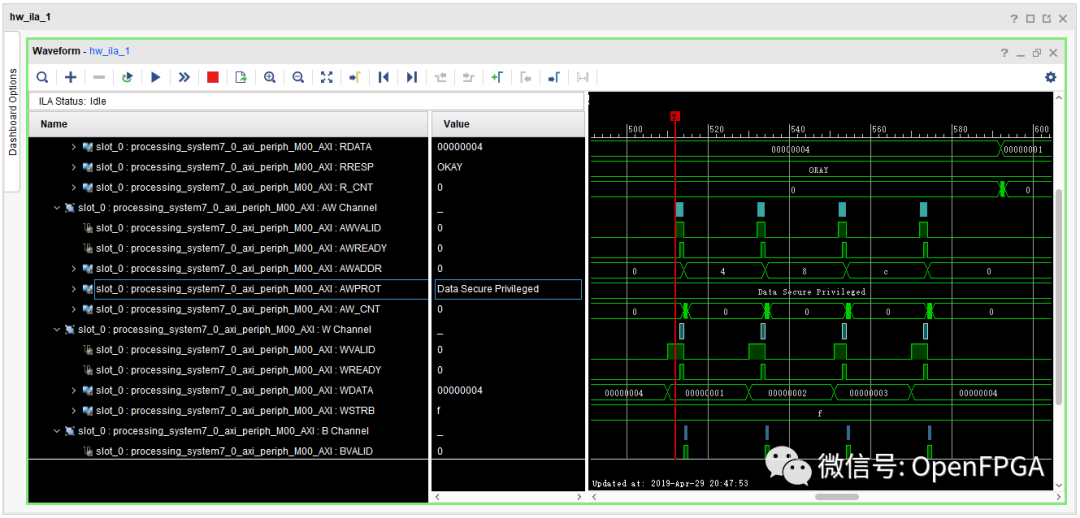

單擊 SDK 中的運(yùn)行按鈕后, VIVADO 中 HW_ILA2 窗口采集到波形輸出,可以看到 AXI 總線的工作時(shí)序。

SDK中 mian.c 程序功能是向 AXI4 總線寫入 1~4,再?gòu)?AXI4 總線讀數(shù)據(jù),從上面對(duì)未修改直接封裝的 IP 分析,可以讀出的數(shù)據(jù)應(yīng)等于寫入的數(shù)據(jù)。

從波形圖可以看出,寫入的數(shù)據(jù)是 1、 2、 3、 4,對(duì)應(yīng)基地址的偏移地址是 0、 4、 8、 12。

圖4?57 仿真結(jié)果

責(zé)任編輯:xj

原文標(biāo)題:觀察 AXI4-Lite 總線信號(hào)

文章出處:【微信公眾號(hào):OpenFPGA】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

-

總線

+關(guān)注

關(guān)注

10文章

2914瀏覽量

88695 -

AXI

+關(guān)注

關(guān)注

1文章

130瀏覽量

16833

原文標(biāo)題:觀察 AXI4-Lite 總線信號(hào)

文章出處:【微信號(hào):Open_FPGA,微信公眾號(hào):OpenFPGA】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

ZYNQ基礎(chǔ)---AXI DMA使用

DAC38J84 SYSREF的時(shí)鐘頻率如何確定?

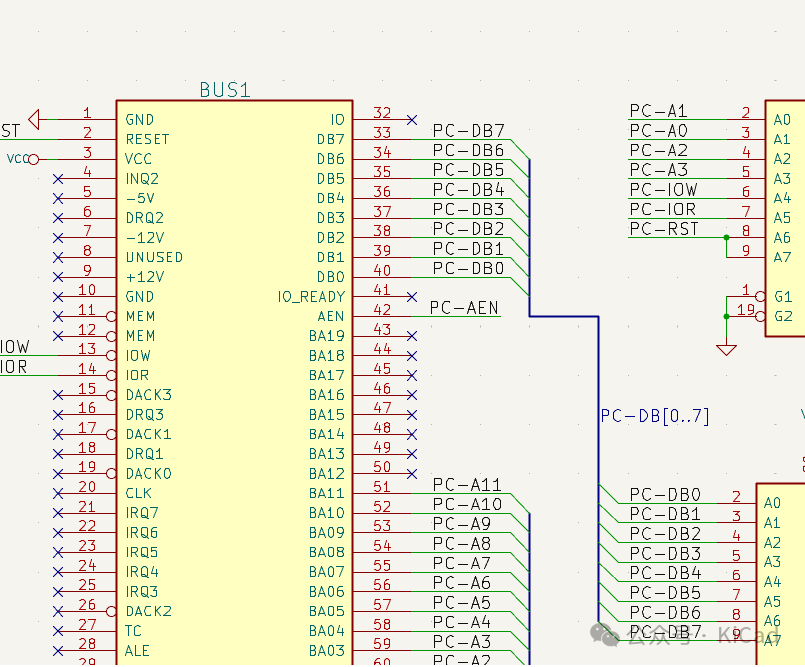

RISC-V芯片中使用的各種常用總線釋義

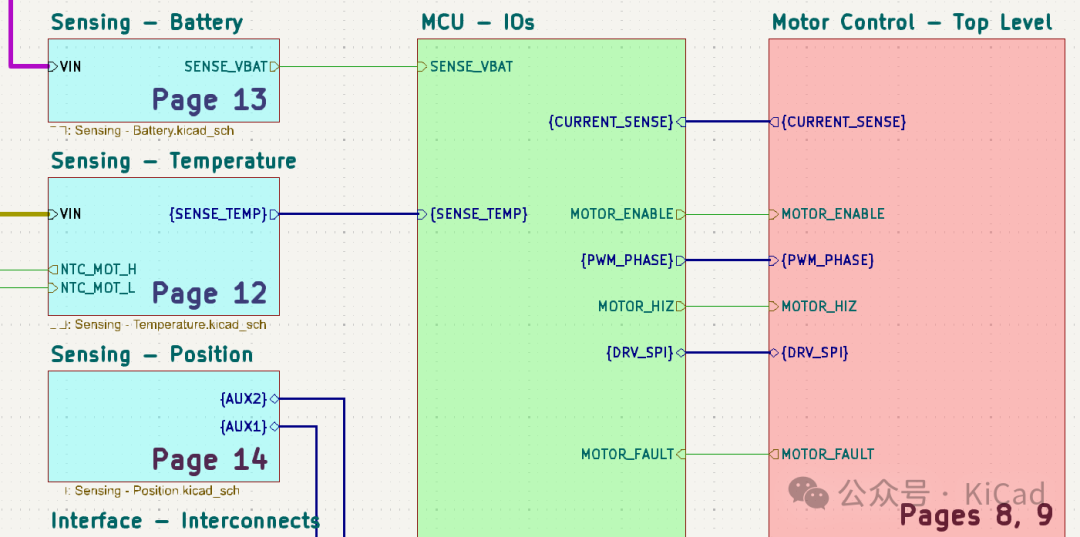

使用總線別名(Bus Alias)實(shí)現(xiàn)信號(hào)線束的功能

KiCad 中的總線的使用(還有信號(hào)線束?)

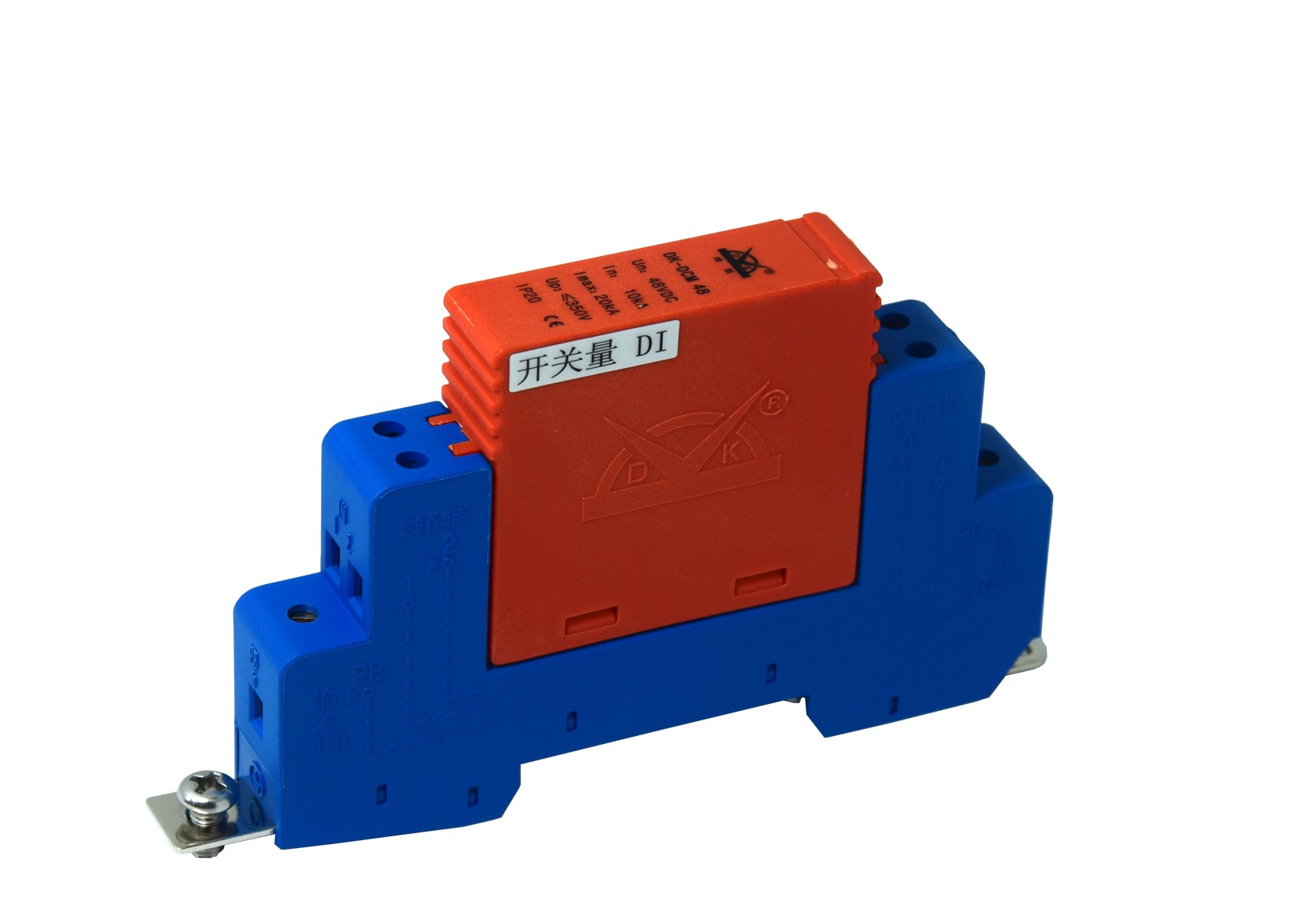

信號(hào)總線浪涌保護(hù)器選型、布置與接線方案

AMBA AXI4接口協(xié)議概述

控制總線傳輸?shù)?b class='flag-5'>信號(hào)大致有幾種

Xilinx NVMe AXI4主機(jī)控制器,AXI4接口高性能版本介紹

如何在psoc 4控制器 (CY8C4245AXI-483) 中實(shí)現(xiàn)RC5協(xié)議?

如何使用示波器檢測(cè)CAN總線上的信號(hào)

有關(guān)PL端利用AXI總線控制PS端DDR進(jìn)行讀寫(從機(jī)wready信號(hào)一直不拉高)

SoC設(shè)計(jì)中總線協(xié)議AXI4與AXI3的主要區(qū)別詳解

AXI4-Lite總線信號(hào)

AXI4-Lite總線信號(hào)

評(píng)論