本應(yīng)用筆記介紹了 ZNEO CPU 中的 DMA 控制器及其突出的特性,例如 DMA 和 CPU 帶寬共享控制以及四個獨立的 DMA 通道。本文檔還描述了 DMA 模式,以及它的軟件實現(xiàn)和應(yīng)用程序的測試/演示。

特征

ZNEO CPU 突出的直接內(nèi)存訪問特性是:

- 四個獨立的 DMA 通道

- 支持內(nèi)存到內(nèi)存、內(nèi)存到外設(shè)、外設(shè)到內(nèi)存以及外設(shè)到外設(shè)的數(shù)據(jù)傳輸。

- 在直接或鏈表模式下運行

- 字節(jié)、字或四元數(shù)據(jù)傳輸長度

- DMA 和 CPU 帶寬共享控制

- 高達 64K 傳輸(64 kByte、64 kWord 或 64 kQual)

- 外部 DMA 請求和 DMA 確認信號

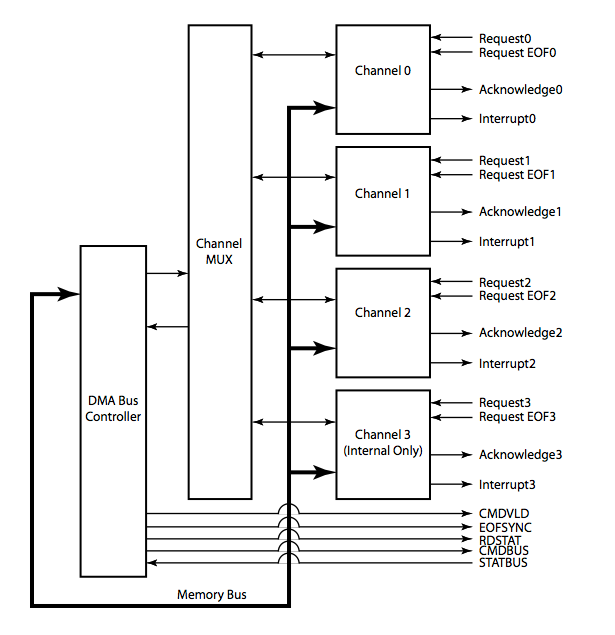

ZNEO DMA 用于減輕處理器執(zhí)行重復(fù)性任務(wù)的負擔。它將數(shù)據(jù)從一個內(nèi)存地址傳輸?shù)搅硪粋€內(nèi)存地址,或從一個外設(shè)傳輸?shù)搅硪粋€外設(shè)。這些任務(wù)需要由 DMA 控制器生成的讀和/或?qū)懼芷凇C總€ DMA 傳輸至少需要 2 個系統(tǒng)時鐘周期來執(zhí)行。圖 1 顯示了 Z16F MCU 的 DMA 控制器框圖,該控制器基于 ZNEO 架構(gòu)。

圖 1 DMA 框圖

DMA 模式

直接模式僅使用 DMA 中的寄存器進行操作。軟件直接寫入這些寄存器以設(shè)置和啟用 DMA。通過直接設(shè)置 DMAxCTL0 寄存器中的相應(yīng)位進入直接模式。下圖顯示了 DMA 寄存器以及它們?nèi)绾沃赶騼?nèi)存中分配的緩沖區(qū)。

鏈表模式

鏈表模式需要軟件為每個緩沖區(qū)分配緩沖區(qū)和設(shè)置描述符列表。完成此操作后,軟件將使用第一個描述符的地址寫入 DMAxLAR。然后 DMA 將第一個描述符讀入 DMA 控制和地址寄存器,LAR 數(shù)據(jù)除外。它執(zhí)行由 DMA 中的描述符數(shù)據(jù)指定的傳輸。傳輸完成后,DMA 讀入列表中的下一個描述符并繼續(xù)執(zhí)行傳輸。

軟件實施

此參考設(shè)計使用 ZNEO Z16F2800100ZCOG 開發(fā)套件。它利用 ZNEO CPU 的 DMA 控制器,特別是 DMA 的通道 0,用于演示目的。該應(yīng)用程序還使用 UART0 提供菜單驅(qū)動的控制臺,允許用戶測試 DMA 控制器的不同操作模式。此外,ADC、Timer2 和 UART1 等外設(shè)用于支持 DMA 演示。有關(guān)外設(shè)初始化的說明,請參見附錄 A。

CPU帶寬選擇

在任何 DMA 初始化之前,確保 CPU 總線設(shè)置為分配所需/所需的帶寬以供 DMA 使用。如果未設(shè)置,將使用重置值;也就是說,每三個 CPU 操作允許 DMA 傳輸一次。在本應(yīng)用筆記中,不同的帶寬選擇用于為 CPUCTL 的不同值提供示例。下表列出了用于每種傳輸類型的 CPU 帶寬。相同的 CPU 帶寬將用于直接模式和鏈表模式。

結(jié)果

直接模式在 DMA0CTL 的 IEOB 和 EOF 位設(shè)置為 1 且未設(shè)置水印值的情況下進行測試。也就是說,只有在當前緩沖區(qū)的末尾才會產(chǎn)生中斷。鏈表模式使用與直接模式相同的設(shè)置進行測試,DMA0CTL 的 HALT 位設(shè)置為 1。

編輯:hfy

-

控制器

+關(guān)注

關(guān)注

112文章

16332瀏覽量

177808 -

寄存器

+關(guān)注

關(guān)注

31文章

5336瀏覽量

120230 -

cpu

+關(guān)注

關(guān)注

68文章

10854瀏覽量

211583

發(fā)布評論請先 登錄

相關(guān)推薦

基于DMA控制器的UART串行通信設(shè)計

如何用C語言對DMA控制器編程

Crossbar的多通道DMA控制器設(shè)計

dma控制器芯片8257資料介紹

基于AXI總線的DMA控制器的設(shè)計

dma控制器由什么組成

基于SystemC的可配置多通道DMA控制器的設(shè)計

dma控制器的組成

DMA控制器原理詳解

ZNEO CPU 上的 DMA 控制器特性分析

ZNEO CPU 上的 DMA 控制器特性分析

評論