微處理器是當(dāng)今制造的每臺(tái)計(jì)算機(jī)的核心。它是幫助運(yùn)行和管理每個(gè)應(yīng)用程序和程序的工作馬。由于這部分的重要性,因此在構(gòu)建基于計(jì)算機(jī)的系統(tǒng)時(shí),每個(gè)用戶都必須首先選擇他們的處理器。

但是,您如何選擇處理器?每個(gè)處理器都有許多不同的規(guī)格。在規(guī)格之上,項(xiàng)目類型會(huì)影響需要哪種類型的處理器。為了為任何場(chǎng)景選擇最佳處理器,需要考慮幾個(gè)關(guān)鍵品質(zhì)。

關(guān)于當(dāng)前的微處理器及其架構(gòu)可以寫一整本書。為了幫助簡(jiǎn)化細(xì)節(jié),工作頻率(時(shí)鐘速度)、緩存和內(nèi)核數(shù)量是當(dāng)今主流臺(tái)式機(jī)微處理器的三個(gè)最重要的品質(zhì)。這三者對(duì)計(jì)算機(jī)的整體性能影響最大。

多核計(jì)算

多年來,計(jì)算機(jī)體系結(jié)構(gòu)發(fā)生了巨大的變化。有許多不同的架構(gòu),但相同的架構(gòu)不會(huì)停留很長(zhǎng)時(shí)間。為了在競(jìng)爭(zhēng)中脫穎而出,每年都必須開發(fā)新的創(chuàng)新架構(gòu)。最流行的架構(gòu)是 x86 架構(gòu)。在某些時(shí)候,當(dāng)今的大多數(shù)處理器都源自這種基本架構(gòu)。一些現(xiàn)代微架構(gòu)包括 Prescott、Nahalem、Sandy Bridge、Bobcat 和 Bulldozer。這些只是英特爾和 AMD 在過去幾年中生產(chǎn)的子微架構(gòu)的幾個(gè)例子。

主要的芯片制造商改變了他們生產(chǎn)的每種架構(gòu)的結(jié)構(gòu)和能力。構(gòu)成架構(gòu)的重要特征包括:內(nèi)核、CPU 時(shí)鐘頻率、L3 緩存和熱設(shè)計(jì)功耗 (TDP)。

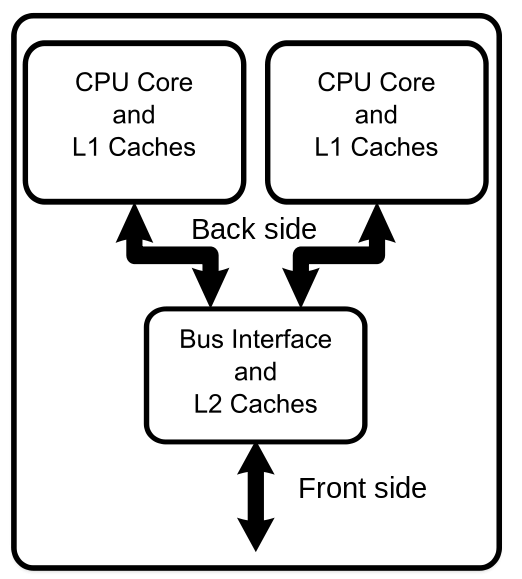

過去幾年來處理架構(gòu)進(jìn)步的最重要的發(fā)展是多核處理器的可能性。直到 2000 年代中期,工作頻率的上升足以補(bǔ)償正在制作的節(jié)目。但是,不斷上升的溫度和頻率限制會(huì)阻礙僅增加工作頻率。為了解決這個(gè)問題,工程師開發(fā)了增加芯片內(nèi)核數(shù)量的能力。在電氣方面,該芯片在單個(gè)芯片上制造有 2-8 個(gè)以上的內(nèi)核。這些內(nèi)核是它們自己的中央處理單元 (CPU),它們通過芯片與處理器上的其他單元相互通信,從而提高利用并行計(jì)算的程序的整體速度。

雙核設(shè)置

在選擇處理器時(shí),使用更多內(nèi)核總是更有利。處理能力隨著每增加一個(gè)內(nèi)核而增加,這允許程序跨多個(gè)內(nèi)核運(yùn)行,以及允許多個(gè)程序在單獨(dú)的內(nèi)核上運(yùn)行。總而言之,擁有多核可在性能上邁出一大步,并且是選擇現(xiàn)代處理器的關(guān)鍵規(guī)范。

工作頻率

正如架構(gòu)部分所強(qiáng)調(diào)的那樣,工作頻率在處理器性能中起著關(guān)鍵作用。每個(gè)微處理器都以某種振蕩器頻率的函數(shù)運(yùn)行。振蕩器頻率與振蕩器晶體的設(shè)計(jì)頻率直接相關(guān)。該振蕩器頻率通常通過電子電路轉(zhuǎn)換為方波。方波對(duì)于處理器內(nèi)部程序的執(zhí)行至關(guān)重要。然后,基于方波的數(shù)字表示,處理器可以“處理”1 和 0 中的函數(shù),然后使處理器可以讀取脈沖,以便它可以執(zhí)行指令。每個(gè)時(shí)鐘周期只能執(zhí)行一條指令,這就增加了提高工作頻率的重要性。工作頻率越高,可以處理的指令越多。如果正在處理更多指令,則可以在更短的時(shí)間內(nèi)完成更多工作。

今天的處理器可以在 2 GHz 到 4 GHz 的任何頻率范圍內(nèi)運(yùn)行。這意味著計(jì)算機(jī)平均每秒可以執(zhí)行大約 125,000 百萬條指令 (MIPS)。僅根據(jù)此質(zhì)量購買的處理器將提供運(yùn)行一些程序和應(yīng)用程序的功能。顯然,我們不只是期望打開一個(gè)網(wǎng)絡(luò)瀏覽器并在打開一個(gè)選項(xiàng)卡的情況下瀏覽網(wǎng)絡(luò)。隨著多核處理的出現(xiàn),工作頻率可以被放大。每個(gè)核心都以制造商規(guī)格中提供的速度運(yùn)行。這意味著相同的操作序列可能會(huì)在不同的內(nèi)核上同時(shí)運(yùn)行。更確切地說,并發(fā)進(jìn)程可以在不同的內(nèi)核上運(yùn)行,從而使處理器能夠同時(shí)處理多個(gè)進(jìn)程。

緩存

緩存是與處理器相關(guān)的第三個(gè)最重要的組件。緩存充當(dāng)更小、更快的內(nèi)存存儲(chǔ)設(shè)備。處理器將經(jīng)常使用的數(shù)據(jù)存儲(chǔ)在適當(dāng)?shù)奈恢谩K兄诤?jiǎn)化數(shù)據(jù)傳輸并通過減少訪問內(nèi)存的平均時(shí)間來提高效率。

現(xiàn)代處理器包含多個(gè)緩存源。處理器上最常見的緩存層次結(jié)構(gòu)是多級(jí)緩存。通常,有三級(jí)緩存;級(jí)別 1 (L1)、L2 和 L3。這些緩存相互結(jié)合運(yùn)行以存儲(chǔ)處理器將使用的最重要的數(shù)據(jù)。處理器檢查 L1 緩存中是否有它需要的數(shù)據(jù),如果處理器找不到它需要的數(shù)據(jù),則進(jìn)入下一級(jí)緩存。

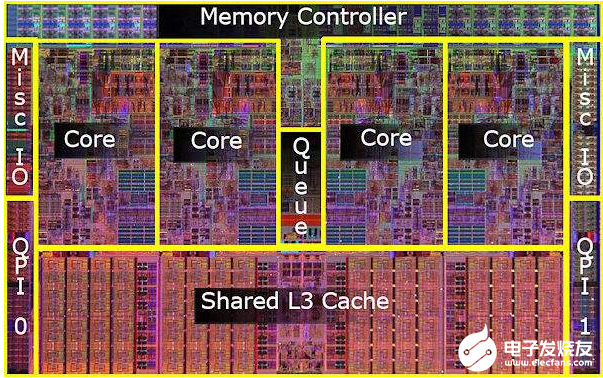

高速緩存在制造過程中以電氣方式實(shí)現(xiàn)到芯片中。隨著多核處理的引入,人們認(rèn)為共享緩存更有用的方法是為每個(gè)內(nèi)核提供自己的緩存。然而,這將包括更多的布線和跨內(nèi)核延遲的增加。因此,現(xiàn)代處理器只有 1 個(gè)緩存層次結(jié)構(gòu),而不是跨內(nèi)核拆分它們。

多核、單緩存處理器芯片

在選擇現(xiàn)代處理器時(shí),查看 L3 緩存是最有益的。許多操作系統(tǒng)的主要功能都存儲(chǔ)在 L1 和 L2 緩存中,讓 L3 緩存來填補(bǔ)空缺。具有 6MB-12MB 的 L3 緩存,處理器應(yīng)該能夠處理當(dāng)今所有的應(yīng)用程序。

結(jié)論

通過多核選擇、運(yùn)行頻率速度和緩存大小,很容易找到適合您需求的處理器。多核功能增加了高時(shí)鐘速度的實(shí)用性。每個(gè)內(nèi)核都可以以出廠設(shè)置的時(shí)鐘速度執(zhí)行指令。L3 Cache 會(huì)將重要數(shù)據(jù)存儲(chǔ)在其內(nèi)存中,并將其提供給下一個(gè)需要它的核心。每個(gè)現(xiàn)代處理器都將在其規(guī)格中包含這些細(xì)節(jié)。在選擇處理器時(shí),重要的是要考慮這三個(gè)組件之間的關(guān)系,以及它們?nèi)绾卧谶\(yùn)行時(shí)使功能受益。

資料來源:

英特爾。第一個(gè) Nehalem 處理器。數(shù)字圖像。英特爾.com。英特爾,2008 年 11 月 17 日。網(wǎng)絡(luò)。2013 年 2 月 10 日。.

施密茨,丹尼斯。通用雙核。數(shù)字圖像。維基百科。Np,2007 年 6 月 8 日。網(wǎng)絡(luò)。2013 年 2 月 19 日。

編輯:hfy

-

處理器

+關(guān)注

關(guān)注

68文章

19547瀏覽量

231867 -

振蕩器

+關(guān)注

關(guān)注

28文章

3875瀏覽量

139672 -

微處理器

+關(guān)注

關(guān)注

11文章

2314瀏覽量

83072 -

數(shù)據(jù)存儲(chǔ)

+關(guān)注

關(guān)注

5文章

987瀏覽量

51288

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

新競(jìng)爭(zhēng)力—ARM Cortex-A9處理器

新競(jìng)爭(zhēng)力—ARM Cortex-A9處理器

新競(jìng)爭(zhēng)力—ARM Cortex-A9處理器

新競(jìng)爭(zhēng)力—ARM Cortex-A9處理器

ARM Cortex-A9處理器

ARM Cortex-A9處理器的新競(jìng)爭(zhēng)力

如何實(shí)現(xiàn)處理器的速度跟外圍硬件設(shè)備的速度在一個(gè)數(shù)量級(jí)上呢

奔騰(Pentium)微處理器介紹

一文讀懂處理器,內(nèi)核,芯片三個(gè)概念的區(qū)別

如何選擇處理器的三個(gè)關(guān)鍵:工作頻率(時(shí)鐘速度)、緩存和內(nèi)核數(shù)量

如何選擇處理器的三個(gè)關(guān)鍵:工作頻率(時(shí)鐘速度)、緩存和內(nèi)核數(shù)量

評(píng)論