高性能控制器設計使用位片組件來提高速度和設計靈活性。常見的是每秒10-20百萬條指令(MIPS)的速度,設計人員可以利用位片設計的靈活性在一條指令中執行對速度有嚴格要求的運算。

位片與RISC架構

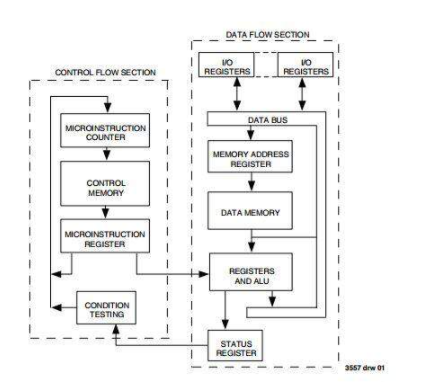

圖1中的典型位切片控制器設計示例。它由控制流部分和數據流部分組成。控制流程部分具有微指令計數器和控制存儲器。數據流部分。控制流部分具有一個寄存器和ALU元素(位片),以及一個數據總線上的數據存儲器和I / O寄存器。注意,控制存儲器和數據存儲器是分開的。使用單獨的數據指令存儲器稱為哈佛架構。分離的控制存儲器提供了與位片設計相關的某些速度,因為它與數據存儲器一起工作。這允許從控制存儲器中提取下一條微指令,同時可以從數據存儲器中讀取當前指令的數據。這與常規微處理器相反,常規微處理器交替地從同一存儲器中獲取指令和數據。將單個存儲器用于指令和數據的這種使用稱為Non Neumann體系結構。

比較圖1和圖2,位片控制器的框圖與典型的RISC CPU的框圖有明顯的相似之處。不同之處在于,控制器的控制存儲器和數據存儲器已被指令高速緩存所取代RISC CPU中的內存和數據高速緩存。指令和數據高速緩存存儲器的工作方式與它們的微代碼副本相同,不同之處在于它們都在公共主存儲器中包含數據的副本。程序員看到的是一個內存-主內存-而硬件則好像有兩個獨立的內存一樣工作。以這種方式,RISC計算機具有哈佛體系結構的速度優勢以及用于非諾伊曼體系結構的程序和數據的單個存儲器。

位片控制器框圖

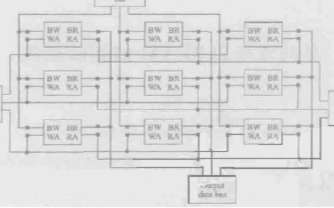

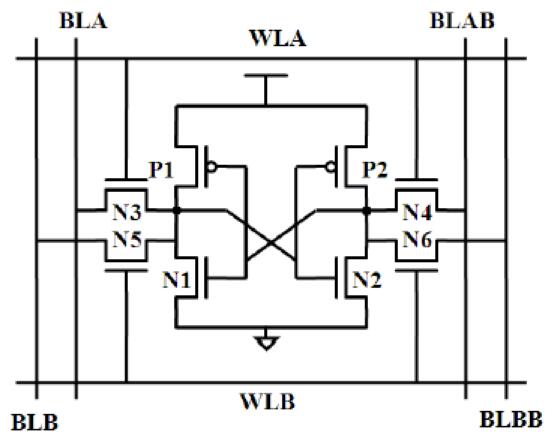

RISC體系結構的指令和數據高速緩存等效于在一個存儲器上具有兩個端口。通過使用高速雙端口內存代替高速緩存,我們可以將此概念應用于位片控制器。雙端口SRAM允許指令和數據端口同時且獨立地處于活動狀態,同時使雙方都可以訪問一組通用的SRAM單元。由于兩個端口都在同一存儲器中工作,因此數據流部分可以以與常規微處理器相同的方式加載和移動這兩個數據指令。結果,該設計用作常規的交互式軟件工具,例如解釋器和監視器,以用于系統開發和調試。

RISC CPU框圖

編輯:hfy

-

控制器

+關注

關注

112文章

16412瀏覽量

178711 -

cpu

+關注

關注

68文章

10887瀏覽量

212342 -

RISC

+關注

關注

6文章

463瀏覽量

83791

發布評論請先 登錄

相關推薦

采用基于字的檢測方法對單向雙端口SRAM進行測試

多片SRAM的可測試設計怎么優化?

單端口SRAM與雙端口SRAM電路結構

如何使用32位RTOS編程LS1046ARDB以太網?

SOC中多片嵌入式SRAM的DFT實現方法

雙端口SRAM中讀干擾問題,讀干擾的原理分析

如何對SRAM?進行分類

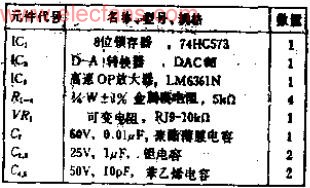

AN-325:12位模擬I/O端口采用AD7549雙12位DAC和8051單片機

32位MCU外擴SRAM芯片VTI7064MSME

應用分享| HPM6000系列片上SRAM揭秘

雙端口SRAM可產生無微碼的位片設計

雙端口SRAM可產生無微碼的位片設計

評論