Mentor的Symphony混合信號仿真平臺看起來將成為設計師工具箱中最有價值的工具之一

混合信號設計是指涉及模擬和數字電路交互相互作用以達到設計目的的設計。驗證這種設計非常棘手,特別是在采用最新的工藝幾何尺寸(例如當今的7納米技術)的最新,最大型硅芯片(ASIC,ASSP,SoC)的情況下。

這種設計很少在模擬和數字之間平均分配(這種設計稱為A / D或“ Big'A,Big'D'”)。取而代之的是,模擬可能會占主導地位,在這種情況下,設計可能被稱為A / d(“大A”,“小D”),“模擬為主”或“頂部模擬”。替代地,并且非常普遍地,數字可能占主導地位,在這種情況下,設計可以稱為a / D(“小A”,“大D”),“以數字為主導”或“頂部數字”。

除了一個或多個處理器內核之外,現代SoC可能還包含數億個邏輯門,這些邏輯門必須與擁有大量模擬內容的功能接口并進行驗證,例如PLL,ADC,DAC,SerDes,DDR IO等。清單繼續。

還有一個事實,就是設計正變得越來越深奧。例如,“頂置數字”芯片可以調用多個模擬IP功能,其中許多本身可以實例化數字子功能以進行控制和校準。

混合信號設計在廣泛的應用和細分市場中扮演著關鍵角色,每個應用和細分市場都具有不同的優先級,例如物聯網(低功耗),通信(高速),數據中心(低功耗和高速)以及汽車(可靠性)。

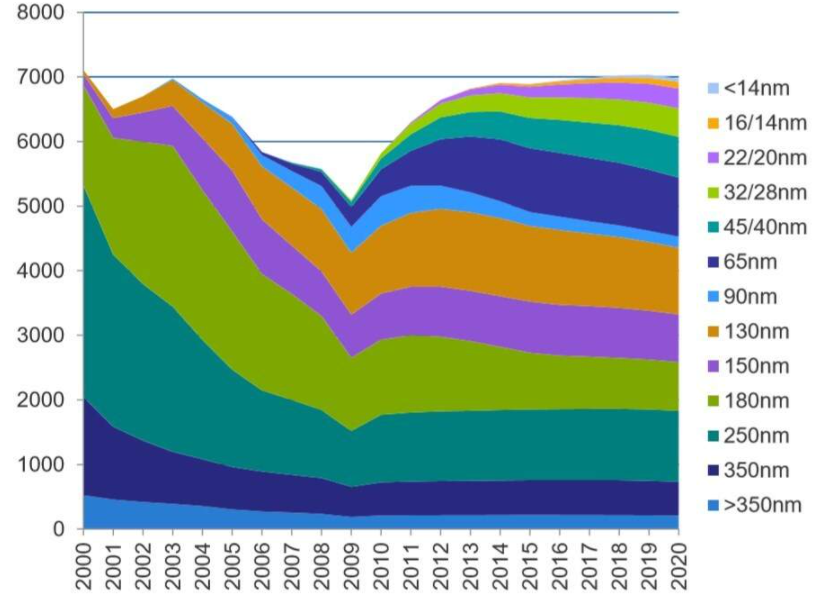

混合信號細分市場(來源:Mentor,西門子業務)

實際上,當今大約80%的芯片設計開始都是混合信號。至少可以這么說,以創新的電路拓撲和復雜的模數交互來驗證這種能力的設備具有挑戰性,并且現有的混合信號驗證解決方案已開始精疲力盡。

混合信號設計從流程節點開始。(來源:IBS)

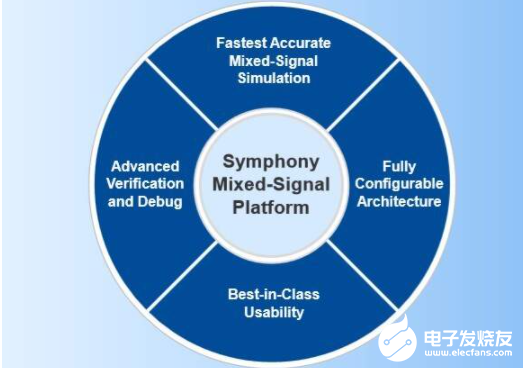

高性能計算,物聯網(IoT)和汽車應用中使用的片上系統(SoC)設備具有多個高性能,低噪聲混合信號接口。為了滿足此類設計的混合信號驗證需求,西門子業務部門Mentor宣布推出其Symphony混合信號平臺,該平臺將其代工廠認證的模擬FastSPICE(AFS)電路仿真器與業界認可的仿真器相結合。標準的HDL仿真器,可以快速,準確地驗證復雜的納米級混合信號集成電路。

Symphony混合信號平臺(來源:Mentor,西門子業務)

AFS模擬求解器最多可擴展至16個處理器內核,并支持支持布局后仿真所需的高容量,在提供出色性能的同時還提供了納米SPICE精度。Symphony的完全可配置體系結構可擴展到Mentor的所有模擬求解器,還支持行業領先的數字求解器,從而最大程度地重用了現有的驗證基礎架構。與傳統的混合信號模擬器相比,其結果是可以顯著提高性能。

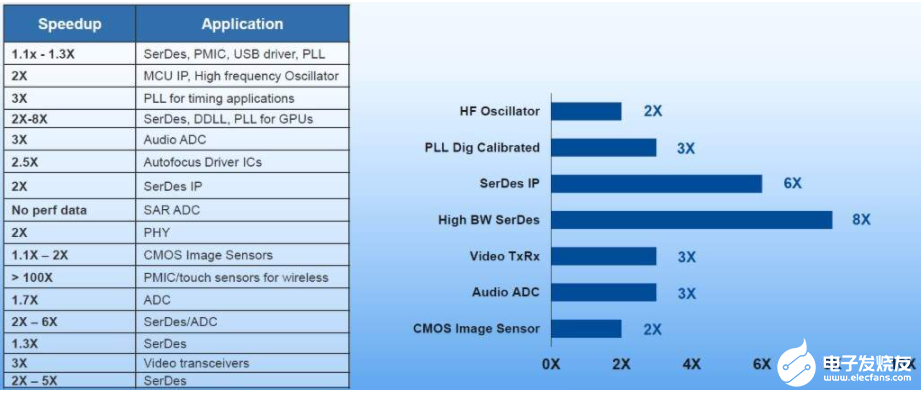

Symphony性能提升與傳統混合信號模擬器的對比(來源:Mentor,西門子業務)

Symphony提供了一個簡單直觀的使用模型,并與Mentor的EZwave Viewer集成在一起,該模型能夠處理巨大的波形數據庫并在幾秒鐘內加載千兆字節的數據。EZwave可以分析任何類型的時域或頻域波形:模擬,數字,眼圖,史密斯圓圖,極坐標圖或復數圖以及直方圖。Symphony還提供了多種提高生產力的功能,包括廣泛的A / D邊界元素支持,以及大量的高級驗證和調試功能,包括Hi-Z檢測,混合信號瞬態噪聲和混合信號IP表征。

當今難以置信的復雜,高容量,高性能混合信號集成電路的創建者需要他們所能獲得的所有幫助,而Mentor的Symphony混合信號仿真平臺似乎已成為設計師工具箱中最有價值的工具之一。

編輯:hfy

-

混合信號

+關注

關注

0文章

475瀏覽量

64962 -

物聯網

+關注

關注

2909文章

44701瀏覽量

373972 -

模擬器

+關注

關注

2文章

877瀏覽量

43252

發布評論請先 登錄

相關推薦

模擬和數字電路交互相互作用的混合信號設計

模擬和數字電路交互相互作用的混合信號設計

評論