中國集成半導體人才存量46.1萬人,人才缺口32萬人,平均每年人才需求為10萬人,但想入門半導體行業,學好HDL語言卻并不太容易。

做好FPGA,入門半導體行業,需要從硬件的角度思考開發的過程,理解IDE工具工作背后的深層次含義,學習HDL不要一上手就寫代碼,切記盲目的使用浮點,隨意的進行除法和開方等運算,這和FPGA本身的特性及硬件結構相關,時序分析也并不難,但一定要理解時序分析的本質原因,理解清楚這5條準則,其實用哪款FPGA都不會太難。

1、學習FPGA切記一開始就寫代碼,一寫就是好多年!

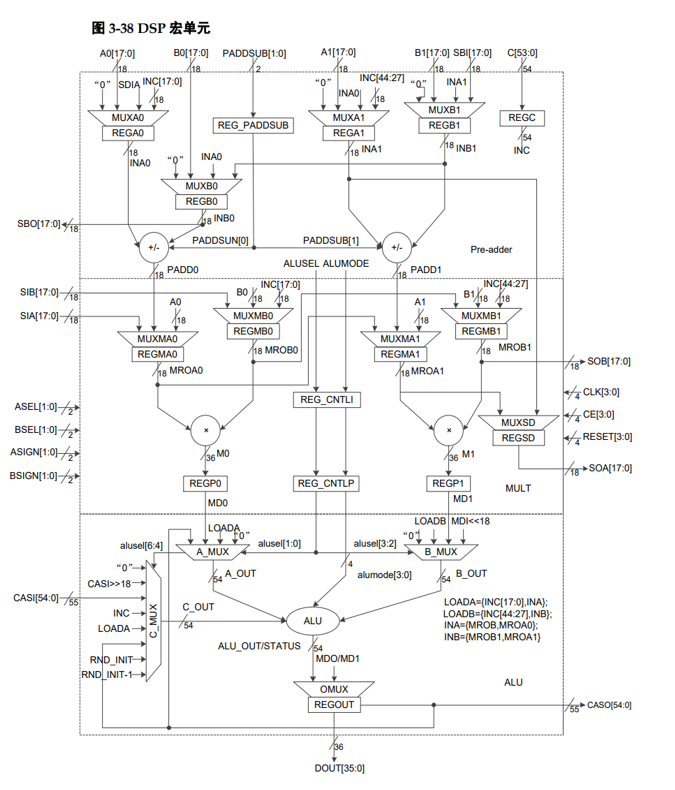

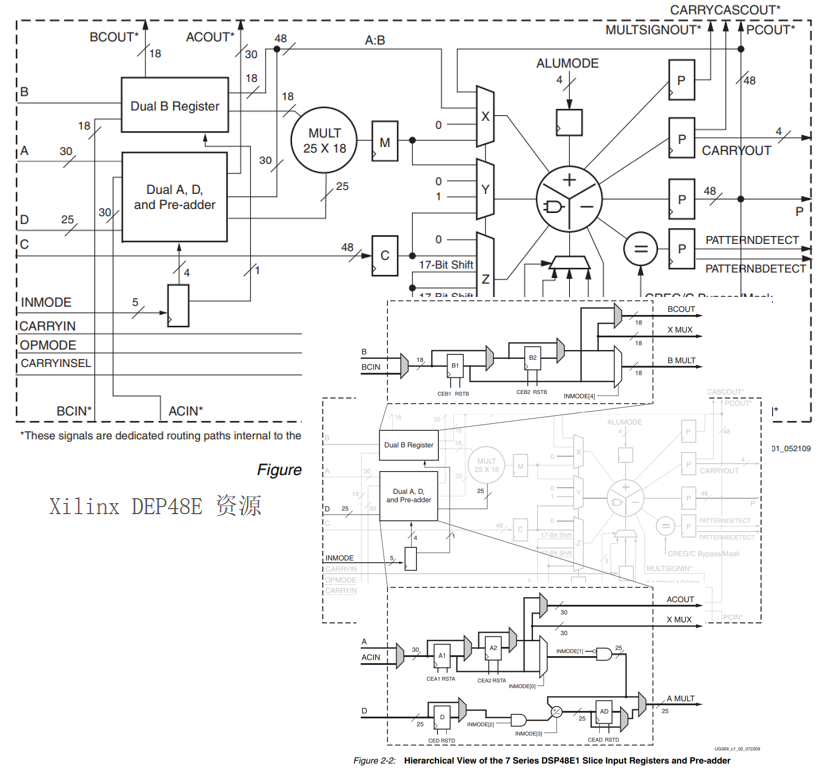

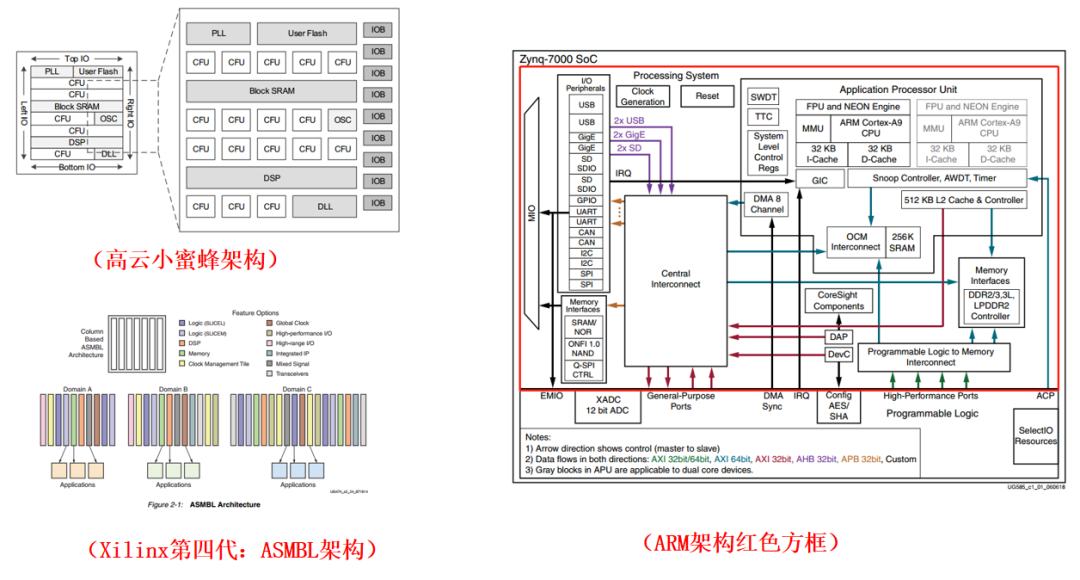

FPGA作為典型的硬件開發過程,其難點在于FPGA硬件的深刻理解,優秀的FPGA工程師是基于數學模型+FPGA底層硬件的理解去優化代碼,而不是根據算法,在不清楚FPGA硬件情況下直接用HDL進行描述,這里我們通過兩款FPGA器件的DSP架構,和大家分享一下在數字信號處理過程中FPGA代碼的優化過程。

Gowin DSP資源

Xilinx DEP48E資源

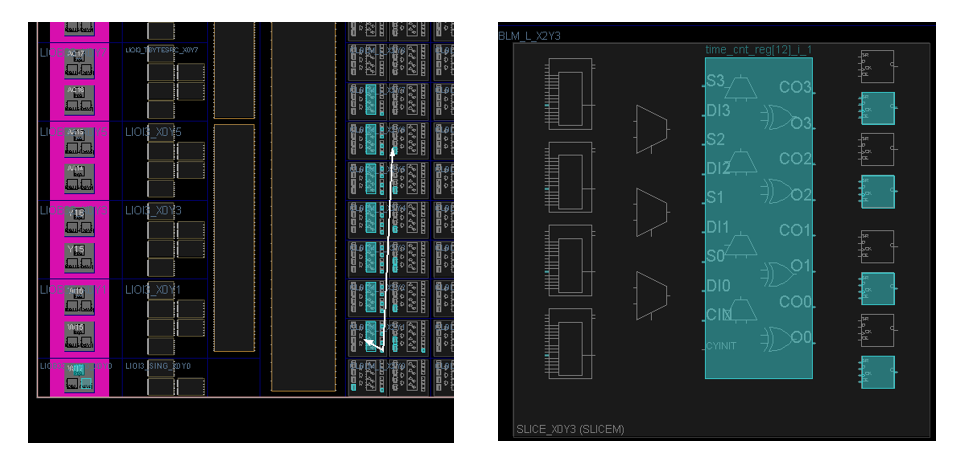

2、需要深刻理解IDE工具的背后邏輯!

Xilinx第四代ASMBL FPGA底層架構

FPGA開發者通常的開發過程是寫好代碼,然后修改語法錯誤,按照工具的先后流程點擊相關選項,下載代碼,可是你是否思考過,所謂的綜合,布局布線,物理約束,時序約束等背后深層次含義以及IDE相關參數設置對我們設計的影響。

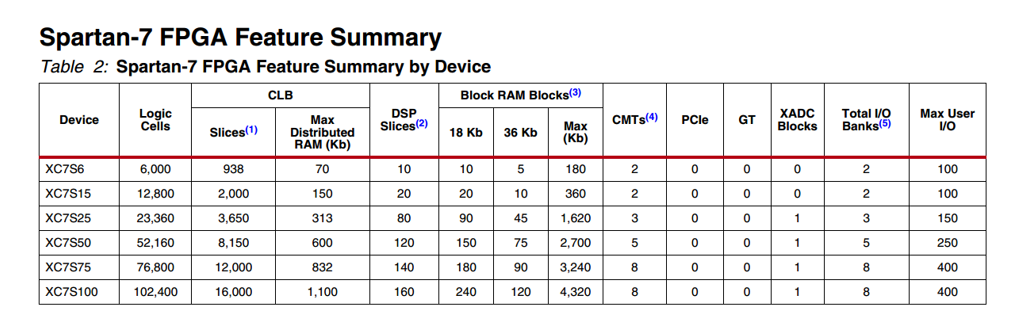

3、不要盲目的浮點,開方,除法,指數運算!

在數字信號處理過程,我們通常建議用戶先將浮點數據進行定點量化,碰到開方運算,我們通常建議是否可以簡化成絕對值和平方再進行處理,盡量避免除法運算,那背后的邏輯又是什么呢?

Xilinx高效低成本Spartan-7 FPGA器件特征

4、時序約束和時序分析沒有想象中的那么難!

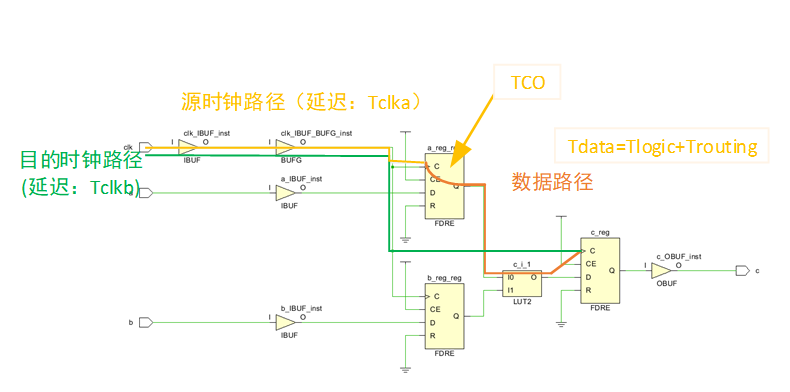

周期約束,輸入輸出延遲約束,生成時鐘約束,時鐘應該走全局時鐘網絡,要進行多周期約束,設置偽路徑這些時序約束中常用的技巧,是否都清楚背后的邏輯,這個部分想和大家一起探討時序約束底層的邏輯。

時序分析必需的三條路徑:源時鐘、數據、目的時鐘路徑

5、如果你理解了底層,用任何一家FPGA原廠都差不多!

有一個有趣的統計:FPGA大部分的問題是由跨時鐘域導致,如果你真正理解FPGA,進行FPGA代碼的移植都不會太麻煩,而最終選擇哪家的FPGA其實也就不太重要,因為萬變不離其宗。

責任編輯:xj

原文標題:FPGA認清這五大原則,想學不好都難!

文章出處:【微信公眾號:電子發燒友網】歡迎添加關注!文章轉載請注明出處。

-

FPGA

+關注

關注

1629文章

21729瀏覽量

603009 -

半導體

+關注

關注

334文章

27290瀏覽量

218090 -

HDL

+關注

關注

8文章

327瀏覽量

47377

原文標題:FPGA認清這五大原則,想學不好都難!

文章出處:【微信號:elecfans,微信公眾號:電子發燒友網】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

AFE031輸出信號的波形不會改變,是哪里出了問題?

DAC5686 IOUTA1,IOUTA2和IOUTB1,IOUTB2,這兩對差分哪個是P端?哪個是N端?

TPA3251D2接4歐負載,功率去到3/2左右就開始打隔,A和D通道去到削波都不會出現保護,為什么?

關于反相器CD4069UBE輸出負電壓的原理

采用的無源麥克輸出信號為2-5mV,請問采用哪款芯作為前置放大器比較合適?

要在AD采樣前加一個低通濾波模塊,濾除1K以上的高頻成分,用哪款運放比較合適?

淺談EMC設計準則

理解清楚這5條準則,用哪款FPGA都不會太難

理解清楚這5條準則,用哪款FPGA都不會太難

評論