EDN文章中介紹的一些技術向您展示了如何提高信號完整性,降低噪聲或降低功耗。我們作為工程師最大限度地提高性能的方法之一就是堅持建立設計規(guī)則。但是,如果遵守這些規(guī)則會增加成本并使您的產(chǎn)品無法銷售?這是低成本嵌入式和消費產(chǎn)品設計人員經(jīng)常面臨的困境。

為了深入了解這種產(chǎn)品,我們在Mentor Graphics對BeagleBone Black進行了分析,BeagleBone Black是許多面向制造商和業(yè)余愛好者的低成本微控制器板之一。我們的分析表明,“黑色”的設計師是如何做出許多工業(yè)產(chǎn)品設計師不需要進行折衷的。由于BeagleBone系列的無畏設計師發(fā)布了他們的設計,原理圖,布局和代碼,供我們其他人進行審查和改進,因此我們可以從信號完整性的角度對其進行分析和仿真。我們的分析揭示了有關設計師在保持性能,降低成本的同時進行權衡取舍的故事,我們可以將這些經(jīng)驗教訓應用到我們自己的設計中。

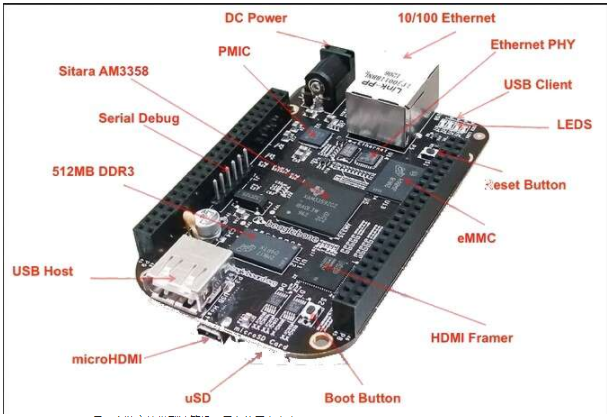

Black最初于2013年發(fā)布,是開放源代碼愛好者計算機家族的一部分。它圍繞德州儀器AM355x“ Sitara”處理器構建,具有512 MB的板載RAM,2 GB的板載閃存以及以太網(wǎng)和HDMI端口。Black(圖1)隨Debian Linux一起提供在板載閃存中,帶有micro-SD卡插槽可用于重新刷新板載內(nèi)存或直接托管操作系統(tǒng)。黑色已被較新的型號取代,不再是最先進的設備。它仍然可以在亞馬遜上以65美元的價格購買。

圖1. BeagleBone Black是一臺獨立的微型計算機,只有信用卡大小。

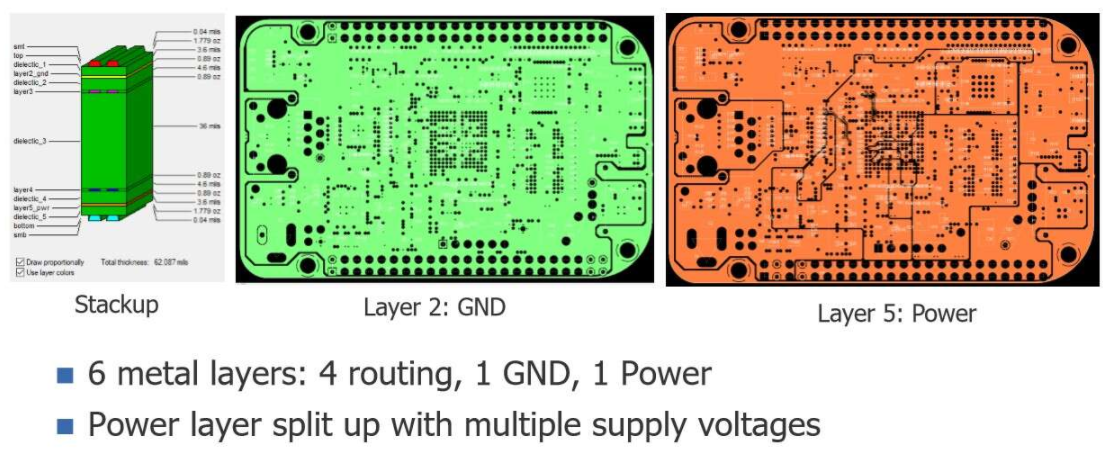

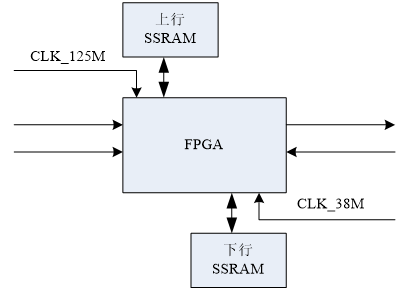

一旦我們了解了Black的堆棧,設計低成本系統(tǒng)的挑戰(zhàn)就變得顯而易見(圖2)。該電路板只有四個布線層和兩個平面層,電源平面層被切成小塊,以適應運行該電路板所需的不同電壓。“最佳實踐”高速設計告訴我們,信號在芯片之間傳播時,我們應保持恒定的參考電壓,并在可能的情況下將其接地。雙倍數(shù)據(jù)速率(DDR)存儲器已長期使用電源參考信號來適應雙列直插式內(nèi)存模塊(DIMM)設備上的有限層數(shù);顯然,我們在這里會遇到同樣的問題,我們必須與在其上切成小塊的參考平面抗衡。

圖2.黑色的電源層分為多個部分以適應不同的電壓。

注意中間電介質在疊層中的厚度。頂部和底部(電氣)相距較遠。原因很明顯:為了使板具有足夠的機械剛度,必須將其確定為一定的厚度,而較大的中心芯線是實現(xiàn)此目的的最佳方法。這意味著我們不能依靠嵌入式電容來對電源層和接地層進行解耦,因此任何從上到下穿越的信號過孔都需要附近的去耦電容器來承載其返回電流,并且這些電容器的有效性受到以下因素的限制:電容器環(huán)路電感。

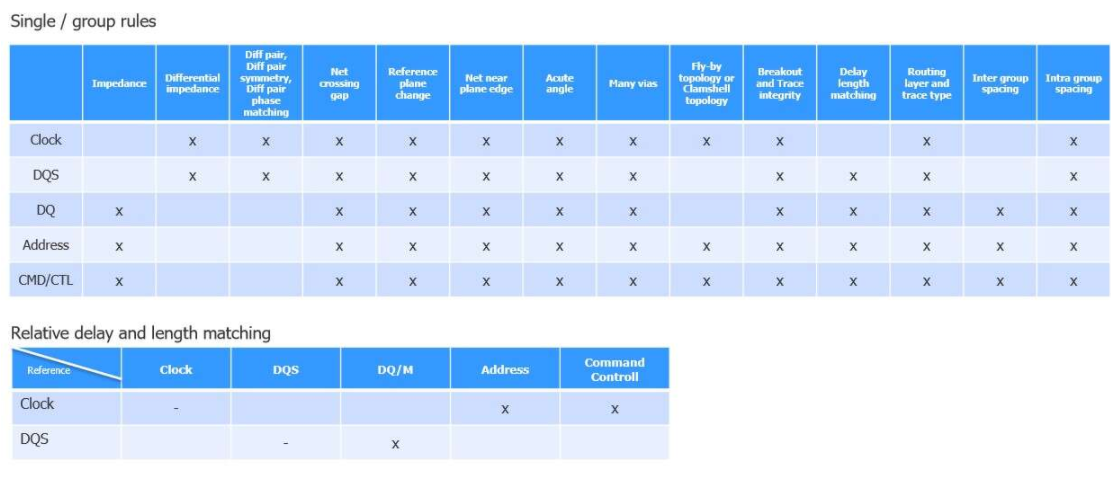

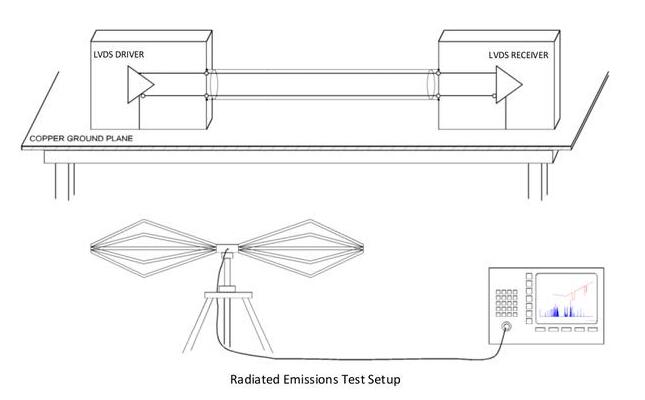

黑色上的DDR3接口(圖3)非常簡單。處理器直接與單個DRAM芯片對話。從原理圖和布線的角度來看,沒有比這更簡單的了。事實證明,簡單不一定意味著容易。Black的DDR3接口有一些有趣的故事,以講述創(chuàng)建低成本設計的含義。我們將從最佳實踐/設計指南的角度來解決這一問題-DDR3定義了一些物理和電氣設計目標,這些目標必須滿足才能使設計正常工作。

圖3.黑色DDR3接口直接與單個DDR存儲器芯片對話。

DDR3設計規(guī)則

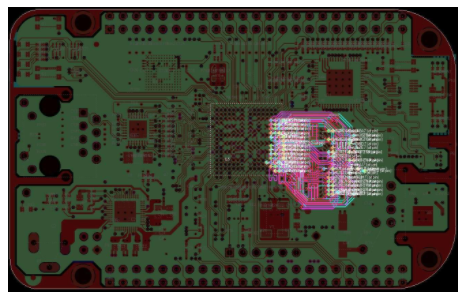

下面顯示了DDR3接口的一些常見物理布局設計規(guī)則(圖4)。不同的團隊對矩陣的定義會有所不同-尤其如此,因為DDR3的JEDEC規(guī)范僅定義了接口的DRAM端。不同的控制器將具有不同的電氣和時序要求,這可能會影響設計的放置和布線方式……但是基本思想仍然是相同的。

圖4.常見DDR3設計規(guī)則示例。

這些構成了“最佳實踐”設計規(guī)則的主體,可以用作放置和布線DDR3設計的起點。然后應使用布線后信號完整性和時序分析來分析布線設計板,以識別和解決任何潛在問題。但是,通常情況下,會根據(jù)最佳實踐規(guī)則放置和布線設計,并且在制作過程中不會進行信號完整性仿真。為什么?因為詳細的信號完整性和時序分析是大多數(shù)設計人員無法企及的。

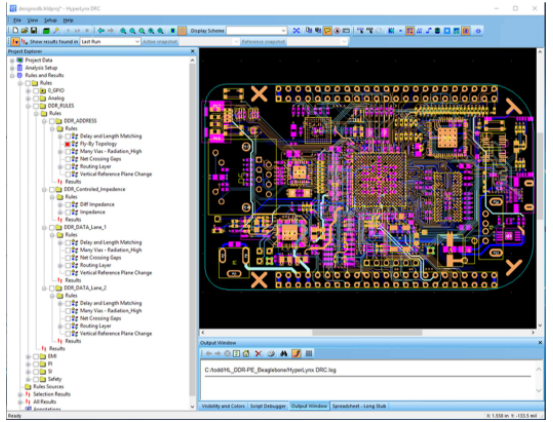

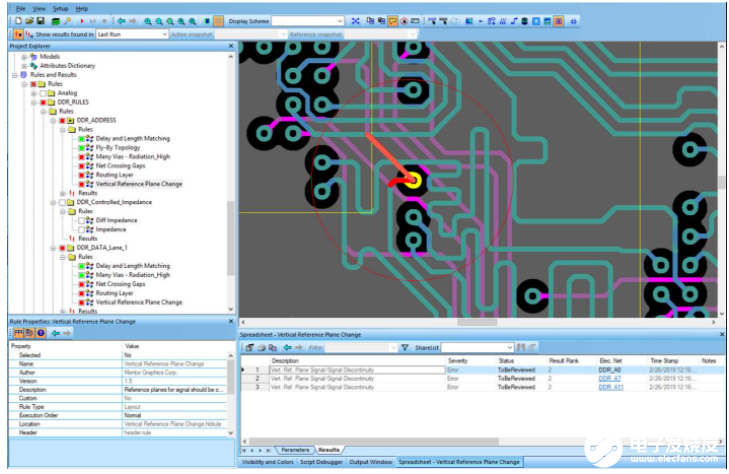

圖4中的物理和電氣規(guī)則足夠具體,我們可以從設計布局中自動檢查它們(圖5)。在這種情況下,我們?yōu)镈DR3數(shù)據(jù)網(wǎng),地址網(wǎng)等定義了特定的規(guī)則集。根據(jù)設計是否通過相應的檢查,每個特定規(guī)則旁邊的框將以紅色或綠色突出顯示。

圖5.自動檢查DDR3設計規(guī)則。

請注意,我們正在完成的Black設計上運行這些檢查。如果準則規(guī)則如此重要,那么黑方將如何無法通過所有這些檢查,并且仍然可以很好地工作以成為運輸產(chǎn)品?好吧,事實證明,指導方針就是:指導方針。違反準則并不意味著設計就行不通,而只是意味著存在一個問題,需要更仔細地調查和理解。如果分析表明該設計仍然可以運行,則可以免除違規(guī)并繼續(xù)進行。如果違規(guī)是一個真正的問題,那么您可以糾正問題并重復該過程。

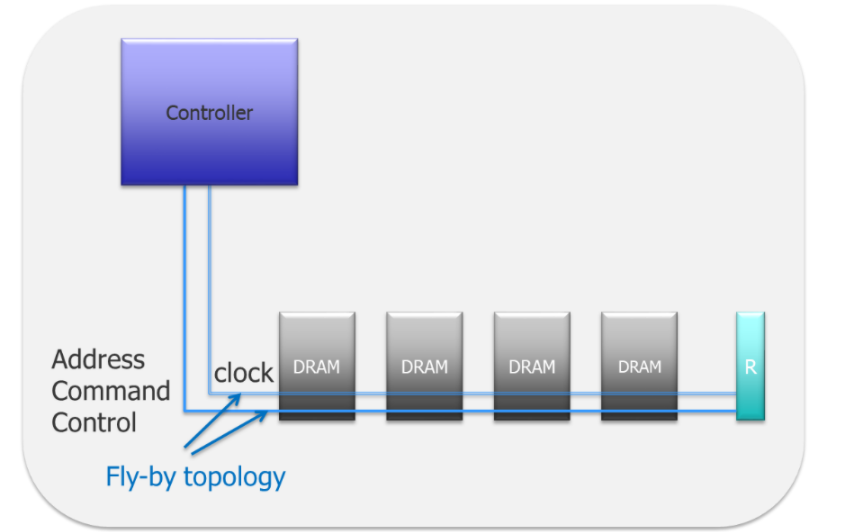

DDR3使用“飛越”拓撲來路由地址,命令/控制和時鐘信號(圖6)。信號由控制器驅動,并以菊花鏈的方式通過不同的DRAM路由,并在線路末端并聯(lián)一個終端。這種方案以到達每個設備的時鐘的時滯為代價,使每個DRAM的時鐘信號質量最大化。這與用于DDR2和更早技術的“時鐘樹”方案形成鮮明對比,后者試圖在每個設備上同步時鐘的到達。時鐘樹方法必然涉及分叉軌跡,這會導致反射,從而降低信號質量。這些反射在DDR2速度下是可以容忍的,但在DDR3及以后的速度下是不能容忍的。

圖6.連接多個DRAM設備時,DDR3使用“ Fly-by”拓撲進行地址和時鐘路由。

對于DDR3及更高版本,這些網(wǎng)絡在線的末端并聯(lián)端接,以最大程度地減少反射,否則會影響信號質量。時鐘到達不同DRAM的時滯表示DRAM將在稍有不同的時間將數(shù)據(jù)發(fā)送回控制器(讀取)。這也意味著控制器將需要在稍有不同的時間將數(shù)據(jù)發(fā)送到DRAM(寫),以確保符合DRAM上的DQ / DQS / CLK關系。控制器處理這些時序偏移的過程稱為讀取均衡和寫入均衡。

第一個問題是我們需要調查與地址網(wǎng)的關系。網(wǎng)絡上的并聯(lián)終端電阻丟失。黑人設計師為什么要這樣做?答案非常簡單-成本。并聯(lián)終端電阻要花錢并占用PCB面積,這兩者在像Black這樣的設計中都是很寶貴的。在像這樣的大批量,低成本應用中,設計師可能不想添加不必要的東西,即使它是“標準”設計指南的一部分。哪個提出了問題–我們?nèi)绾未_定沒有這些電阻的設計就能工作?我們將如何進行需要證明的設計分析?

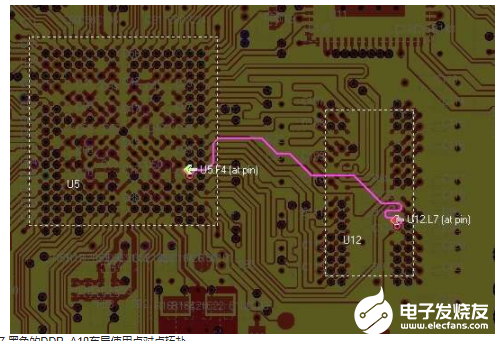

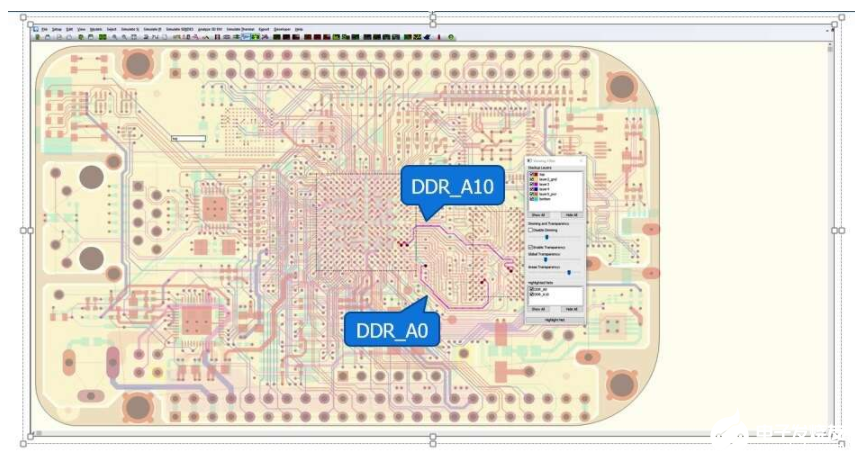

DDR地址線10(DDR_A10)顯示在圖7的PCB布局中(如果您想知道為什么我們不選擇DDR_A0,我們將在后面進行介紹)。處理器在左側,單個DRAM在右側。現(xiàn)在,圖片開始成為焦點-Black的地址總線不是點對點的多點拓撲。請記住,在存在多個負載時,DDR3中并行終止的目的是管理地址/命令/控制網(wǎng)絡的信號質量。考慮到這一點,讓我們集中討論Black上的地址線實際上需要提供什么樣的信號質量,而不是在更一般的情況下DDR3準則告訴我們的。

圖7.黑色的DDR_A10布局使用點對點拓撲。

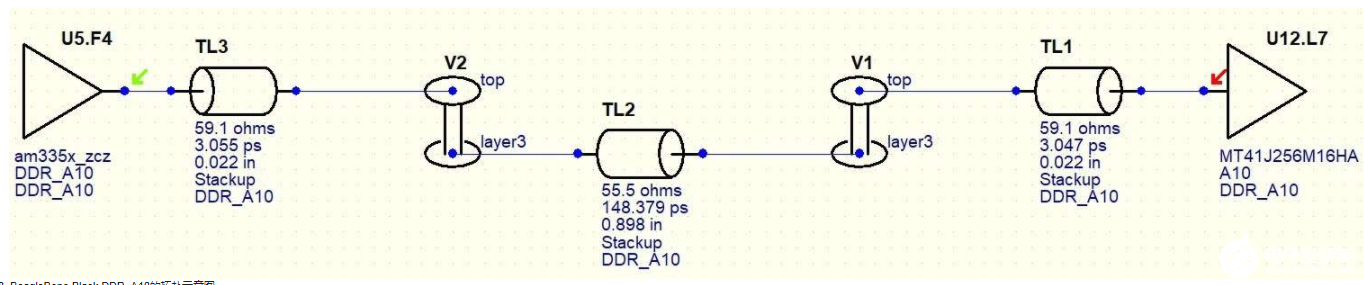

圖8顯示了該網(wǎng)絡的布局前示意圖。這種表示形式特別有用,因為它使我們能夠對網(wǎng)絡進行快速的“假設分析”更改,以探討它們對信號行為的影響。Black的最大DDR3數(shù)據(jù)速率為1600 MT / s,因此讓我們從運行模擬開始,看看信號質量如何。

圖8. BeagleBone Black DDR_A10的拓撲示意圖。

知道會發(fā)生什么

讓我們先退后一步。信號完整性專家Eric Bogatin提供了高速設計的經(jīng)驗法則,其中第9條法則指出:“切勿在沒有預測您首先看到的情況下運行仿真。”那是非常好的建議。如果您不知道期望得到什么結果,您如何知道模擬是否正確運行?

仿真通常會運行到完成并產(chǎn)生結果,但是建模或設置問題有很多方法會影響結果的有效性。考慮到這一點,您應該驗證基本假設,簡單地開始并以受控的方式增加模擬的復雜性,以便可以預測任何模擬實驗的結果。這與說仿真總是可以預測預期的結果不同,但是它確實表示可以解釋和解決意外的結果。

您在這里應如何應用該原則?在點對點拓撲和未端接的接收器中,您可能希望入射波形的電壓加倍,并反射回驅動器。如果驅動器的輸出阻抗與傳輸線的阻抗相匹配,則驅動器將吸收反射信號。驅動器的輸出是否與線路阻抗匹配,或者是否使用串聯(lián)電阻將驅動器的(較低)輸出阻抗與線路阻抗匹配,就是這種情況。該技術被稱為“串行端接”,是一種使用點對點拓撲結構控制信號質量的有用方法。它具有減少開關期間輸出驅動器所需功率的額外好處,這是一項額外好處。

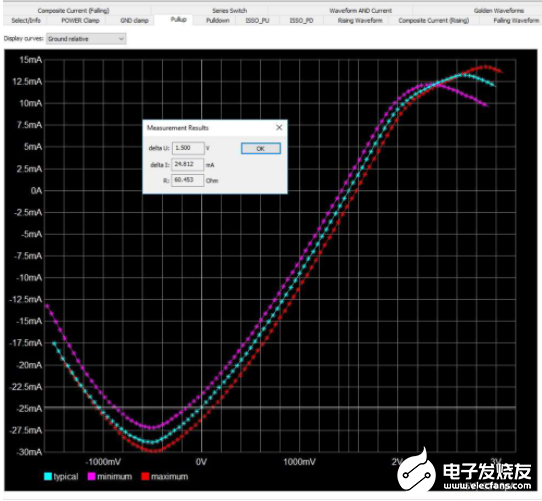

那么,我們?nèi)绾闻宄绾螢锽lack設置串聯(lián)終端?好吧,您需要找到一個驅動器設置,其中驅動器阻抗與板上走線的傳輸線阻抗匹配,我們知道大約為60Ω。我們在IBIS模型中查看了處理器的驅動器電壓與電流(V / I)曲線,以了解是否可以找到合適的設置。

我們繪制了處理器地址線輸出緩沖器的上拉/下拉曲線,并使用該曲線的斜率來計算驅動器的有效輸出電阻。黑色的地址輸出驅動器是可配置的,具有以下設置:5 mA,6 mA,7 mA,8 mA,9 mA,10 mA,11 mA和12 mA。當我們在輸出阻抗上繪制不同的設置時,我們發(fā)現(xiàn)7 mA的輸出提供了與我們要尋找的阻抗的良好匹配(圖9)。

圖9.使用處理器模型的地址線V / I曲線的斜率來計算輸出阻抗。

接下來,我們對7 mA左右的設置進行了仿真,并查看我們的預測如何與結果匹配。

并非總是需要額外的余量

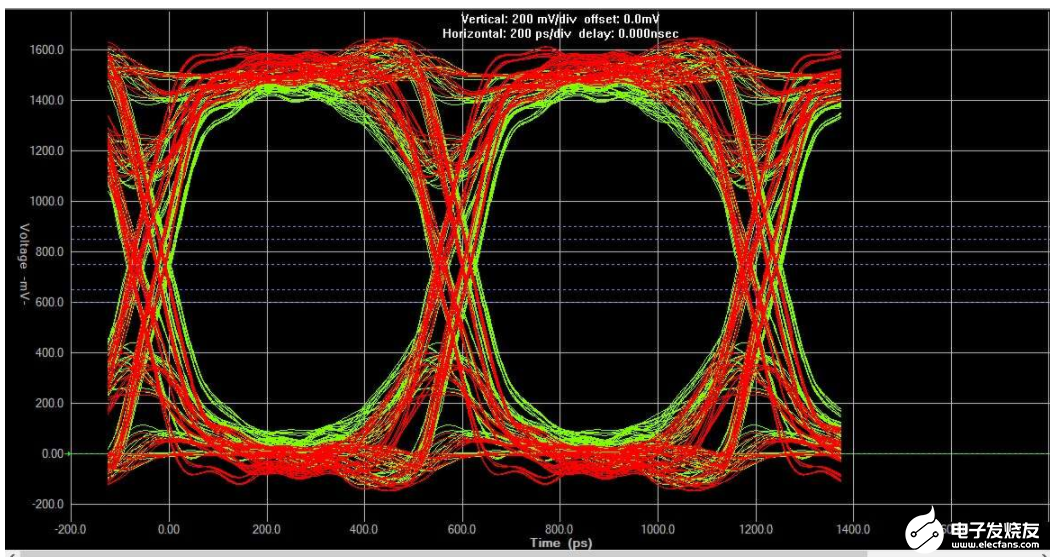

正如預期的那樣,7 mA(圖10眼圖的綠色區(qū)域)設置工作得很好。但是,我們注意到8mA設置提供了額外的設計余量。為什么?因為當我們僅考慮使驅動器阻抗與線路阻抗匹配時,我們并未考慮接收器輸入端的電容性負載,因為電容性負載需要額外的電流才能充電。這是通過仿真進行受控實驗的一個很好的例子–我們沒有無法獲得我們期望的結果,但是我們解釋了原因并因此獲得了見識。

圖10. 1600 MT / sec時7 mA和8 mA驅動器的眼圖。顯示7 mA可產(chǎn)生更寬的眼圖張開度。

我們還運行了其他驅動器強度,未在圖10中顯示。我們注意到,驅動器設置高于8mA會增加波形的峰峰值電壓,但這并沒有進一步擴大視野。換句話說,更強地驅動信號只會給系統(tǒng)增加噪聲。

說實話,由于DDR3地址網(wǎng)絡是設計為端接的,因此無論選擇哪種設置,我們都有很多眼圖余量–我們甚至可以將驅動器的強度降低到5 mA,但仍然有足夠的余量。網(wǎng)絡末端的并聯(lián)端接通常將峰峰值信號擺幅減小一半,因此我們有足夠的余量來處理。

DDR3設計的另一個標準經(jīng)驗法則是,信號在芯片之間傳輸時應保持恒定的參考電壓。參考電壓可以是GND或DDR I / O的電壓軌,但是無論信號以哪個參考電壓啟動,該參考電壓在信號的整個路徑上都應保持一致。在信號改變層的情況下,相關的參考平面需要在附近具有縫合過孔,以減輕返回路徑的影響(圖11)。

圖11.當信號改變層時,信號參考平面通常需要縫合通孔以保持參考一致性。

信號可以更改包含兩個不同參考電壓的參考平面,只要兩個參考平面在信號過孔附近充分解耦即可。這樣做的問題是,去耦電容器所涉及的電感必然比通孔拼接策略要大,因此通常可以避免這種情況。

當我們在黑色(圖12)上運行DDR設計規(guī)則檢查時,我們發(fā)現(xiàn)幾個地址網(wǎng)違反了該準則,并同時參考了接地層和電源層進行了布線。為什么?因為黑方只有兩個參考平面,所以設計人員沒有足夠的空間在上兩層存儲DDR信號。他們將所有數(shù)據(jù)信號路由到上層微帶線和帶狀線層(參考GND)。這是有道理的,因為DQ信號以地址信號頻率的兩倍運行。但是,某些地址信號是同時參考GND和DDR電源進行路由的,這意味著返回電流必須在路由中間找到這兩個平面之間的路徑。

這就引出了一個問題:這對信號質量有多大影響?黑人設計師如何知道他們負擔得起?我們來看兩個地址信號(圖12)。

圖12.黑色上的地址線。

地址線更改平面

地址線10(圖13)從頂層(微帶)啟動,在其大部分長度上向下過渡到layer3,然后切換回頂層以連接到設備引腳。由于頂層和第3層位于第2層的任一側(接地平面),因此返回路徑接近理想狀態(tài)。返回電流不受干擾,因為它永遠不會改變層數(shù)。

圖13.地址線10穿過BeagleBone Black PCB的路線。

地址行0是另一個故事(圖14)。它從頂部微帶層(參考接地)啟動,切換到底部帶狀線層(參考電源),切換回第3層(參考接地),然后在頂層(參考接地)結束。這意味著A0在大約1英寸的范圍內(nèi)兩次切換其參考電壓。從控制器到DRAM所需的時間。有什么影響?

圖14.地址線0沿著黑色的四個PCB層中的三個層移動。

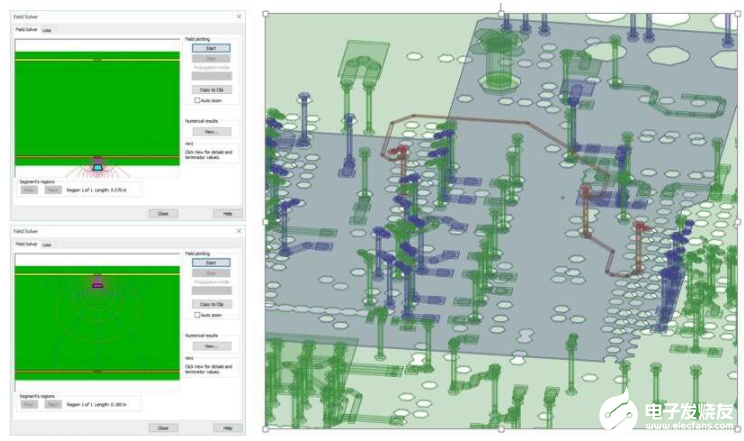

基本的信號完整性分析始終假設信號的返回路徑是理想的。自IBIS于1993年問世以來,所有信號完整性工具均是如此。高速信號與系統(tǒng)的配電網(wǎng)絡(PDN)相互作用,而這些相互作用只會使信號降級。對這些交互進行建模和仿真的仿真工具被稱為“ Power-Aware”仿真工具。對于黑色,這是我們需要量化A0信號更改參考電壓的影響的分析類型。Power-Aware仿真是信號完整性方面的一個相對較新的發(fā)展-早在2012年,Black設計師肯定還沒有使用它,但是我們今天可以使用它來量化其決策的影響。

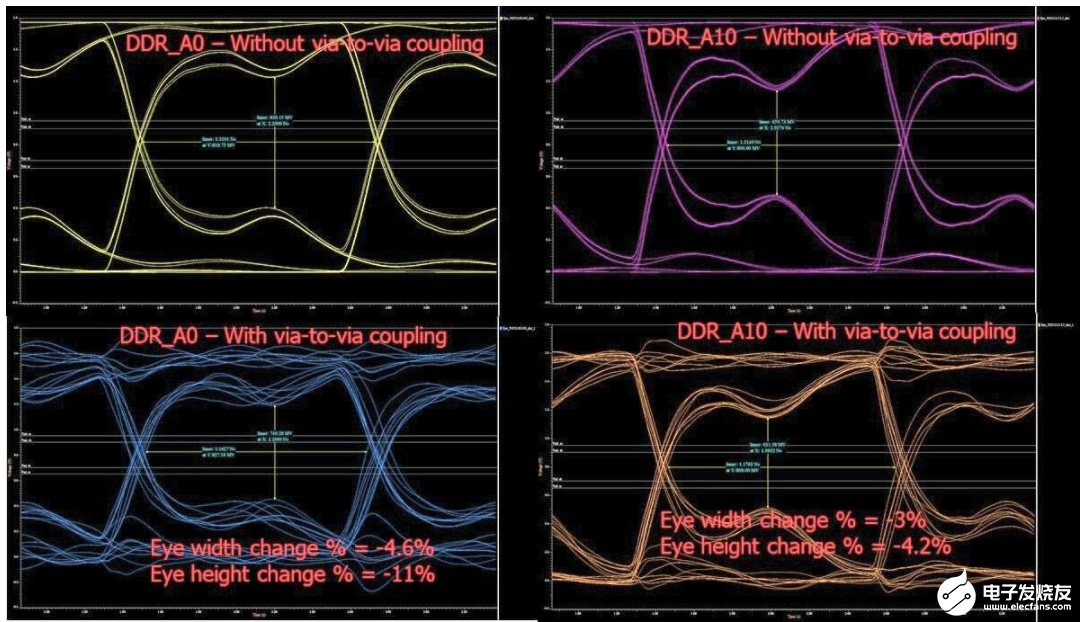

圖15中圖的左側顯示了A0信號,而右側顯示了A10。頂部的圖顯示了具有理想返回路徑的網(wǎng)絡仿真,而底部的圖顯示了當考慮信號的實際返回路徑時眼圖裕量如何受到影響。對返回路徑進行建模時,A0信號的眼高降低了A10的眼高的兩倍。由于信號開始時有很大的余量,因此這仍然是可接受的信號質量。如果我們不是點對點運行信號,并且與并行端接相關聯(lián)的眼高降低,情況可能會有所不同。

圖15.功耗感知的仿真結果表明,即使眼睛高度顯著下降,仍然有足夠的睜眼余量供Black使用。

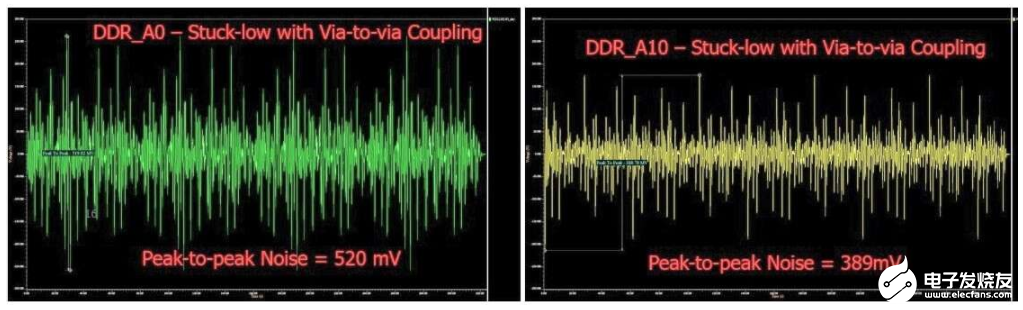

我們還可以評估由它們的鄰居的開關活動在這些信號上引起的噪聲。為此,我們通過將利息凈額穩(wěn)定在高或低狀態(tài)來將其視為受害凈額。我們在總線上的其他網(wǎng)絡上放置一個隨機模式,并測量耦合到目標信號上的噪聲。我們在受害網(wǎng)上看到的任何波動都是耦合噪聲的結果。不出所料,圖16中A0上的噪聲大于A10上的噪聲。

圖16.建模返回路徑時的地址線噪聲耦合

即使在接近理想的返回路徑的情況下,耦合噪聲似乎也很高–接近390 mV!請記住,幅度和時間是耦合噪聲的重要考慮因素,而不僅僅是幅度本身。如果在采樣(定時)信號時沒有發(fā)生耦合噪聲,則不會產(chǎn)生任何影響。對于這樣的并行總線,在信號切換時由于串擾會產(chǎn)生大量噪聲是很常見的,因為所有信號都一起切換。重要的一點是,在采樣信號時,噪聲已經(jīng)消失了,圖16并未對此進行描述。

切換信號基準電壓對A0的影響還不算太壞-設計具有足夠的裕度,這很重要。如果設計人員嚴格遵守DDR3設計的既定經(jīng)驗法則,他們可能會增加額外的電阻器,并可能增加一個平面對(以提供額外的接地層)。這些更改實際上不是必需的,只會使產(chǎn)品成本增加而沒有任何實際好處。設計師如何知道他們可以做到這一點?我們不知道–也許他們使用了原型和實驗室特性,并對其進行了仔細的測試。具有功耗意識的建模和仿真表明,即使違反了既定的DDR設計指南,該設計也可以有足夠的余量。

當然,我們知道,黑人從幾年前就開始工作了。但是,當今的大批量,低成本設計存在相同的問題-制造成本至關重要,僅遵循傳統(tǒng)的經(jīng)驗法則通常會導致設計過于昂貴而無法實現(xiàn)。因此,我們一直在努力展示現(xiàn)代分析工具如何幫助您確定在何處“違反規(guī)則”,何時何地以及如何進行。

—Todd Westerhoff是MentorGraphics的電子板系統(tǒng)部分的高速和模擬/混合信號系統(tǒng)設計產(chǎn)品營銷經(jīng)理。

編輯:hfy

-

處理器

+關注

關注

68文章

19275瀏覽量

229744 -

電容器

+關注

關注

64文章

6219瀏覽量

99588 -

DRAM

+關注

關注

40文章

2313瀏覽量

183461 -

DDR3

+關注

關注

2文章

276瀏覽量

42258 -

信號完整性

+關注

關注

68文章

1408瀏覽量

95461

發(fā)布評論請先 登錄

相關推薦

如何實現(xiàn)低噪聲和高精度的增強電源和信號完整性

【信號完整性】地彈噪聲對信號完整性的影響

PCB信號完整性

如何在汽車設計中降低功耗

提高信號完整性的PCB材料

信號完整性對EMC的影響有哪些

如何降低地彈噪聲對單板信號完整性影響

如何最大程度地降低地彈噪聲對單板信號完整性影響?

如何提高信號完整性,降低噪聲或降低功耗

如何提高信號完整性,降低噪聲或降低功耗

評論