Arira Design的信號完整性小組被要求重新設(shè)計現(xiàn)有的5GHz接地共面波導(dǎo)RF饋線,以提高客戶板上Wi-Fi子系統(tǒng)的性能。測量表明,饋線阻抗的阻抗約為38歐姆。

在進行仿真之前,原始設(shè)計發(fā)現(xiàn)了幾個問題,包括:

- 無法考慮阻焊層對走線阻抗的影響

- 在走線阻抗計算中未考慮PCB回蝕

- 附近的非參考地平面中的切口不正確

對現(xiàn)有的饋線進行了仿真,然后根據(jù)仿真結(jié)果改進了共面幾何形狀,以滿足50歐姆的阻抗要求。結(jié)果,該客戶報告說,使用新的PCB可以大大改善Wi-Fi性能。

本文討論了初始PCB設(shè)計的共面幾何形狀,上述三項的影響以及最終的共面幾何形狀。顯示了不同共面配置的電場圖,以說明接地共面設(shè)計可能發(fā)生的有意和無意耦合(假設(shè)讀者熟悉共面波導(dǎo)或CPW和接地共面波導(dǎo)的基本結(jié)構(gòu),或者GCPW)。

接地共面波導(dǎo)

由于現(xiàn)代電路板上Wi-Fi和藍牙集成的普遍性,接地共面波導(dǎo)在PCB設(shè)計中正變得越來越普遍。與傳統(tǒng)的微帶傳輸線相比,GCPW的一些優(yōu)勢如下:

更低的損耗:更多的電場線穿過空氣,而不是流過有損的PCB材料。這樣可以在運行于5GHz的PCB設(shè)計中使用價格更便宜的FR-4。

隔離:與微帶相比,GCPW線提供了更多的隔離,因為磁場線的約束更加嚴格。

靈活的幾何形狀:GCPW阻抗主要由走線和共面接地結(jié)構(gòu)之間的間隙控制。與微帶傳輸線相比,這在走線寬度上具有更大的靈活性。

較低的銅表面粗糙度損失:微帶線中的電流傾向于沿著走線的底部集中,走線的底部是最粗糙的銅(以增強與電介質(zhì)的附著力)。正確設(shè)計的GCPW傳輸線傾向于使電流集中在走線的邊緣,在走線的表面較光滑。

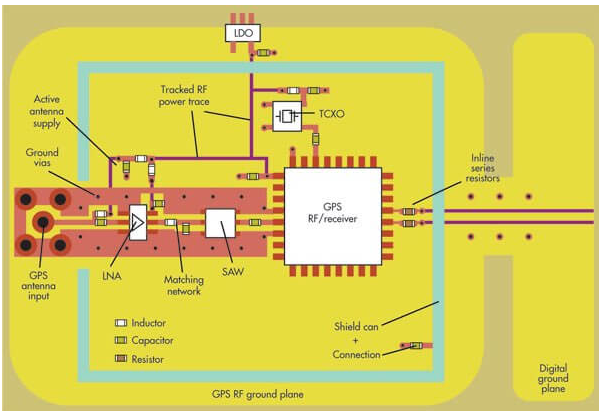

出色的匹配組件放置:大多數(shù)藍牙或Wi-Fi RF饋線需要串聯(lián)和/或并聯(lián)匹配組件。由于GCPW的接地線緊鄰走線,因此可以將并聯(lián)組件直接安裝在走線和共面接地之間,從而消除了與過孔相關(guān)的寄生現(xiàn)象。

可使用許多工具來計算GCPW結(jié)構(gòu)的阻抗,但是Internet上可用的免費工具通常會限制可分析結(jié)構(gòu)的類型。通常可以計算出基本結(jié)構(gòu),但近乎銅結(jié)構(gòu)的效果通常需要進行EM仿真才能正確建模。

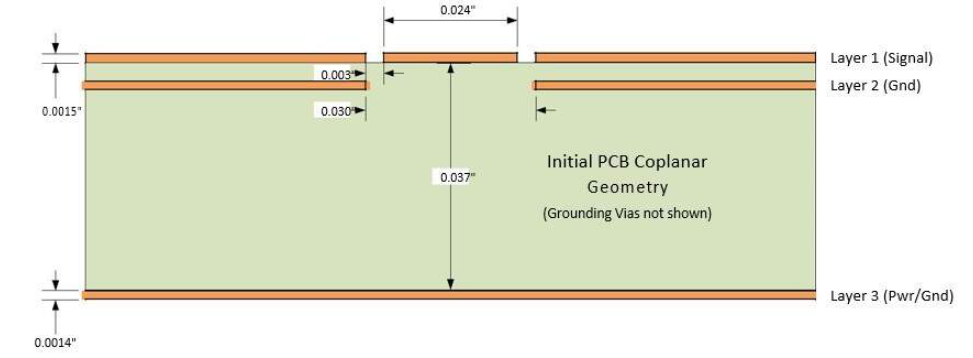

PCB說明

所考慮的PCB是使用FR4電介質(zhì),標(biāo)稱Dk(介電常數(shù))為4.2的消費類產(chǎn)品的高容量四層板。板的厚度約為45密耳。GCPW位于第1層,而接??地參考島位于第3層。第2層是接地平面層。第3層是電源平面層,也具有GCPW的接地參考島,第4層是信號層。直徑為8密耳的通孔將第1層接地層與第3層參考平面和第2層上的主接地層連接起來。

初始PCB上的接地共面波導(dǎo)幾何形狀是使用Internet上提供的免費軟件傳輸線計算工具設(shè)計的。GCPW的走線寬度約為24密耳。選擇該走線寬度以匹配Wi-Fi模塊和天線連接器的引腳尺寸。電鍍后的跡線厚度約為1.5密耳。共面走線位于地面參考平面上方約37密耳處。

(資料來源:Arira Design)

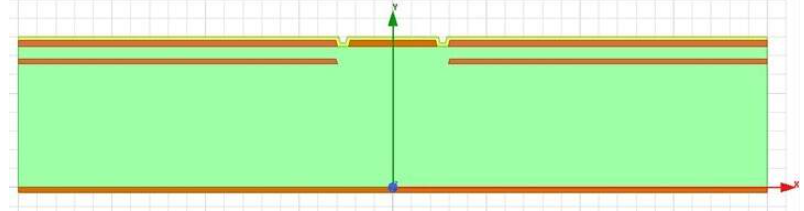

通過此輸入,我們的客戶最初使用的傳輸線計算工具確定共面間隙為3密耳。第2層接地平面上有一個切口。PCB設(shè)計人員將此切口的寬度與第1層上共面接地浮雕的寬度相匹配,以使第2層平面上的切口的寬度為30密耳,如上圖所示。

初步分析與模擬

當(dāng)檢查用于在初始板上設(shè)計共面幾何形狀的傳??輸線計算器時,發(fā)現(xiàn)該工具并未解決板上存在阻焊層的問題。同樣,它也沒有考慮到PCB回蝕。對于位于PCB外層的邊緣耦合結(jié)構(gòu),阻焊層和PCB回蝕會極大地影響走線阻抗,尤其是在結(jié)構(gòu)表現(xiàn)出強耦合的情況下。顯然,如果這些因素未包括在共面阻抗分析中,那么計算的準(zhǔn)確性就會受到影響。同樣清楚的是,靠近共面走線的第2層接地平面的存在也會影響走線阻抗。

考慮到這一點,進行了一系列模擬,以量化阻焊層,回蝕以及第2層接地平面與共面走線的緊密距離的影響。Ansoft的Q2D場求解器工具用于此建模。仿真及其結(jié)果如下所示:

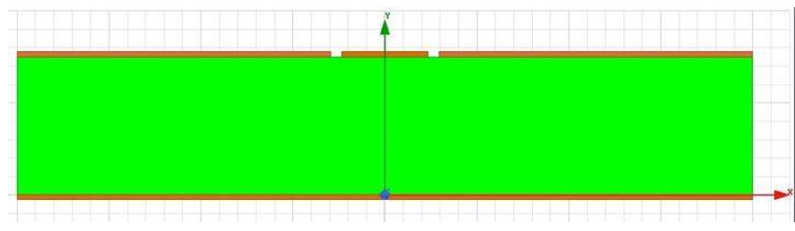

沒有阻焊層,沒有回蝕,沒有L2接地層:Q2D仿真報告的阻抗為43.0歐姆。另一款商用2D場求解器LINPAR報告的阻抗為42.7歐姆,與Q2D模擬顯示出極好的一致性。這是免費軟件阻抗計算器分析并錯誤地報告阻抗為50歐姆的結(jié)構(gòu)。

沒有阻焊層,沒有蝕刻層,沒有L2接地層(來源:Arira Design)

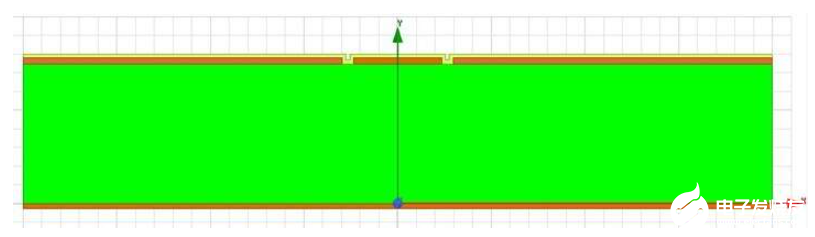

存在阻焊層,無回蝕,無L2接地平面:對于此仿真,將阻焊層添加到了模型中。Q2D仿真報告的阻抗為37.9歐姆。阻焊層的存在增加了共面走線和共面接地層之間的耦合,從而大大降低了阻抗。

存在阻焊層,無蝕刻,無L2接地層(來源:Arira Design)

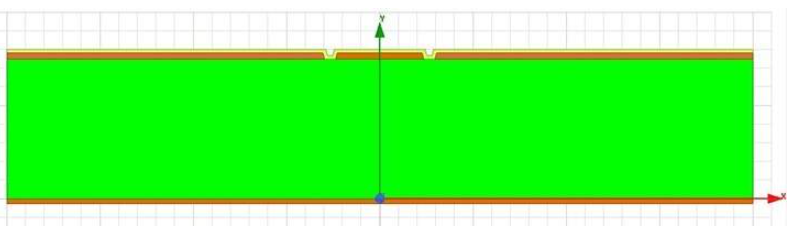

存在阻焊層,存在回蝕層,不存在L2接地平面:此模擬將回蝕添加到了共面走線和共面地上。Q2D仿真報告的阻抗為39.9歐姆。回蝕減少了共面走線和共面接地層之間的耦合,與以前的情況相比,這稍微增加了阻抗。

存在阻焊層,存在回蝕層,無L2接地平面(來源:Arira Design)

存在阻焊層,存在Etchback層,存在L2接地層:這是在原始PCB設(shè)計中實現(xiàn)的結(jié)構(gòu)。Q2D仿真報告的阻抗為36.5歐姆。靠近共面走線的接地層的存在會增加對地的耦合,從而降低阻抗。36.5歐姆的仿真結(jié)果與38歐姆的初始PCB設(shè)計上的走線阻抗測量值接近。

存在阻焊層,存在回蝕層,存在L2地平面(來源:Arira Design)

阻抗優(yōu)化

為了將GCPW結(jié)構(gòu)的阻抗優(yōu)化為50歐姆,策略是首先確定(使用模擬)滿足50歐姆要求的共面幾何形狀。然后,一旦確定了幾何形狀,就將第2層的接地平面添加到模擬中,并使用模擬對第2層接地平面切口的寬度進行優(yōu)化。

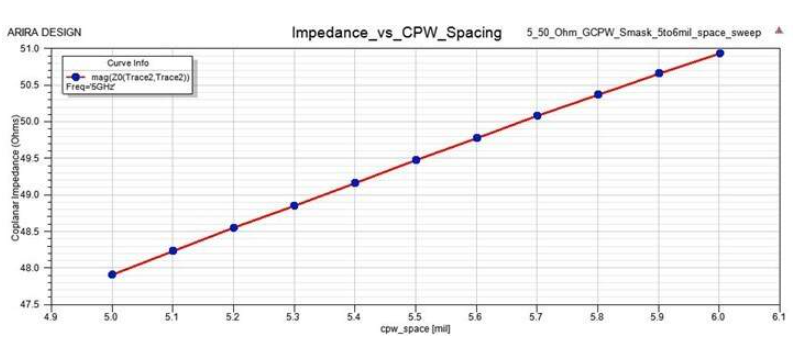

步驟1:在阻抗優(yōu)化過程的第一步中,通過連續(xù)進行共面間隙的模擬掃描,將第1層上共面間隙的寬度優(yōu)化為50歐姆。發(fā)現(xiàn)最佳間隙為5.7密耳,這導(dǎo)致模擬阻抗為50.07歐姆。通過仿真確定的最佳間隙幾乎是原始PCB設(shè)計間隙寬度的兩倍。模擬的共面阻抗與共面間隙的關(guān)系圖如下所示。

阻抗與CPW間距(來源:Arira Design)

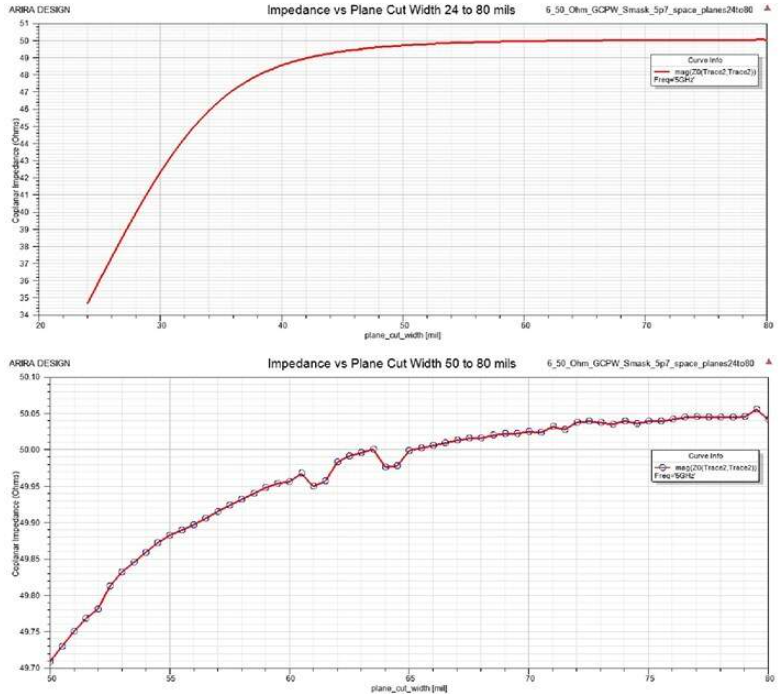

步驟2:在第二個優(yōu)化步驟中,將共面間隙固定為5.7密耳,將第2層接地平面添加到模型中,并將第2層接地平面上的切口寬度從24密耳掃到80密耳。根據(jù)以前的經(jīng)驗,我們知道與第1層總共面間隙(30 mils)相似的第2層平面切口寬度會導(dǎo)致阻抗過低,但是我們想模擬小于預(yù)期解決方案范圍的寬度,以便了解阻抗與接地寬度的關(guān)系。

阻抗與接地切口寬度的兩幅圖如下所示。第一個圖顯示了從24到80密耳掃過的接地平面切口寬度,而第二個圖則將焦點縮小到50到80密耳范圍內(nèi)的接地切口寬度。

阻抗與平面切割寬度的關(guān)系,頂部24至80密耳,底部50至80密耳(來源:Arira Design)

從這些圖中可以看出,當(dāng)不存在第2層接地層時,阻抗將收斂到在優(yōu)化過程的第一步中計算出的50.07歐姆值。從這些圖中可以看到,第二層接地平面切口寬度大于58密耳并不會顯著移動阻抗,因此,這就是為新PCB設(shè)計選擇的接地平面切口的大小。所得阻抗為49.9歐姆。

電場圖

下面顯示了不同接地平面切口寬度以及原始PCB設(shè)計的仿真電場圖。這些電場圖用于確認結(jié)構(gòu)是否正確設(shè)計并發(fā)現(xiàn)任何問題區(qū)域。例如,在以較小寬度的第2層接地平面切口為特色的仿真中,可以看到共面走線的電場與第2層接地平面牢固耦合,從而降低了走線的阻抗。

對于每種配置,將顯示兩個圖。電場強度圖顯示電介質(zhì)(FR4,阻焊層和走線上方的空氣)中的電場圖,并用顏色編碼以指示電場強度。矢量圖以矢量格式顯示電場。這也用顏色編碼以反映場強。

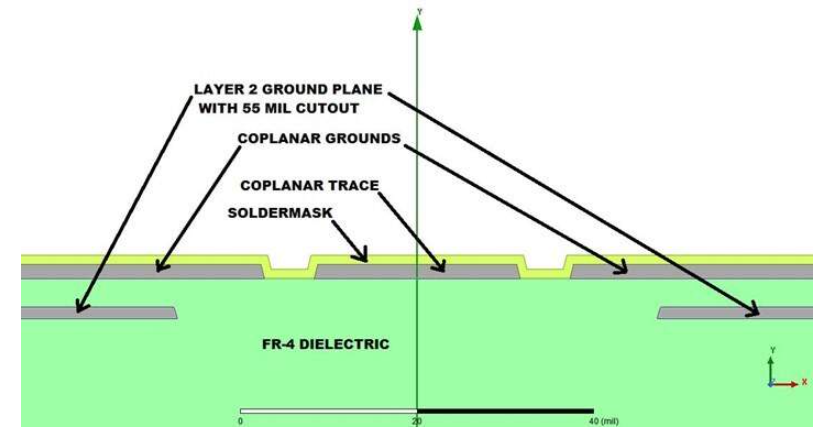

下圖顯示了在Ansoft Q2D中建模的GCPW,其中標(biāo)記了組成結(jié)構(gòu)。查看電場圖時,可使用此圖獲取方位。該圖或電場圖中未顯示第3層的返回接地平面。

以Ansoft Q2D建模的GCPW(來源:Arira Design)

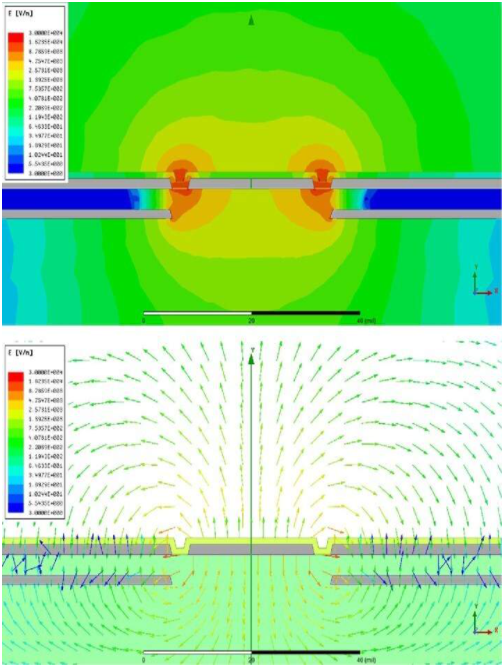

原始設(shè)計:3 mil共面間隙,30 mil 2層接地平面間隙:下圖顯示了具有3 mil共面間隙和2層接地平面中30 mil寬間隙的原始設(shè)計的電場。從共面走線到第2層接地層的耦合非常強。這種強耦合以及太小的共面間隙導(dǎo)致模擬的36.5歐姆共面阻抗。

原始設(shè)計:3 mil共面間隙,30 mil 2層地平面間隙(來源:Arira Design)

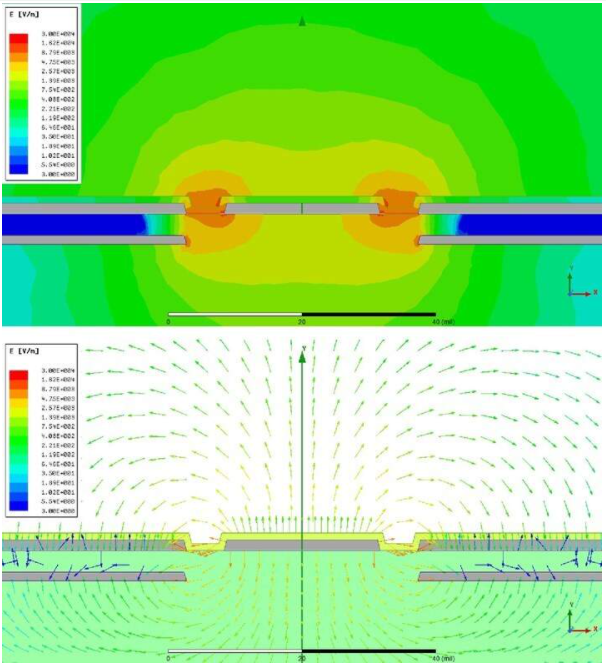

不正確的設(shè)計:5.7 mil共面間隙,35 mil第2層接地平面間隙:下圖顯示了具有阻抗優(yōu)化的5.7 mil共面間隙但在2層接地平面中有35 mil寬間隙的設(shè)計的電場。這說明了(相對常見的)情況,設(shè)計人員使用了正確的共面間隙,但錯誤地將第2層接地間隙實現(xiàn)為與總共面接地間隙相同的寬度(35密耳)。如我們所見,從共面走線到第2層接地層的耦合相當(dāng)強,這導(dǎo)致模擬的共面阻抗為46.5歐姆。

設(shè)計不正確:共面間隙為570萬密耳,第2層地平面間隙為3500萬密耳(來源:Arira Design)

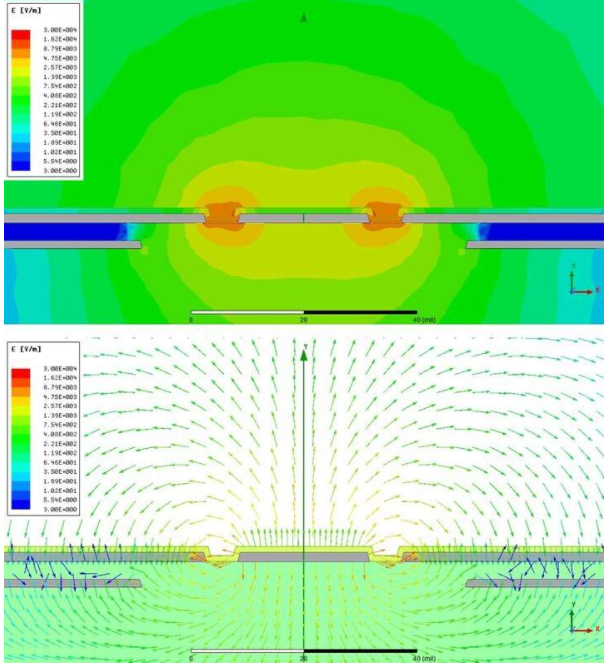

優(yōu)化設(shè)計:共面間隙為570密耳,第2層接地層間隙為58密耳:下圖顯示了設(shè)計的電場,其中第2層接地面阻抗優(yōu)化了570密耳,共面間隙為58密耳。L2接地平面間隙優(yōu)化掃描顯示,第2層接地平面中的間隙大于58 mils不會顯著影響阻抗。因此,接地平面切口設(shè)置為58密耳。

在這種配置中,與第2層接地層的耦合很小,模擬阻抗為49.9歐姆。

優(yōu)化設(shè)計:共面間隙為570萬密耳,第2層地平面間隙為5800萬密耳(來源:Arira Design)

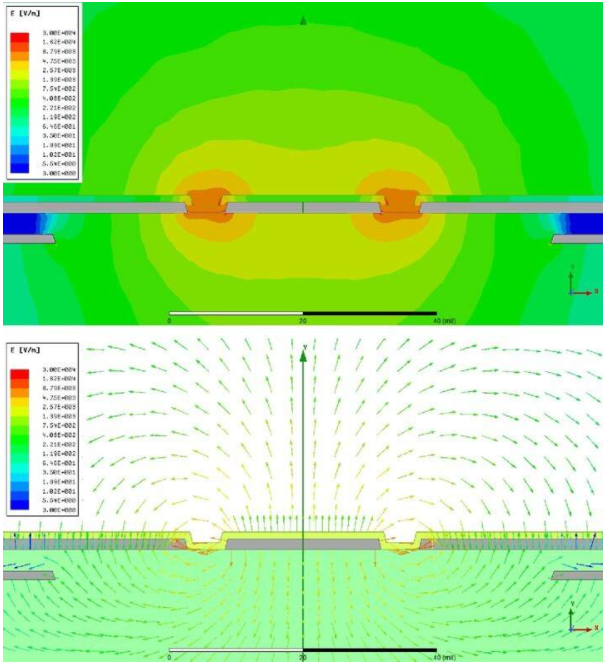

大接地平面切口:570萬共面間隙,第7層第2層接地間隙:下圖顯示了設(shè)計中的電場,其中阻抗優(yōu)化了5.7密共面間隙,第2層中有75 mil寬間隙地平面。該圖表明,如果將第2層接地平面的間隙擴大到58密耳以上,則L2接地平面的耦合不會顯著降低。但是,較大的接地平面間隙可能會干擾PCB上的其他布線。

在這種配置中,與第2層接地層的耦合非常低,模擬阻抗為50.0歐姆。

較大的接地平面切口:共面間隙為570萬,第二層接地間隙為7500萬(資料來源:Arira Design)

結(jié)論

免費軟件阻抗計算工具通常功能有限。它們可能允許也可能不允許您為回蝕或阻焊膜建模,并且它們通常不適合模擬多層幾何中各層之間的現(xiàn)場相互作用。

對于多層堆疊上的某些接地共面配置,共面接地參考平面可能是共面走線下方的兩個或更多PCB層。這需要在接地平面參考層上方的那些層上的共面走線下方設(shè)置銅保留區(qū)域。試圖直觀地估計該銅保留區(qū)域的最佳尺寸是非常困難的。低估保留區(qū)的大小可能會導(dǎo)致無法預(yù)料的EM場相互作用,而高估保留區(qū)的大小可能會導(dǎo)致PCB設(shè)計上不必要的寶貴布線面積損失。

一些設(shè)計人員使用眾多可用的傳輸線工具之一來“足夠接近”地獲取走線的阻抗,然后他們依靠自己的晶圓廠使用商用阻抗計算器(例如Polar)來計算正確的幾何形狀和撥號方式。蝕刻電路板時的阻抗。不幸的是,這種方法無法解決PCB結(jié)構(gòu)之間意外耦合的問題,因為晶圓廠在電路板制造過程中并未使用PCB上的實際走線來測量阻抗。取而代之的是,晶圓廠使用測試蝕刻片,上面刻有設(shè)計者的跡線幾何形狀。這些測試試樣不會將無意的耦合復(fù)制到PCB設(shè)計上發(fā)生的附近結(jié)構(gòu)上。因此,晶圓廠

如果您要在板上設(shè)計接地共面波導(dǎo),那么您將希望在第一時間就將其正確設(shè)置。即使天線饋線存在嚴重的失配,大多數(shù)Wi-Fi和Bluetooth設(shè)計在板載過程中似乎都可以正常工作。但是,糟糕的設(shè)計幾乎總是會在您宣布勝利后在范圍測試或數(shù)據(jù)完整性測試中廣為人知。

編輯:hfy

-

pcb

+關(guān)注

關(guān)注

4319文章

23081瀏覽量

397536 -

射頻

+關(guān)注

關(guān)注

104文章

5574瀏覽量

167695 -

連接器

+關(guān)注

關(guān)注

98文章

14483瀏覽量

136436 -

wi-fi

+關(guān)注

關(guān)注

14文章

2134瀏覽量

124428 -

計算器

+關(guān)注

關(guān)注

16文章

437瀏覽量

37330

發(fā)布評論請先 登錄

相關(guān)推薦

光波導(dǎo)系統(tǒng)中光柵幾何結(jié)構(gòu)的優(yōu)化

光波導(dǎo)系統(tǒng)中光柵幾何結(jié)構(gòu)的優(yōu)化

Jcmsuite應(yīng)用:脊形波導(dǎo)模式分析

具有連續(xù)調(diào)制光柵區(qū)域的光波導(dǎo)優(yōu)化

波導(dǎo)同軸轉(zhuǎn)接器的原理

避雷針的施工接地和行業(yè)應(yīng)用綜合方案

射頻電路工程師與模擬電路工程師 的技術(shù)要求

防雷與接地安裝原理和施工方案

RFTOP推出自研的常用連接波導(dǎo)及高效選型工具

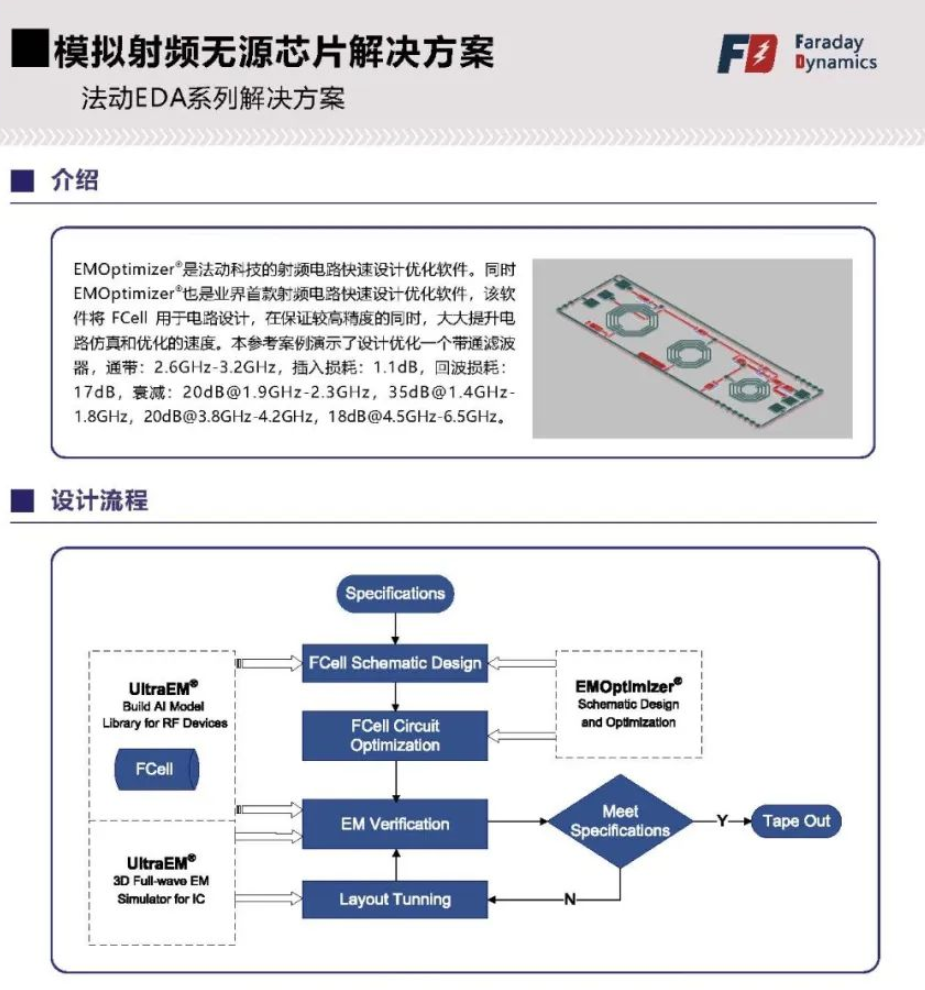

模擬射頻無源芯片解決方案

優(yōu)化PCB設(shè)計中的射頻饋線

射頻(RF)印刷電路板(PCB)設(shè)計和布局的建議

接地共面波導(dǎo)射頻饋線的優(yōu)化方案解析

接地共面波導(dǎo)射頻饋線的優(yōu)化方案解析

評論