自己動手做一個信號發生器和示波器非常重要,不僅可以深刻理解測量儀器的工作原理、關鍵技術指標,還可以將書本上學過的模擬電路、數字邏輯乃至嵌入式系統全部串起來,從系統層面對各個部分的功能以及構成有更真切的認識,因此這兩個項目應該是所有電子工程師都要動手做一遍的基礎入門項目。

高速ADC是數字示波器的核心部件,今天關于ADC應用的文章就結合我們摩爾吧/硬禾實戰營的一個實際項目 - 100Msps的數字示波器的制作來做一個簡單的案例分析,數字和處理部分將在將來的文章中具體分析,今天集中在模擬部分:

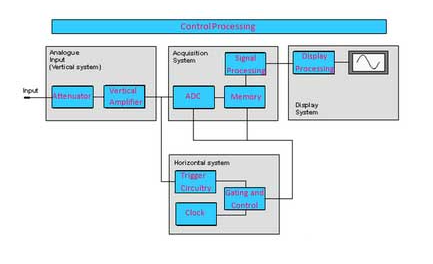

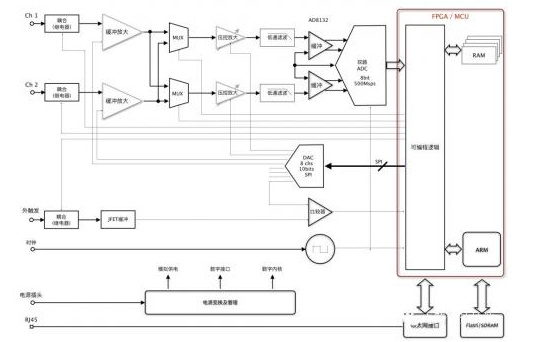

數字示波器的構成框圖

我們的項目對模擬部分的主要指標要求如下:

? 單通道、100Msps采樣率

? 模擬帶寬20MHz,輸入電壓的范圍 - -10V ~ +10V

? 最小分辨電壓 10mV

經過高速ADC以后的數據通過FPGA(當時就用Lattice的FPGA)進行處理以后送到后面的Cortex M4控制器,再在LCD顯示屏上顯示出來,觸發、測量電壓、頻率等參數都在FPGA內實現。

用Lattice FPGA + NXP的M4開發板以及自制的模擬鏈路/ADC構建的數字示波器

今天我們就以這個項目為例,簡單分析一下數字示波器模擬鏈路部分的設計要點。

首先我們基于給出的指標需求分析一下:

? 單通道 - 需要一顆單路的ADC

? 100Msps - 需要一顆采樣率在100Msps以上的ADC

? 20MHz的模擬帶寬 - 意味著最高頻率20MHz的模擬信號,如果用100Msps的采樣率,每個周期會有5個采樣點,留給學員通過FPGA邏輯進行內插的空間

? +/-10V的最大輸入電壓范圍和最小10mV的電壓分辨率意味著整個模擬鏈路以及ADC能夠處理的信號的動態范圍為20Vpp/10mV ~ 2000 ~ 63dB

第一個問題:選用多少位數的ADC?8、10、12、14、16位?ADC的精度的選用要和前面的模擬信號調理電路共同對付63dB的動態范圍。理想狀態下8位的ADC可以提供48dB的動態范圍、10bit ~ 60dB、12bits ~ 72dB,14bits ~ 84dB,但由于存在著量化噪聲,導致ADC的有效位數要低于實際使用的位數,也就是12位的ADC,有效的位數小于12(數據手冊顯示 - AD9628在采集20MHz的模擬信號的時候相當于11.6bits)。 從這個分析上看,選用一顆12bits/100Msps的ADC就可以滿足系統對動態范圍的要求。

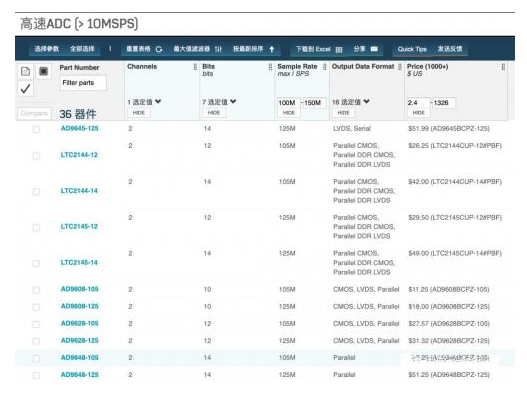

但,ADC的精度越高,意味著器件內部的資源大幅增加,器件的成本以及價格也就大幅增加,在同樣的轉換率的情況下,一顆12位的雙通道ADC(AD9628-105)的價格比10位的雙通道ADC(AD9608-105)要高出一倍(以其官網上1000+片的價格做參考),見下面的表格。這多花的十幾美元是否可以通過10bit ADC + 可變增益運放甚至8bit ADC +可變增益運放來實現呢?

ADI公司的高速ADC,可以通過參數過濾選用最適合自己的器件

這就需要權衡,需要從系統層面來綜合考慮,引入可變增益放大器可以提供幾十個dB的可調增益范圍,帶來的挑戰就是:

? 運放器件本身的價錢、多出來的電路板空間的成本

? 運放電路設計(需要仿真)和調試的難度 - 可調增益、要保證線性范圍工作、周邊器件的合理選用

? 最難的可能是運放電路的供電 - 一般都是雙軌、低噪聲的電壓,比如+/-5v或+/-10V,模擬電路的雙軌供電可是難煞了很多工程師,做不好性能會達不到要求。

? 放大電路的增益要可調節,如何調節?總不能用手擰電位計調節吧?需要VGA(電壓控制增益)或模擬開關切換。電可調的電路會帶來額外的復雜度以及成本。

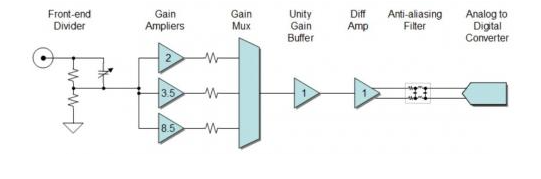

實現數字示波器模擬前端的方式之一,通過模擬開關來實現鏈路增益的調節

說到這里是不是覺得頭大了?是不是覺得自己的知識量不夠了?這還僅僅是信號的幅度方面的要求,信號的頻率呢,也就是對頻帶的要求呢?即便20MHz以內的模擬信號,你需要低通濾波器(防混疊),選用的模擬器件要考慮到增益帶寬積是否滿足要求、瞬間的響應速度是不是夠、電壓控制增益的范圍內線性度如何?

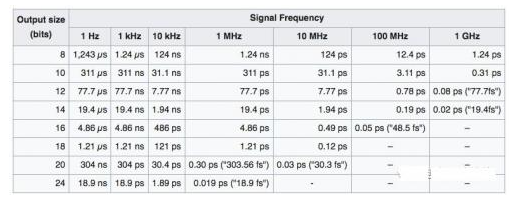

從降低系統復雜度的角度出發,我們希望用一顆高速的ADC,比如14、16bit全部搞定最好,但殺雞用牛刀顯然也是不對的,畢竟要考慮到系統的成本,更重要的是即便從理論分析上14bit的ADC能夠滿足你的要求,但實際的電路中會由于電源噪聲、時鐘抖動等使得你使用更高分辨率的ADC沒有意義。上篇文章中我們講過(下面的表格),即便對于10MHz的模擬信號,用14bit的ADC,采樣時鐘邊沿的抖動必須小于2ps,100MHz(10ns周期)的時鐘抖動要小于2ps,你自己測一下你自己板子上用FPGA產生的100MHz的時鐘的邊沿抖動有多大?是否能小于2ps?

針對不同的模擬信號,采用不同位數的ADC對時鐘邊沿抖動的要求

所以,如果你用14bits的ADC,那必須給你的ADC提供極小邊沿抖動的采樣時鐘信號,意味著你的時鐘源(一般PLL產生)要非常好,最好采用差分時鐘信號傳輸、時鐘以及ADC的電源去偶要格外注意、PCB的設計要很講究。所以挑戰會比較大。

越是采樣頻率高的示波器,高分辨率的ADC器件成本會更高,對時鐘抖動的要求越高,成本也會大幅增加,比如500Msps的數字示波器,如果你做的產品不能賣到非常高的價格讓你有足夠的成本空間采用更好的器件,最好采用8bits的ADC。

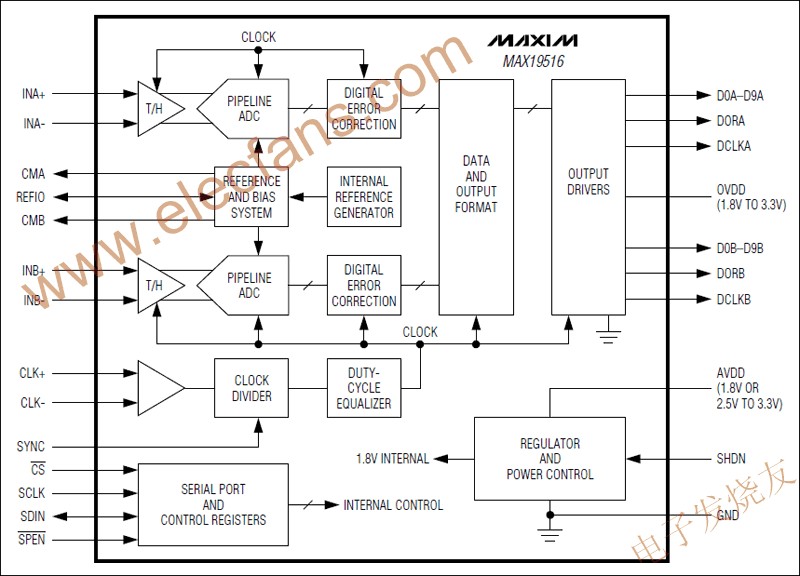

因此在學員的實際項目制作中我們也盡量讓學員選用8bit、10bit的ADC配合前端可調增益的放大器來實現63dB的動態范圍,下面是幾款當時我們推薦給學員選用的ADC的型號,具體型號的選用還要考慮到供電電壓、功耗、數據接口方式、價格等要素。

幾款可用于100Msps數字示波器的高速ADC

在我們100Msps的項目中我們選用8位的AD9283作為ADC,63dB-48dB ~ 15dB的動態范圍就通過可控增益的運放來實現。

由于輸入的信號是+/-10V,而ADC一般的輸入電壓范圍是2Vpp,所以需要對輸入的電壓信號先進行10:1衰減(-20dB),得到+/-1V的模擬信號,再通過0-20dB的可變增益控制來滿足ADC的輸入電平要求。

在ADC之前有一個低通濾波器用于對20MHz以上的信號做過濾,主要目的是防止20MHz以上的噪聲通過采樣混疊在被測信號的采樣結果中。關于這部分的理論分析大家可以看一下抗混疊采樣相關的技術文章。

以上我們簡單分析了一下如何根據被采集信號的幅度范圍來選取適當分辨率的ADC + 可變增益調理電路的組合,原則是考慮到電路的性能、可實現性、設計難度、系統成本等各因素后的綜合折衷。

下面的這個圖是我們設計的一款產品 - 500Msps的雙通道高速數據采集系統的框圖,使用的是8位、500Msps的ADC以及ZYNQ FPGA器件,可以通過以太網同上位機PC進行數據傳輸。壓控放大器的增益控制電壓是靠低速串行 DAC 實現。每一級電路的增益、帶寬的設定原理同上。

編輯:hfy

-

FPGA

+關注

關注

1629文章

21729瀏覽量

603009 -

數字示波器

+關注

關注

6文章

522瀏覽量

33565 -

信號發生器

+關注

關注

28文章

1472瀏覽量

108739 -

測量儀器

+關注

關注

3文章

792瀏覽量

42163

發布評論請先 登錄

相關推薦

ADC芯片的采樣率為100MSPS,位寬16位,那么吞吐量是多少?

[原創]8bit100MHZ AD轉換國產芯片-HWD9288

【FPGA設計實例】基于FPGA的數字示波器設計

MAX19506 雙通道、8位、100Msps ADC

面向醫療與工業,TI推出8通道100MSPS ADC

100Msps的數字示波器的制作來做一個簡單的案例分析

關于MSO/DS4000數字示波器的性能分析和介紹

非常低功耗的 12 位 / 14 位 25Msps 至 125Msps ADC 在 125Msps 時以低于 100mW 工作

AD7760:24位、2.5 MSPS、100 dB,Σ-Δ ADC,內置片內緩沖 數據手冊

10位100msps流水線adc的分析實現

ADS5263四通道、16位、100MSPS高SNR ADC數據表

ADS5295低功耗,12位,100MSPS,8通道模數轉換器(ADC)數據表

關于ADC應用100Msps的數字示波器的案例分析

關于ADC應用100Msps的數字示波器的案例分析

評論