對于DDR3的布局我們首先需要確認(rèn)芯片是否支持FLY-BY走線拓?fù)浣Y(jié)構(gòu),來確定我們是使用T拓?fù)浣Y(jié)構(gòu)還是FLY-BY拓?fù)浣Y(jié)構(gòu)。。

常規(guī)我們DDR3的布局滿足以下基本設(shè)計要求即可:

1.考慮BGA可維修性:BGA周邊器件5MM禁布,最小3MM。

2.DFM 可靠性:按照相關(guān)的工藝要求,布局時器件與器件間滿足DFM的間距要求;且考慮元件擺放的美觀性。

3.絕對等長是否滿足要求,相對長度是否容易實現(xiàn):布局時需要確認(rèn)長度限制,及時序要求,留有足夠的繞等長空間。

4.濾波電容、上拉電阻的位置等:濾波電容靠近各個PIN放置,儲能電容均勻放置在芯片周邊(在電源平面路徑上);上拉電阻按要求放置(布線長度小于500mil)。

注意:如有提供DEMO板或是芯片手冊,請按照DEMO板或是芯片手冊的要求來做。

1.濾波電容的布局要求

電源設(shè)計是PCB設(shè)計的核心部分,電源是否穩(wěn)定,紋波是否達(dá)到要求,都關(guān)系到CPU系統(tǒng)是否能正常工作。濾波電容的布局是電源的重要部分,遵循以下原則:

CPU端和DDR3顆粒端,每個引腳對應(yīng)一個濾波電容,濾波電容盡可能靠近引腳放置。

線短而粗,回路盡量短;CPU和顆粒周邊均勻擺放一些儲能電容,DDR3顆粒每片至少有一個儲能電容。

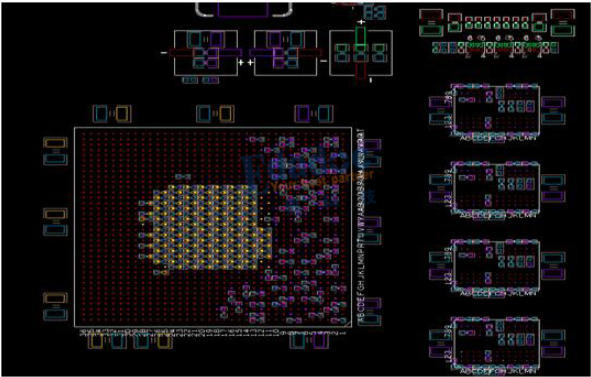

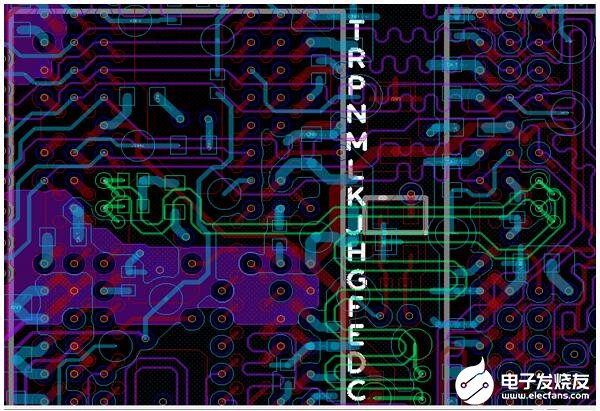

圖1:VDD電容的布局(DDR顆粒單面放)

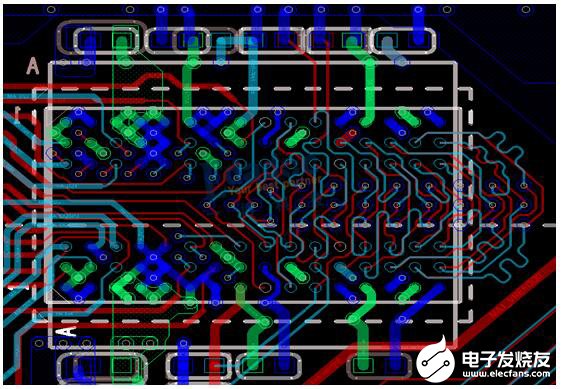

如圖2所示:VDD電容的布局(DDR顆粒正反貼)

DDR 正反貼的情況,電容離BGA 1MM,就近打孔;如可以跟PIN就近連接就連接在一起。

2.VREF電路布局

在DDR3中,VREF分成兩部分:

一個是為命令與地址信號服務(wù)的VREFCA;另一個是為數(shù)據(jù)總線服務(wù)的VREFDQ。

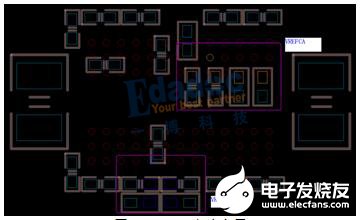

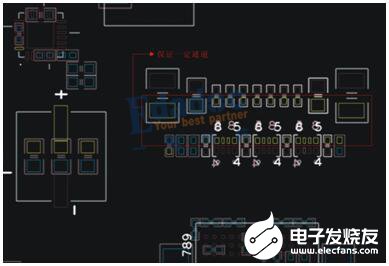

在布局時,VREFCA、VREFDQ的濾波電容及分壓電阻要分別靠近芯片的電源引腳,如圖3所示。

圖3:VREF電路布局

3.匹配電阻的布局

為了提高信號質(zhì)量,地址、控制信號一般要求在源端或終端增加匹配電阻;數(shù)據(jù)可以通過調(diào)節(jié)ODT 來實現(xiàn),所以一般建議不用加電阻。

布局時要注意電阻的擺放,到電阻端的走線長度對信號質(zhì)量有影響。

布局原則如下:

對于源端匹配電阻靠近CPU(驅(qū)動)放,而對于并聯(lián)端接則靠近負(fù)載端(FLy-BY靠近最后一個DDR3顆粒的位置放置而T拓?fù)浣Y(jié)構(gòu)是靠近最大T點放置)

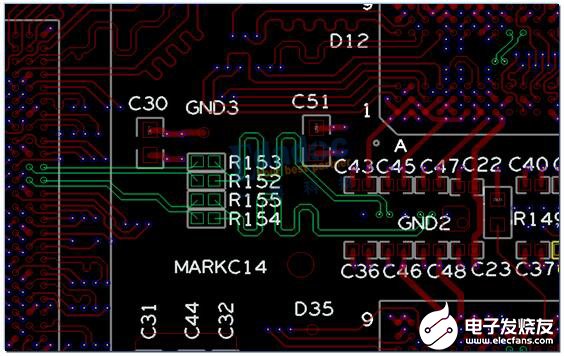

下圖是源端匹配電阻布局示意圖;

圖4:源端匹配電阻

圖4:并聯(lián)端接

而對于終端VTT上拉電阻要放置在相應(yīng)網(wǎng)絡(luò)的末端,即靠近最后一個DDR3顆粒的位置放置(T拓?fù)浣Y(jié)構(gòu)是靠近最大T點放置);注意VTT上拉電阻到DDR3顆粒的走線越短越好;走線長度小于500mil;每個VTT上拉電阻對應(yīng)放置一個VTT的濾波電容(最多兩個電阻共用一個電容);VTT電源一般直接在元件面同層鋪銅來完成連接,所以放置濾波電容時需要兼顧兩方面,一方面要保證有一定的電源通道,另一方面濾波電容不能離上拉電阻太遠(yuǎn),以免影響濾波效果。

圖5:VTT濾波電容

DDR3的布局基本沒有什么難點,只是要注意諸多細(xì)節(jié)之處,相信大家都已經(jīng)學(xué)會。

編輯:hfy

-

上拉電阻

+關(guān)注

關(guān)注

5文章

359瀏覽量

30609 -

DDR3

+關(guān)注

關(guān)注

2文章

276瀏覽量

42244 -

濾波電容

+關(guān)注

關(guān)注

8文章

458瀏覽量

40021 -

cpu

+關(guān)注

關(guān)注

68文章

10854瀏覽量

211587

發(fā)布評論請先 登錄

相關(guān)推薦

使用 AM437x 而不具有 VTT 終端的 DDR3 參考設(shè)計

使用AM437x無VTT終端的DDR3參考設(shè)計包括BOM及原理圖

請問面對4片ddr3怎么布局?

DDR布局的要求有哪些?

Gowin DDR3參考設(shè)計

ddr4和ddr3內(nèi)存的區(qū)別,可以通用嗎

基于Digilent介紹DDR3和mig

常規(guī)DDR3的布局需要滿足哪些要求?

常規(guī)DDR3的布局需要滿足哪些要求?

評論