Vref偏移對DDR會造成什么影響,其中有比較重要的一個點就是會影響setuptime和holdtime,這兩個參數和Vref又有什么關系呢,還有JEDEC中講的derating又是什么東西呢?

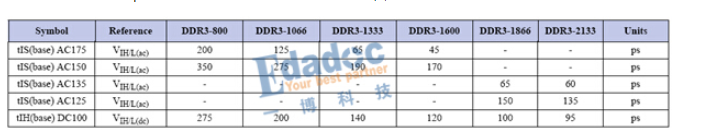

setuptime和holdtime對我們判斷時序裕量是一個比較關鍵的數值。一般JEDEC里面會對于setuptime和holdtime做比較詳細的描述,如下圖所示,

從上圖中,我們可以看到幾個比較關鍵的點,為什么是tIS(base)和tIH(base),還有標題中指明for 1V/ns,又指代的什么意思?為什么tIS參考的是VIH/L(ac),而tIH參考的是VIH/L(dc)呢,AC和DC的區別又是什么?一個小小的參數表格,包含的意義卻涉及很多內容。

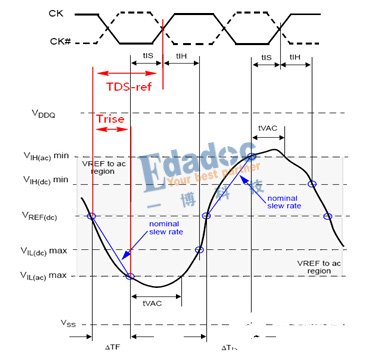

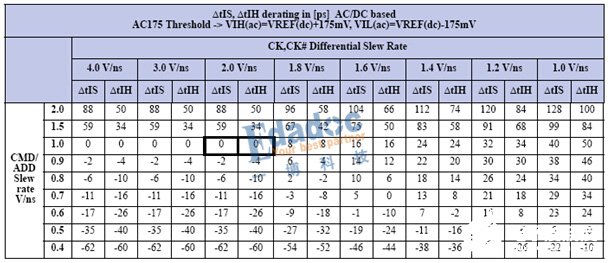

首先,我們計算建立時間的margin的時候,都是由UI/2-建立時間,實際上此時的建立時間是tIS(total setup time)= tIS(base)+derating, derating是對建立保持時間基準值的修正。對于tIS的定義,為什么會需要用到derating這個參數呢,這實際和規范中tIS(base)的定義方式相關。如下圖所示,建立時間等于TDS-ref(在ref處的建立時間)減去Trise(Vref到VIH AC的時間)。規范中的基準值是預減去了這個Trise的,這個預減去的值是特定slew rate為1V/ns時的值,若判斷門限是AC175,則預減去175ps。當slew rate等于1V/ns時,derating為0,不需要調整;當slew rate大于1V/ns(更快)時,從Vref到Vih(ac)所需的時間就少,預減多了,要補回來,所以取值為正;當slew rate小于1V/ns(更慢)時就預減少了,所以取值為負。

至于建立時間和保持時間的參考電壓值不一致,主要是因為AC和DC的代表的意義不一樣,AC指由高低電平跳變時需要的參考電壓,DC則指保持所在電平時的閾值電壓, tIS是以數據從前一狀態變化為當前狀態的時刻開始算起,對應于狀態變化過程,要確保電平已變化到規定電平,所以以更為嚴格的AC參數作為參考;tIH描述的是數據從穩定到狀態轉換的時間,對應于電平穩定的過程,而電平一旦建立后,發生狀態轉換的門限電壓值是參考DC,所以tIH也以DC參數作為參考。

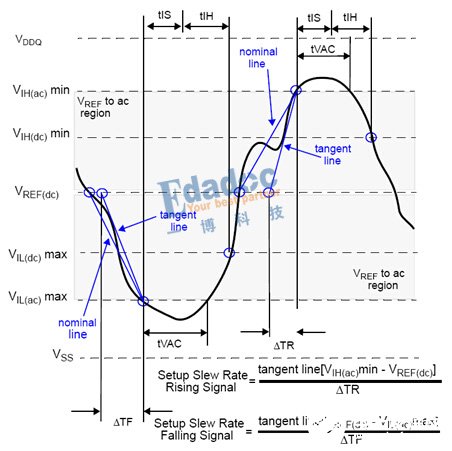

信號的波形很多情況都是不完美的,也許有回溝,也許會有臺階,如下圖所示,這種情況下,skew rate就不能用下圖所示的nominal line,而應該選取tangent line。

編輯:hfy

-

DDR

+關注

關注

11文章

732瀏覽量

66886 -

波形

+關注

關注

3文章

390瀏覽量

32369 -

JEDEC

+關注

關注

1文章

37瀏覽量

17728 -

IVREF

+關注

關注

0文章

6瀏覽量

1522

發布評論請先 登錄

INA849仿真輸出電平不在VREF的靜默電平,有近1V的偏移,是什么原因引起的?

DDR2設計原理 DDR2 design

無法設置屬性VREF

怎么將FPGA vref引腳連接到DDR參考電壓

OMAPL138 DDR2讀數據偏移2個字節

金士頓:DDR2/DDR3價格可能會繼續上漲

DDR4偽漏極開路驅動器及對接收器的功耗和Vref電平而言的意義

75uV輸入偏移電壓會影響您的電路嗎?

內置VREF的灌電流/拉電流抗輻射加固型3A DDR終端穩壓器TPS7H3301-SP數據表

內置VREF的灌電流/拉電流抗輻射加固型3A DDR終端穩壓器TPS7H3301-SP數據表

評論