我們都知道源同步方式的典型代表是DDRx信號,下面就來介紹源同步方式是怎樣改善系統(tǒng)同步的先天不足的。

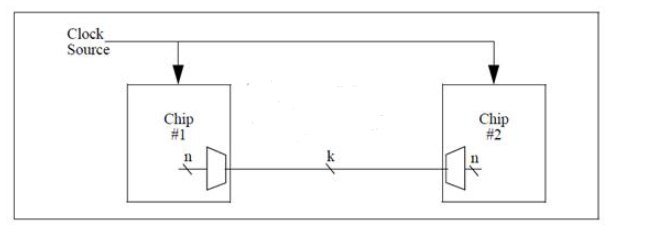

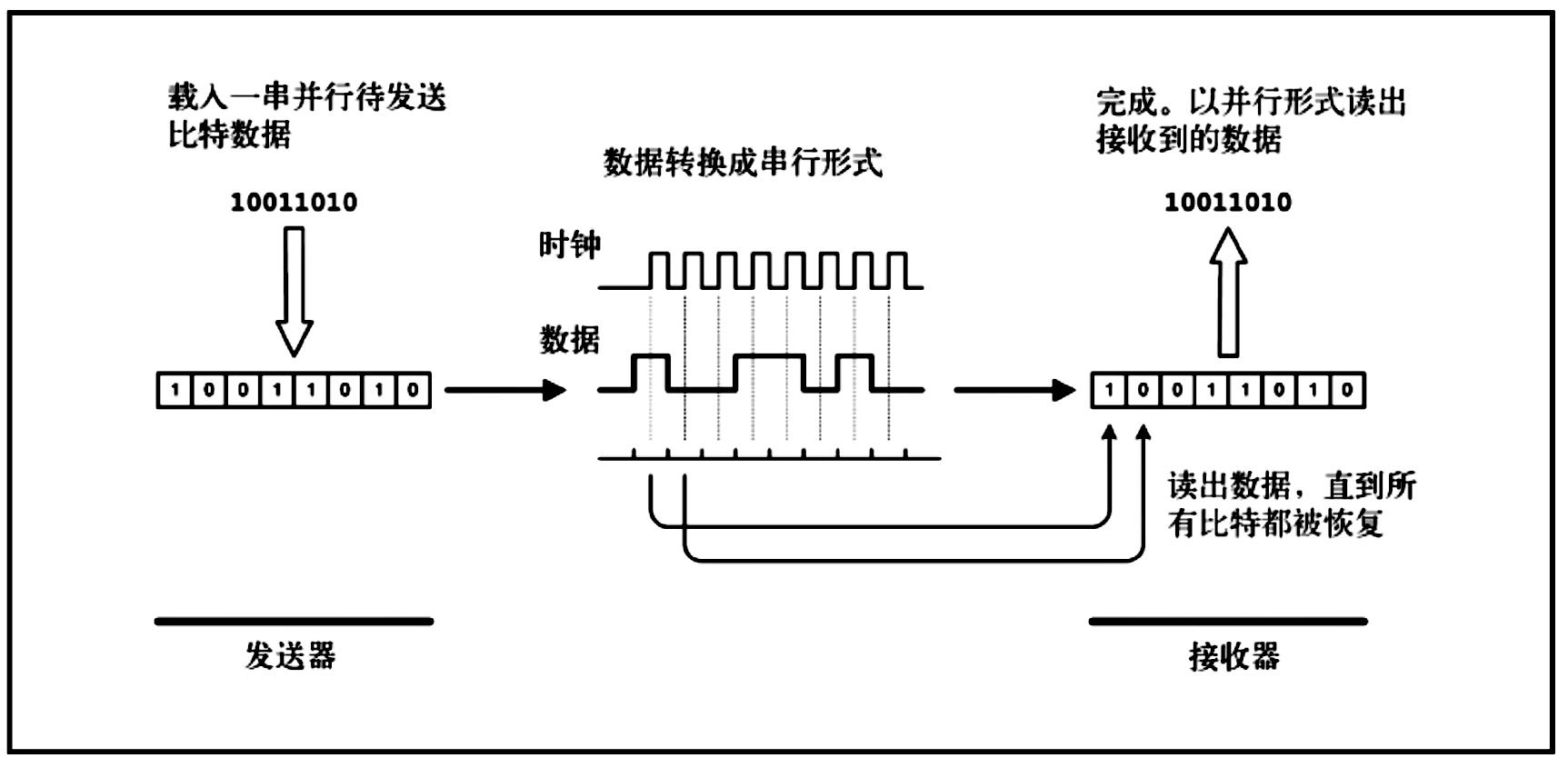

源同步要解決的第一個問題是減少在芯片之間傳輸數據所需的I/O引腳數量。這通過將芯片#1的輸出處的n位數據復用到k位互連(k 《n),然后將芯片#2的輸入上的互連的k位解復用到n位內部數據路徑上來實現(xiàn),如下圖所示。所得到的系統(tǒng)只需要每個芯片上的k個I/O引腳,而不需要先前的n個引腳。

當然,雖然引腳數量要求已經通過k:n的比率降低,但是參考時鐘的所需頻率已經增加了這個比率的倒數。由于噪聲,電磁干擾(EMI)和功耗問題,系統(tǒng)設計人員通常不喜歡在系統(tǒng)內分配高速參考時鐘。通常,分配較低頻率的時鐘,并且使用芯片中的PLL將該參考時鐘乘以可用頻率,但所產生的時鐘相位的變化以及數據傳輸的頻率越高,往往會加劇并行數據總線的時序問題。

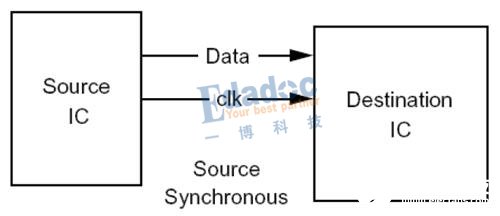

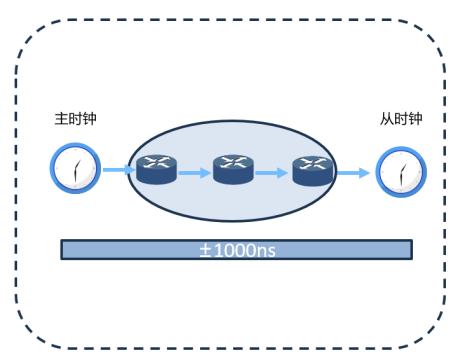

源同步的第二個法寶就是在兩個芯片之間的數據通路中增加了一個高速時鐘,如下圖所示。假設該時鐘源提供的時鐘頻率略低于在芯片互連上對數據進行觸發(fā)的時鐘頻率,每個芯片都使用PLL來產生這個頻率倍數的時鐘,所得到的時鐘用于啟動和捕獲相應芯片中的數據。芯片#1中用于從該芯片啟動數據的PLL的輸出時鐘也是該芯片的輸出,芯片#2使用該時鐘來捕獲數據,這種方法稱為時鐘轉發(fā)。

時鐘轉發(fā)的優(yōu)點是用于在芯片#1上啟動數據的高速時鐘可用于芯片#2作為捕獲數據的參考。這樣之前通過時鐘分配網絡驅動兩個芯片的延遲的變化在時序分析中就不需要考慮了,只有時鐘路徑和數據位之間的延遲變化是相關的。 雖然制程,電壓和溫度導致的這些路徑之間的變化在一定程度上相互影響,但接口的時序分析需要的余量較少,因此建立和保持時間更容易滿足。

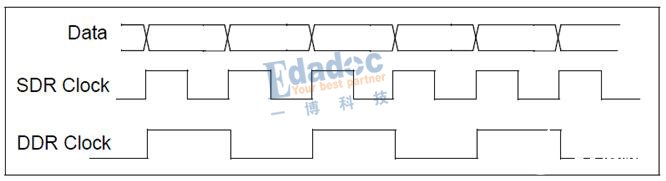

我們還是來看看典型的例子吧,圖中所示的時鐘可以是單數據速率(SDR)或雙倍數據速率(DDR)的時鐘,如下圖所示。SDR就是接收芯片在SDR時鐘的每個上升沿(或每個下降沿)捕獲數據; 而DDR則是接收芯片捕獲DDR時鐘的每個邊沿(上升沿和下降沿)的數據。

無論時鐘是SDR還是DDR時鐘,接收芯片都使用該時鐘直接捕獲數據。 該芯片還使用參考時鐘以相同的頻率生成內部系統(tǒng)時鐘,這些時鐘是中間同步的。 雖然頻率相同(鑒于它們共享共同的頻率參考),但是時鐘之間的相位關系是未知的,并且可能由于PVT變化而變化。 因此,接收芯片通常將接收到的數據從接口時鐘域重新定時到內部芯片時鐘的時鐘域。 FIFO用于執(zhí)行此重定時功能, 期望最小化由接口時鐘計時的觸發(fā)器的數量,以便最小化時鐘分配網絡中的延遲,否則時鐘問題將會加劇。

編輯:hfy

-

時鐘

+關注

關注

11文章

1903瀏覽量

133290 -

電磁干擾

+關注

關注

36文章

2393瀏覽量

106659 -

接收芯片

+關注

關注

1文章

28瀏覽量

17350

發(fā)布評論請先 登錄

一種delphi串行通信源碼教程

一種并行幀同步設計方案的提出、設計與應用

信源及信源熵

一文詳解串行、并行、同步、異步

評論