精密制造交接

另一個常見的挑戰是在制造之前進行驗證簽核所需的時間。避免這種瓶頸及其相關影響的一種行之有效的方法是實施一種集成且連續的驗證過程和方法,以使最終的驗證簽字過程得到控制和管理。這意味著提供通過鑄造廠或OSAT的加工規則(PDK或PADK)的無制造錯誤的制造和裝配數據。目標和挑戰是在第一階段中實現這一目標。

消除迭代需要設計環境具有滿足流程規則的能力和特征,而又不依賴于可能會需要多次設計旋轉才能達到切換標準的命中或未命中的手動方法。為了避免多次修改設計以通過制造商的規則,自動化是強制性的。

先進的IC封裝幾乎總是使用GDSII制造的。制造商,鑄造廠或OSAT將通過此GDSII文件來驗證是否符合其制造規則和約束,這當然會導致一個常見的難題:GDSII文件是從設計工具的本地CAD數據庫進行后處理的,這就是問題可能發生并且確實發生的地方。

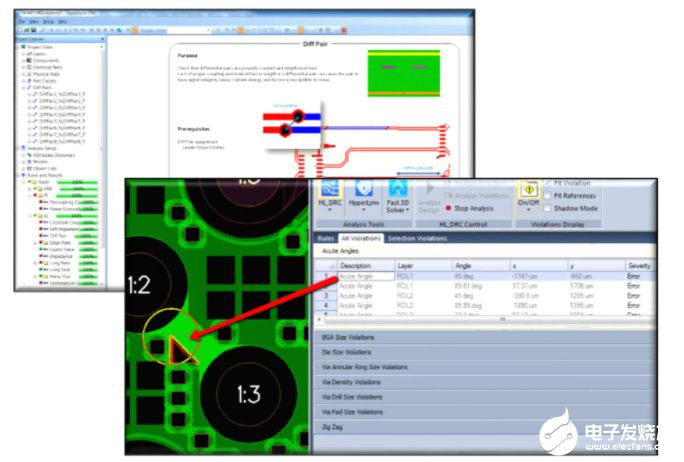

圖5如果要避免重新旋轉,精確創建制造定義的結構至關重要。資料來源:Mentor Graphics

無論您的CAD設計工具能生產出滿足制造商制造規則的幾何形狀的好壞,都是將后處理衍生的GDSII用于簽收,這就是當今大多數IC封裝CAD設計工具的致命弱點。盡管CAD中的實際設計可以通過,但由于幾何圖形后處理質量差,因此生成的GDSII很少這樣做,這通常導致設計旋轉,因為設計人員難以獲得可接受的GDSII。

金色簽到

對于高級IC封裝,黃金簽收需要進行全面的檢查,否則組裝后的器件總產量將無法達到目標,并且會超出預計的組裝和測試成本。全面的金色簽字至少應包括物理驗證,連接性檢查(aka LVS)和異構程序集級別的驗證(aka LVL)。這種全面的簽核檢查過程可以突出顯示許多需要重做的問題。如果沒有發現,這些問題很容易導致項目延誤,增加成本并導致錯過制造計劃。

防止這種情況發生的一種方法是實施“左移”設計流程,該流程在設計中執行,以查找并消除明顯的簽核錯誤。使用這種方法可以消除80%以上的簽核錯誤,并防止簽核瓶頸和延遲。

IC驗證的一個標志就是在一個框架內使用多個專用的EDA工具,以使設計人員能夠執行各種驗證過程。自動執行異構包裝組裝驗證時的目標是相同的。基于已經根據目標晶圓代工廠規則對每個模具進行檢查的前提,顯著簡化了異構驗證。保持設計和驗證環境之間的獨立性以確保驗證結果的準確性也很重要。

驗證包括DRC,以驗證管芯組件之間的相互作用,并且可能需要在每個管芯內提取多個層以查看這些相互作用。物理驗證還包括LVL檢查,以檢查基板之間的對齊,縮放或補償系數以及焊盤中心或重疊。對于EDA工具,工程師必須了解如何區分每個芯片和每個位置的分層。此外,該工具應利用數字孿生虛擬模型的數據來自動提取正確的裝配體表示,以執行DRC和LVL檢查。

IC中的連通性檢查(LVS)會查看從物理布局數據得出的連接形狀和引腳位置,以生成物理網表,并將其與黃金原理圖網表進行比較以驗證連通性。在每個基板級別和跨基板執行連接檢查。以最簡單的形式實現的自動化封裝LVS流程必須確保中介板和封裝GDSII正確地按預期將管芯連接到管芯(對于多管芯系統),并且將管芯連接到C4 / BGA凸點(對于單管芯和多管芯系統)由設計師。

如前所述,系統網表是從整個組件的數字孿生編譯而成的。然后將該系統或黃金網表與從制造數據得出的物理設計連接性進行比較。虛擬模型可以突出顯示警告或違規,因此設計人員可以在EDA工具的幫助下跟蹤和調試錯誤。

圖6基于幾何的集成DRC可以防止過多的簽核錯誤。資料來源:Mentor Graphics

2.5和3D異構封裝通常包含多個設備和多個基板,以提供系統縮放和性能所需的解決方案。隨著管芯和基板之間的輪廓線的減少,這些元件的緊密接近極大地增強了芯片-封裝之間的相互作用,因此需要統一的協同設計流程。使用諸如高速接口或功率傳輸之類的關鍵元件,對一個基板的決策可能會對相鄰基板產生連鎖反應,或影響整個系統。

設計人員必須使用快速原型設計和協同設計來評估襯底的可布線性,電氣和熱性能以及測試,從而找到在單一環境中管理多個襯底的方法,同時跨地區和部門進行協作。隨著方法和流程的成熟,系統級設計人員還需要了解封裝DRC,LVL驗證和組裝級LVS是否足以保證正確的功能和成功制造異構組裝的能力。

通過以高效,可重復和自動化的流程管理所有這些流程的單一環境,設計人員可以更好地預測和消除潛在的下游問題,有效地執行和評估折衷和設計方案,并清晰地將決策傳達給利益相關者。

最后,在堆疊為2D和3D異構組件之前,已知的良好管芯(KGD)測試和封裝級測試的生成至關重要。測試團隊應重用芯片級的內置自測試(BIST),并通過將其映射到封裝級別來掃描模式。封裝互連結構的邊界掃描測試可確保I / O實際上已連接,并且可以識別任何基板制造或組裝問題。

完整的設計和驗證流程

對于許多應用而言,下一代IC封裝是在縮小整體封裝尺寸的同時實現硅縮放,功能密度和異構集成的最佳途徑。將多個設備集成到一個封裝中可支持系統擴展需求,減少系統空間,降低制造成本,并通常提高質量和可靠性。

下一代IC封裝設計需要一種新的方法來進行所有級別的設計和驗證,即使使用數字孿生虛擬原型模型也可以驅動設計和驗證的各個方面,即使使用了不同的設計工具也可以使設計人員進行管理。所有這些過程都以高效,可重復和自動化的流程進行。

西門子業務部門Mentor提供了一種高密度高級封裝解決方案,該解決方案專為解決下一代IC封裝設計的五個關鍵問題而開發。完整的設計和驗證流程整合了行業的黃金標準進行驗證。口徑3DSTACK以及Xpedition基板集成商和Xpedition封裝設計器,利用HyperLynx和FloTHERM進行跨域多物理場分析。

Keith Felton是Mentor Graphics的Xpedition IC封裝解決方案的市場經理。

編輯:hfy

-

晶圓

+關注

關注

52文章

4895瀏覽量

127939 -

eda

+關注

關注

71文章

2755瀏覽量

173216 -

CAD

+關注

關注

17文章

1090瀏覽量

72452 -

IC封裝

+關注

關注

4文章

185瀏覽量

26718

發布評論請先 登錄

相關推薦

探索步進電機驅動IC的創新融合

開始報名!PCB/封裝設計及系統 SI/PI/Thermal 仿真專場研討會——2024 Cadence 中國技術巡回研討會

普萊信喬遷新址,聚焦先進封裝設備國產化

什么是IC封裝?

2024年全球先進封裝設備將同比增長6%至31億美元

半導體組裝封裝設備市場遇冷

224G 系統需要多大的 ASIC 封裝尺寸?

探索高級IC封裝設計的相互關聯(下)

探索高級IC封裝設計的相互關聯(下)

評論