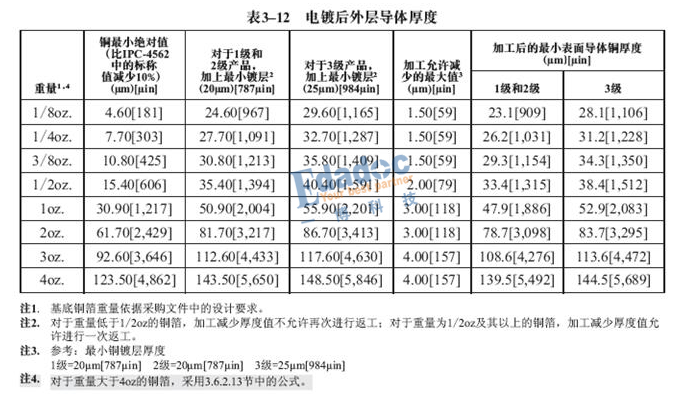

我引用了IPC對銅箔厚度偏差的定義,我們來回顧一下:

提取內層0.5oz的數據來簡單做個描述:這也是多層板層疊中的常見內層厚度

內層0.5oz的銅箔正常厚度是0.7mil(17um),也是見到有人用這個厚度來做仿真和設計的。也有的公司會選擇0.5oz的銅厚是0.6mil(15.4um),這是IPC允許的銅的最小值。但是還有一個加工中允許減少的銅厚是4um,加工后允許的銅箔極限最小厚度是0.45mil(11.4um)。

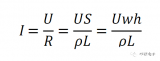

我們都知道,銅厚變化,首先會影響阻抗,然后會影響載流能力、壓降、電流密度等指標,那我們來看看影響到底有多大?

內層銅厚偏差對性能的影響

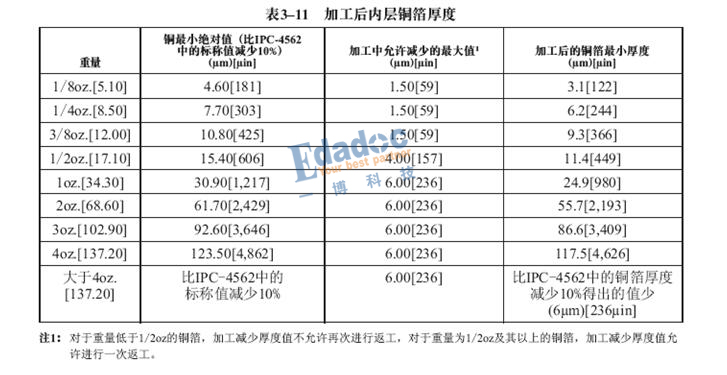

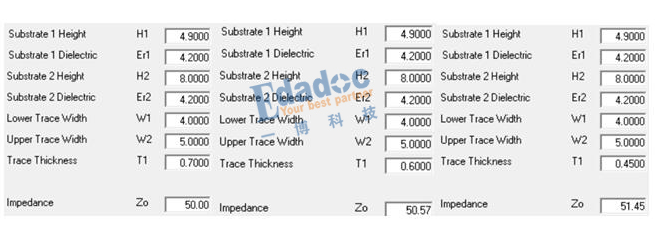

先看看阻抗:影響小于±1歐姆,不算太大的影響,并且這個影響是在整體阻抗10%的偏差里面的,設計中我們可以忽略不計。

再看看載流的影響:我們找了一個實際項目,0.5oz銅分別按標準值(0.6mil)與加工最小值(0.45mil)設置的仿真結果對比

0.5oz銅厚設置為0.6mil時:

用電端電壓:839mV

VRM端輸出電壓:890mV

回路直流電阻:8.98mΩ

0.5oz銅厚設置為0.45mil時:

用電端電壓:838mV,看起來壓降變化不大

看起來壓降和VRM端輸出電壓變化不算太大,但是直流電阻差值隨銅厚變化1.78mΩ,所以壓降的變化是引入遠端反饋的結果,直流電阻抬升明顯,還是有一定隱患。

同時看到電流密度的變化,影響會更大:

0.5oz銅厚設置為0.6mil時的電流密度,最大在120A/mm2左右

0.5oz銅厚設置為0.45mil時的電流密度,最大在160A/mm2左右

直流電阻抬升,電流密度變大,加工誤差的影響不可忽略。回顧我們上一個話題開始的故事,可能PCB板廠的加工都在行業規范允許的誤差范圍,但是最終導致影響到產品性能,這本質上是設計裕量的問題。凡是生產,必有偏差,PCB設計裕量要預留出生產允許的偏差。

編輯:hfy

-

阻抗

+關注

關注

17文章

957瀏覽量

45915 -

多層板

+關注

關注

2文章

151瀏覽量

27883 -

PCB設計

+關注

關注

394文章

4683瀏覽量

85548 -

IPC

+關注

關注

3文章

346瀏覽量

51902

發布評論請先 登錄

相關推薦

厚銅PCB設計這個問題一定要注意

內層銅厚偏差對性能的影響

內層銅厚偏差對性能的影響

評論