最近小編去外面的世界走了一圈,和大家進行了多場面對面的技術交流會。粉絲們很熱情,水平也很高,雖然時間匆忙,但是也獲益良多;回來后決定重拾“荒廢”一段時間的學業,結合不少朋友的問題和最近高速先生的文章主題繼續講講PCB設計與加工誤差的這些事。

如果讓你疊一個8層板,最常規的會疊成下圖左邊這樣:有兩個內層走線,其中有一個走線層上下都參考地,屬于比較好的走線層,另外一個需要有一面參考電源,很多人總是會覺得差一丟丟的感覺(問他們差在哪,他們又不一定說得出來,關于參考電源的差異,這里不展開討論)。那如果發現2個內層不夠,需要3個內層走線的話,你可能只能像下圖右邊這么疊,在同樣層數的情況下,多一個內層就只能少一個地層,那就會出現兩個平面層夾2個信號層,這就是我們所說的雙帶線結構,下圖右邊紅色框框所示。

在我們日常的PCB設計中,對于雙帶線,我們除了要關心同層走線之間的串擾之外,還要關心相鄰層走線的串擾。

下面是兩對線寬為4.5mil,線間距為9mil的差分線,它們和參考平面共同組成了一組雙帶線的結構(下面紅色和綠色的差分線,黃色是參考平面)。

一些基礎的串擾理論告訴我們,如果雙帶線平行走線長度過長的話,串擾會比較嚴重,我們用這個雙帶線的模型做一下仿真,看看到底串擾能嚴重到什么程度哈。我們定義差分線到各自參考平面的距離為H,相鄰層的距離為2H,平行走線長度為1000mil。

在上圖的這種情況下,兩對差分線的串擾(由于是內層走線,我們更關心近端串擾,下面的分析也都是指近端串擾)是這樣的:我們可以看到,串擾是比較嚴重的,接近15dB了。

如果在垂直方向的距離2H固定的情況下,我們可以通過拉開它們的水平距離達到減小串擾的目的,例如可以拉開到下面的這兩種情況。

從仿真結果上看,拉開到相切到一倍線寬的距離時對串擾就會有明顯的改善效果,串擾可以從-15dB到非常好的-50dB。

但是拉開到一倍線寬線距對布線來說會很浪費空間,降低布線的密度。另外大家有沒有有想過,按從下圖左邊完全重合到右邊相切逐漸拉開的話,串擾會是怎樣的一個變化過程呢?是不是從左到右越錯開串擾越小呢?

實際上很多事情真的不能靠感覺來判斷哈,我們通過仿真,串擾結果是這樣的:

除了上面說的重合和相切的串擾外,如果細致分析下面三種情況,分別往右邊拉開水平距離時,它們的串擾結果是這樣的:

大家覺得上圖的串擾結果從高到低分別是上圖的從左到右,是不是越往右邊拉開,串擾越小呢?

但是事情的真相是這樣的:當走線移到接近互相錯開的時候,這時的串擾是極小的,甚至接近拉開一倍線寬線距的設計。

至于原理,簡單來說是這樣:當攻擊差分線和受害差分線互相錯開到一定距離的時候,兩根單端的攻擊線對每根單端的受害線的串擾都有最大程度的抵消,因此總會在一個錯開的位置有串擾的最低值,再向左向右的過程,抵消的比例都會逐漸減小,因此串擾又會大起來了,當然到拉開出相切以上的距離,就肯定是越來越小了。

上圖幾個情況的串擾值如下所示:

單從理想的設計層面,如果把兩對差分線互相錯開,大概錯開到中間的位置,串擾的效果就會非常的好,然后也會很節省布線的空間,看起來真是一個很不錯的設計。

編輯:hfy

-

PCB設計

+關注

關注

394文章

4683瀏覽量

85555

發布評論請先 登錄

相關推薦

[討論]PCB設計面臨的新挑戰

PCB設計后期處理概述

(免費資料+福利)多層高速pcb設計中那些不得不說的事

(免費資料分享)多層高速pcb設計中那些不得不說的事(包含DDR、眼圖、剛柔板、傳輸線等等內容)

【系列直播免費分享】多層高速pcb設計中那些不得不說的事

(免費資料+福利)多層高速pcb設計中那些不得不說的事(DDR、眼圖、剛柔板,傳輸線等等內容)

[(8小時+免費課程分享)多層高速pcb設計中那些不得不說的事(包含DDR、眼圖、剛柔板、傳輸線等等內容)

(免費分享)多層高速pcb設計中那些不得不說的事(包含DDR、眼圖、剛柔板、傳輸線等等內容)

談談PCB設計電子與機械之間的那些事

PCB設計有哪些誤區PCB設計的十大誤區上部分內有下部分鏈接

SMT貼片加工對PCB設計的要求

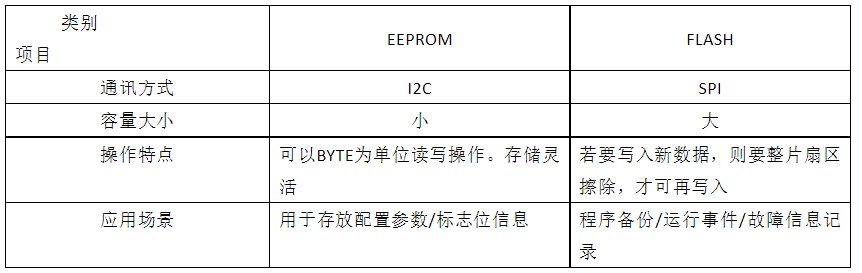

說說EEPROM和FLASH的那些事

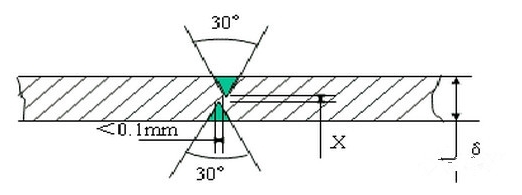

談談PCB設計與加工誤差的那些事

談談PCB設計與加工誤差的那些事

評論