了找出誤碼的根本原因,抖動分析是最好的起點,但是在某些情況下,電源軌分析可以幫助找出真正的根本原因。為了深入了解比特錯誤,我們在時域和頻域都研究了抖動和電源軌噪聲。比較TIE頻譜中的PJ(周期性抖動)頻率和電源紋波頻譜中的雜散,是識別由PDN(配電網絡)引起的信號完整性問題的快速而準確的方法。

SI和PI助長錯誤

數字錯誤是由抖動和噪聲引起的。噪聲是信號幅度變化的廣義術語。抖動是相對于數據速率時鐘的比特轉換時序變化,即所謂的時間間隔誤差。抖動是由相位噪聲和幅度噪聲到抖動的轉換引起的。抖動噪聲帶來了串擾,EMI(電磁干擾)和隨機噪聲的問題。

信號完整性分析著眼于BER(誤碼率),著眼于發送器,參考時鐘,通道和接收器的性能。電源完整性著眼于PDN提供恒定電壓電源軌和低阻抗返回路徑的能力。SI和PI具有廣泛的相互依賴性。PDN會引起噪聲和抖動。電路設計和組件(芯片封裝,引腳,走線,過孔,連接器)會影響PDN的阻抗,進而影響供電質量。

從眼圖開始調試SI問題

硬件調試可以從眼圖分析開始。眼圖由相對于時鐘的重疊波形組成,圖1。

圖1:眼圖,帶遮罩測試,頂部,對應的波形,底部。

交叉點的水平寬度表示抖動,眼睛的頂部和底部的垂直寬度表示噪聲。睜大眼睛應該對應于低BER。如果BER太高,下一步就是執行抖動分析。圖2將抖動的分解圖映射到其組件和子組件,圖3顯示了“抖動摘要”測量值,包括浴盆圖,眼圖,TIE頻譜和直方圖,抖動測量結果和波形。

圖2:抖動分解為其各個組成部分。

圖3:抖動摘要屏幕快照,從左上方順時針方向:浴缸圖,眼圖,TIE頻譜,抖動分析結果,波形,TIE直方圖。

抖動的分解開始于將TIE分布分為其隨機和確定性分量RJ(隨機抖動)和DJ(確定性抖動)。DJ進一步分為與數據中的比特序列相關的抖動-DDJ(與數據有關的抖動)和與PJ(周期性抖動)等不相關的抖動。

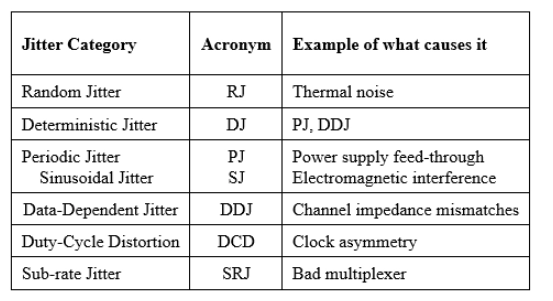

眼圖上的廣泛交叉可以指示RJ。看起來由許多幾乎不同的線組成的眼睛可能表示DDJ,可能是由于信號路徑中的阻抗不匹配所致。需要更詳細的測量來確定可以指示硬件錯誤的抖動類型:TIE,RJ,DJ,DDJ,PJ,TJ(總抖動),EH(眼高),EW(眼寬),眼高和眼低的。表1列出了不同類型的抖動和一些原因。電源軌紋波是PJ有時甚至是RJ的常見原因。

表1:抖動測量以及常見原因示例。

表1:抖動測量以及常見原因示例。

抖動和配電網絡

PDN的工作是維持恒定電壓并為系統中的組件提供足夠的電流。它會影響主動或被動每個元素的性能。PDN包括整個系統,不僅包括DC-DC轉換器和內部芯片電源分配,還包括每個互連,走線,過孔,連接器,電容器,封裝,引腳和球柵。

紋波對隨機和周期性抖動的影響

電源軌噪聲通常稱為紋波,通常為幾毫伏。要在GHz頻率上準確測量電源軌上的mV噪聲,就需要具有高DC阻抗的高帶寬探頭,該探頭在高頻下充當50Ω傳輸線。為此專門設計了電源導軌探頭。

開關電源通過在低功耗??導通和關斷狀態之間連續切換來調節電源軌和返回路徑(又稱“接地”)之間的電壓。不幸的是,驅動開關元件的脈沖會引起“開關噪聲”并引起PJ。

開關以固定頻率發生,應將其記錄在DC-DC轉換器的數據手冊中。如果圖4左上方的紋波頻譜和緊靠其下方的TIE頻譜在開關頻率或開關頻率的諧波處都有雜散,那么我們就知道了源頭并可以解決設計問題。請注意,圖4中紅色標記處出現大的重合雜散。TIE頻譜右邊的TIE直方圖在一個頻率上具有正弦抖動分布(馬蹄形)PJ。

圖4:頻譜視圖左上方的電源軌紋波,以及其下方的TIE頻譜,以及信號和電源軌波形以及TIE直方圖。

電源會引入隨機噪聲,從而導致RJ。電源軌隨機噪聲顯示為圖4左上方“頻譜視圖”圖的本底噪聲。RJ由TIE頻譜的本底噪聲計算得出。在此示例中,由于電源紋波引起的隨機噪聲非常低,RJ很小,約為0.84 ps。

PJ和地面彈跳

在邏輯轉換期間,發送器和接收器從PDN獲取或吸收電流。當多個信號同時在兩個電平之間切換時,它們可以從電源導軌和/或接地板上沉積或去除大量電荷。短期引入電荷密度會改變導體兩端共同接地的電壓。所產生的電壓變化稱為接地反彈或等效的同時開關噪聲(SSN)。

在繼續之前,我們應該澄清兩件事。首先,“接地”是指返回路徑的所需公共參考電壓,通常將其定義為0V。第二,“同時”是指組件在其上升/下降時間間隔內產生或吸收電荷。下降時間重疊。

SSN在時域中看起來是隨機的,但在頻域中卻不是。數據信號由許多頻率分量組成-基頻或奈奎斯特頻率,也許多達兩個高次諧波,再加上連續相同位的次諧波。這些頻率中的任何一個都可能發生同時切換。因此,SSN是具有許多低振幅雜散的周期性噪聲,會引起PJ。

為了確認PJ是由SSN引起的,請將圖5左上方的電源軌頻譜與正下方的TIE頻譜進行比較。在兩個頻譜中以相同頻率出現的高振幅雜散表明SSN的PJ貢獻很大。

圖5:(a)電源軌紋波頻譜和(b)TIE /抖動頻譜。

概括

信號完整性和電源完整性是一個反饋回路。網絡中的每個元素,每條走線,過孔,連接器,引腳,封裝等都會影響PDN阻抗和每個通道的阻抗,并且每個有源組件都會改變電源軌和接地層的電壓。

眼圖可以告訴我們很多有關信號完整性的信息,但很少幫助我們識別特定問題。對TIE分布的分析將抖動分解為一些組件,這些組件提供了問題所在的線索。高RJ通常意味著時鐘嘈雜,但也可能指示電源產生隨機噪聲。

PJ可能指示時鐘故障,電源開關噪聲或接地反彈/ SSN。將電源軌紋波頻譜與TIE頻譜進行比較可以分兩步解決問題。TIE頻譜中的雜散表示電源軌頻譜中沒有任何相應的雜散,表示時鐘。兩個頻譜中相同頻率的一個或兩個雜散表示電源開關噪聲;兩個光譜共有的大量雜散表示SSN。在每種情況下,將抖動和功率分析結合起來可以解決其他困難的問題。

信號完整性和電源完整性通常被認為是不同的學科,但是我們已經發現,發現與高抖動相關的問題需要對兩者都進行理解。

編輯:hfy

-

信號完整性

+關注

關注

68文章

1408瀏覽量

95464 -

PDN

+關注

關注

0文章

83瀏覽量

22706

發布評論請先 登錄

相關推薦

數字產品中電源軌噪聲如何影響系統中時鐘抖動

電源軌的封裝電感過大怎么辦

電源軌是什么,電源軌不同列之間導通嗎

OPA2188單電源時最大輸出3.7V,不能軌至軌輸出怎么解決?

OPA4350-DIE高速、單電源、軌到軌運算放大器數據表

OPA2834 50MHz、負電源軌輸入、軌至軌輸出、電壓反饋放大器數據表

如何通過電源軌分析理解電源軌噪聲與抖動

如何通過電源軌分析理解電源軌噪聲與抖動

評論