1 短波動態(tài)頻譜接入系統(tǒng)硬件設(shè)計(jì)

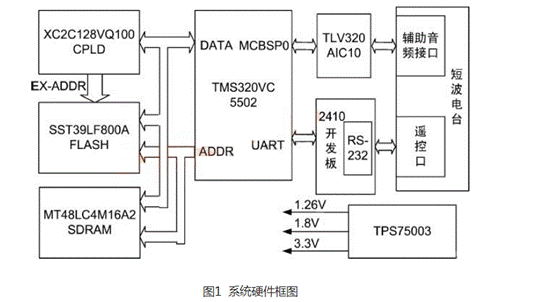

短波動態(tài)頻譜接入系統(tǒng)的硬件組成部分主要包括:TMS320VC5502 數(shù)字信號處理器、音頻信號處理模塊以及外部存儲器等部分。

TMS320VC5502 是信號處理部分的核心,主要負(fù)責(zé)對音頻信號處理模塊送來的數(shù)據(jù)進(jìn)行頻譜分析;TLV320AIC10 音頻處理模塊主要完成對輸入模擬信號的濾波和A/ D 轉(zhuǎn)換工作; SST39LF800A 作為程序存儲器,存放DSP 的引導(dǎo)程序; SDRAM 作為外部存儲空間的擴(kuò)展,存放處理的數(shù)據(jù); DSP 與各外設(shè)的聯(lián)絡(luò)由XC2C128VQ100 來完成; 2410 開發(fā)板承載整個應(yīng)用程序,同時通過RS 232 串口實(shí)現(xiàn)對短波電臺的自動化操作和控制,并通過反饋信息獲取電臺的工作狀態(tài),圖1 為系統(tǒng)的硬件框圖。

系統(tǒng)工作過程如下: 系統(tǒng)加電TMS320VC5502復(fù)位后,由其內(nèi)部固化的引導(dǎo)程序( BOOT) 將存于FLASH 的程序和數(shù)據(jù)搬移至內(nèi)部RAM。由電臺音頻口送來的音頻信號經(jīng)TLV320AIC10 采樣后,送到高速處理器TMS320VC5502 進(jìn)行基帶信號的FFT 運(yùn)算。DSP 每運(yùn)行一次算法,將結(jié)果送至RAM,在信道掃描一周后,RAM 將結(jié)果送到DSP,將各個信道的噪聲功率值排序,并將結(jié)果通過RS232 口送給SBC 2410 開發(fā)板,SBC 2410 開發(fā)板收到后,根據(jù)預(yù)先設(shè)置好的噪聲門限為每個信道劃分等級,并將其存儲在數(shù)據(jù)庫中。

2 短波動態(tài)頻譜接入系統(tǒng)軟件設(shè)計(jì)

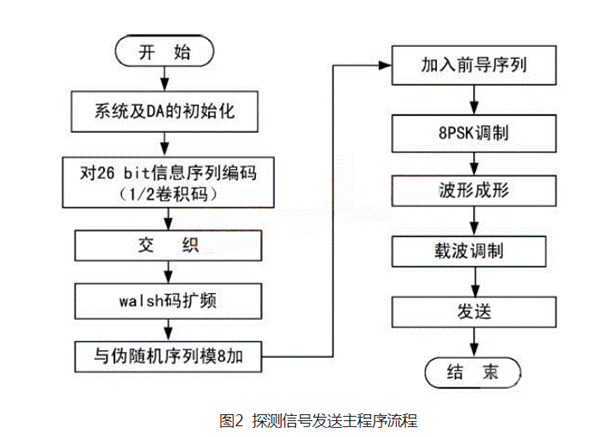

2. 1 探測信號發(fā)送主程序設(shè)計(jì)

探測信號發(fā)送主程序流程如圖2 所示。

有效載荷經(jīng)過卷積編碼、交織和正交符號映射后,形成長度為13 1*= 832 的3 bit 數(shù)據(jù)符號序列,然后與保護(hù)序列、探測報(bào)頭和數(shù)據(jù)符號序列組成信道符號序列,以2 400 符號/ s 的速率對1 800 Hz的載波進(jìn)行8PSK 調(diào)制,產(chǎn)生發(fā)送波形。

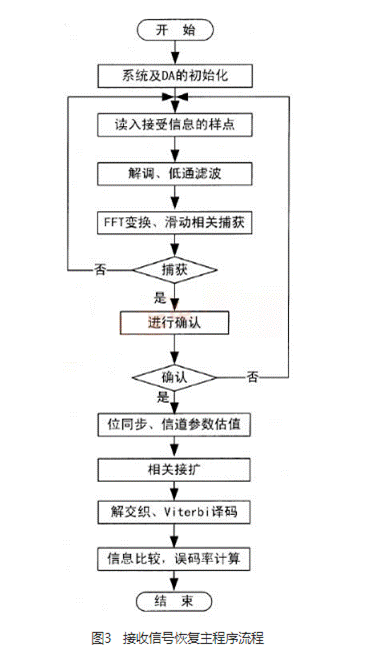

2. 2 接收信號恢復(fù)主程序設(shè)計(jì)

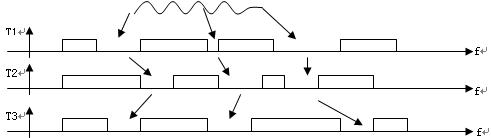

在沒有通信任務(wù)的狀態(tài)下,系統(tǒng)持續(xù)地監(jiān)測信道上有沒有高過門限的有效信號序列。如果發(fā)現(xiàn)信號,系統(tǒng)開始對信號進(jìn)行捕獲。當(dāng)?shù)? 次出現(xiàn)峰值大于門限時,記錄此時的頻差估計(jì)值,然后作3 次確認(rèn)。若3 次確認(rèn)中的峰值大于門限的少于2 次,或者頻差估計(jì)值之間的差值超出允許的范圍,則認(rèn)為捕獲無效,系統(tǒng)重新開始搜索; 若確認(rèn)過程中大于門限的峰值次數(shù)和頻差估計(jì)值之間的差值在允許范圍內(nèi),則進(jìn)行位同步和信道估計(jì)。在位同步過程中,通過與本地序列的滑動相關(guān)來實(shí)現(xiàn)位同步和信道估計(jì),并對多次估計(jì)值的結(jié)果進(jìn)行適當(dāng)處理,獲得最終的位同步和信道參數(shù)估值結(jié)果。根據(jù)位同步結(jié)果,通過采用分集接收、相關(guān)解擴(kuò)、解交織和解碼獲得原始信息,完成一次接收。根據(jù)前導(dǎo)序列的對比可獲得信道誤碼率,其軟件設(shè)計(jì)流程如圖3 所示。

3 短波動態(tài)頻譜接入系統(tǒng)性能測試

為了對所設(shè)計(jì)系統(tǒng)的整體性能進(jìn)行*估,先后在重慶? 遵義、重慶? 常州、重慶? 廣州、北京? 常州等不同距離的通信線路上進(jìn)行了3 個多月、共約1 200 余次的通信實(shí)驗(yàn)。

實(shí)驗(yàn)中主要對設(shè)計(jì)系統(tǒng)的鏈路建立和基本數(shù)傳性能進(jìn)行了測試和*估。以鏈路建立和數(shù)據(jù)報(bào)文通信為主,每份報(bào)文以200 組為標(biāo)準(zhǔn),每4 個字符為一組,共800 個字符進(jìn)行實(shí)驗(yàn)。每隔30 min 發(fā)起一次呼叫,發(fā)起呼叫時的起始狀態(tài)為同步掃描狀態(tài),待鏈路建立后并分別以600 baud 和1 200 baud 的數(shù)據(jù)傳輸速率發(fā)送報(bào)文。通過記錄鏈路建立情況、呼損率和數(shù)據(jù)報(bào)文的接收情況來測試系統(tǒng)的基本性能。通過對實(shí)驗(yàn)數(shù)據(jù)的比較分析表明,系統(tǒng)由于采用了短波頻譜感知技術(shù)、動態(tài)頻率優(yōu)選等技術(shù),建鏈概率和建鏈時間分別比二代短波電臺提高了約26% 和31% 。

在數(shù)據(jù)報(bào)文的通信過程中,由于系統(tǒng)采用了短波頻譜感知技術(shù),通信前,系統(tǒng)根據(jù)頻譜感知結(jié)果優(yōu)選出了可靠空閑頻譜,保證了系統(tǒng)始終建鏈在可靠信道上。在數(shù)據(jù)傳輸速率為600 baud 和1 200 baud的前提條件下,報(bào)文的正確接收概率比普通的短波電臺提高了10%~ 12%,而且平均錯誤字符的概率也比普通電臺降低了一個數(shù)量級,達(dá)到了10- 4,能夠充分滿足短波普通通信業(yè)務(wù)的需求。

4 結(jié)束語

綜上所述,基于短波動態(tài)頻譜接入的頻譜感知技術(shù)改善了現(xiàn)有的二代短波通信系統(tǒng)的鏈路建立及業(yè)務(wù)傳輸性能,提高了短波數(shù)據(jù)通信的可靠性和有效性,對于提升通信裝備的戰(zhàn)術(shù)技術(shù)性能具有十分重要的意義。

編輯:hfy

-

頻譜

+關(guān)注

關(guān)注

7文章

893瀏覽量

46298 -

數(shù)字信號處理器

+關(guān)注

關(guān)注

5文章

478瀏覽量

27729 -

音頻信號處理器

+關(guān)注

關(guān)注

0文章

2瀏覽量

1465

發(fā)布評論請先 登錄

感知時間等比縮減的機(jī)會頻譜接入算法研究

面向頻譜感知的傳感器網(wǎng)絡(luò)設(shè)計(jì)

頻譜感知技術(shù)研究發(fā)展到了哪一步?未來的發(fā)展方向是什么?

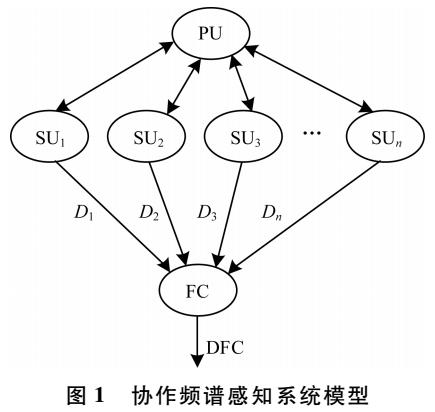

基于數(shù)據(jù)融合的加權(quán)合作頻譜感知技術(shù)

基于認(rèn)知無線電的高效頻譜利用技術(shù)

認(rèn)知無線電頻譜感知與分配技術(shù)

Femtocell系統(tǒng)中認(rèn)知無線電頻譜感知技術(shù)

動態(tài)頻譜分配與頻譜共享研究綜述

基于隨機(jī)矩陣?yán)碚摰?b class='flag-5'>頻譜感知技術(shù)研究綜述

基于智能跳頻的短波無線接入網(wǎng)動態(tài)頻譜分配算法

基于用戶服務(wù)質(zhì)量的動態(tài)頻譜接入網(wǎng)絡(luò)

一種選擇觸發(fā)協(xié)作頻譜感知算法

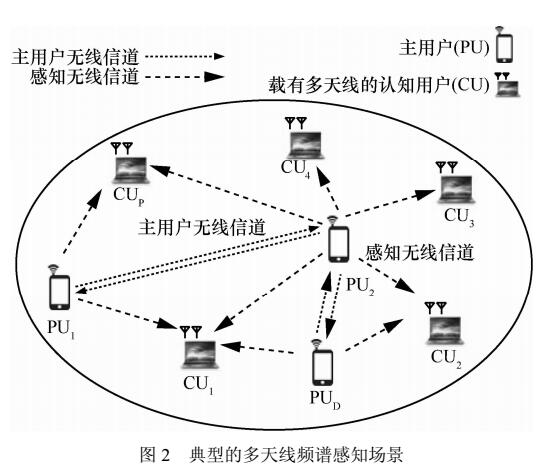

多天線盲頻譜感知算法

面向泛在頻譜信息實(shí)時更新與安全傳輸?shù)?b class='flag-5'>動態(tài)頻譜分配方法

評論