對于模擬電路沒學好的工程師來說,電阻只知道用來端接;電感只知道用來隔離;至于電容嘛,估計你們只知道濾波,更不用說它們的組合產生的作用了。不信?估計以下這個電容的用法,你也只能說濾波了吧……

上周我們雷工,哦不是,是我們姜工的文章向大家介紹了DDR的時鐘里面并聯電容的用處,讓大家驚奇的發現了原來電容也可以用來端接,可能已經讓一大把粉絲獲得了一波知識的源泉。那么本期高速先生還繼續玩這個DDR的時鐘,去深挖它還有什么槽點。

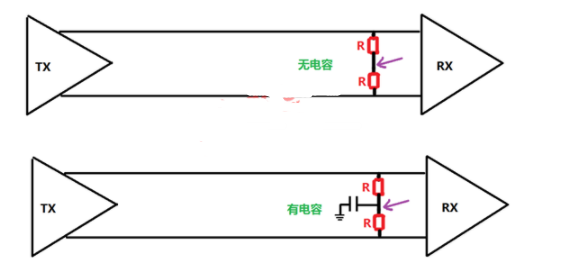

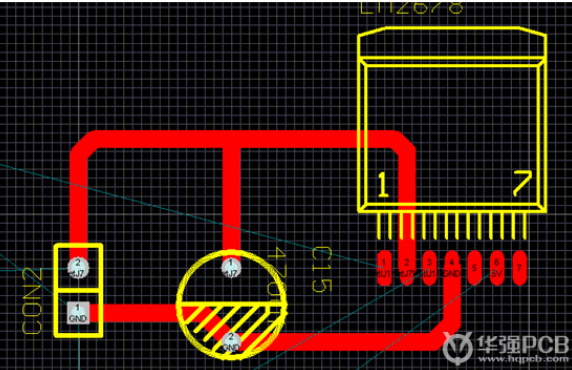

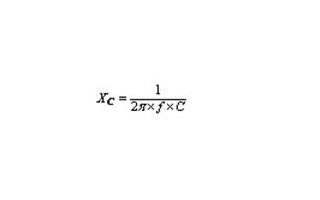

我們先把上周所講到的這個DDR時鐘的拓撲再一次拉出來,沒錯!就是下面這個圖啦。其中上周讓雷工尷尬不已的這個電容就是下面紅色圈圈的那位了。把電容并聯到差分對間,能夠很好的對發送的信號進行端接,目標是使得電容的電抗值和傳輸線接近,從而起到源端端接的效果,減小時鐘的反射。

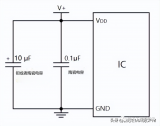

恩,這個是上篇文章的精華哈。那么我們這期的文章繼續研究這個拓撲,大家有沒有發現上面的拓撲其實不止一個電容,看看上圖藍色圈圈的位置,其實還有一個電容哦!它一般是放在最后兩個端接電阻之間,然后下拉到地(也可以上拉到DDR電源)。這個電容到底有什么用呢?根據高速先生對你們的認識,都接到地了,肯定又是用來濾波啦?

高速先生對此也研究了一番,我們用一個簡單的點對點的時鐘拓撲進行驗證哈。

如果這對差分線是理想的走線,所謂理想就是差分線的P和N長度一致,阻抗相同,分成對稱的情況下。有無電容的結果是下面這樣的。

是的,如果我們的PCB加工出來就像原理圖設計一樣是理想的情況,那這個電容的確起不了什么作用。但是我們PCB最精彩的地方就在于它的設計和加工的誤差哈。我們知道,對于一對差分線來說,對間P和N的對稱性是最為重要的事情,不然的話它們就是產生共模的噪聲。基本上來說,只要破壞了差分線理想狀態,這對差分線都會或多或少產生共模的噪聲。那么我們在有共模噪聲的情況下再去進行對比驗證,結果就會變得不一樣了。

可以看到,沒有了這個電容之后,接收端的波形變得扭曲,甚至是產生了非單調的結果。那么大家也許會問了,那你們怎么知道是不是共模噪聲的影響呢?怎么看呢?

我們可以看下圖紫色箭頭位置的波形,也就是它們產生的共模噪聲的位置了。

我們可以看到,當差分線有共模噪聲的時候,這個電容其實可以為我們抑制很大部分的噪聲,因此能最大限度的還原接收端信號的完整性。

當然如果旁邊的走線離這對時鐘很近的話,有了這個電容,自然也能使得共模噪聲串擾到旁邊走線的能量削弱啦,也就是起到減小串擾的效果。

編輯:hfy

-

模擬電路

+關注

關注

125文章

1556瀏覽量

102719 -

電容

+關注

關注

100文章

6036瀏覽量

150267 -

濾波

+關注

關注

10文章

667瀏覽量

56633 -

串擾

+關注

關注

4文章

189瀏覽量

26943 -

走線

+關注

關注

3文章

113瀏覽量

23902

發布評論請先 登錄

相關推薦

PCB設計應用:電容的作用

PCB設計應用:電容的作用

評論