做DDR的調試無非以下三種結果:調試fail、調試pass和調試很久才pass。你可能永遠也想象不到PCB工程師花幾天設計出來的DDR模塊在加工出來后調試就多久才pass,一天?一周?一個月?甚至……

高速先生近幾年來在DDR設計仿真取得了長足的進步,這要得益于AI(人工智能)的熱潮,作為該領域的核心產品,AI算力卡成為近年來各大通訊公司和芯片公司爭相研發的產品。而其中DDR模塊則是AI算力卡里最核心的模塊,支撐著算力卡大容量、快速的運算能力。

高速先生在和各大公司合作的情況下,也有機會接觸到了形形色色的AI算力卡,它里面的DDR模塊雖然實現的功能類似,但是具體的結構卻有著很多的變化。例如容量的不一樣導致顆粒數量的不同;板子的大小不一樣導致采用的拓撲不同;PCB層數的不一樣導致DDR模塊的布局和密度也不相同;有的由于功耗電流大小不一樣導致DDR走線參考層也不相同,有的需要參考電源層,有的需要相鄰層走線;當然還有的就是需要跑到的目標速率不同,我們在設計上的設計裕量也會有所差異等等。因此對于我們高速先生來說,每一塊算力卡的DDR設計都是不同的,當然設計加工出來之后,我們和客戶配合著去調試的難度也是不一樣的。這一塊高速先生在近幾年的研討會上也和大家分享過一些經典的案例,讓大家對DDR的設計和調試難度都有了新的認識,AI產品的一些特點關于它的設計使得比以往任何產品的DDR難度都要大一點,當然我們也就會有很多測試和仿真的案例了。這里關于DDR調試的案例,我們再給大家分享一個從fail到pass的經歷哈。

在一個安靜祥和的午后,高速先生剛剛還略帶點午睡的困意開始下午的工作,就突然收到了客戶一份很“提神”的郵件,讓大家立馬精神了起來。

原來是客戶在我們公司設計加工的一款主力的AI算力卡出現了調試fail的問題,客戶本身是一家很有研發能力而且很嚴謹的公司,它們對硬件原理和調試都是具有豐富的經驗,然而這款產品的DDR模塊他們調試了幾周都依然沒辦法成功。由于是我司PCB工程師設計的板子,因此高速先生肯定是臨危受命,去負責介入到他們的調試中去。

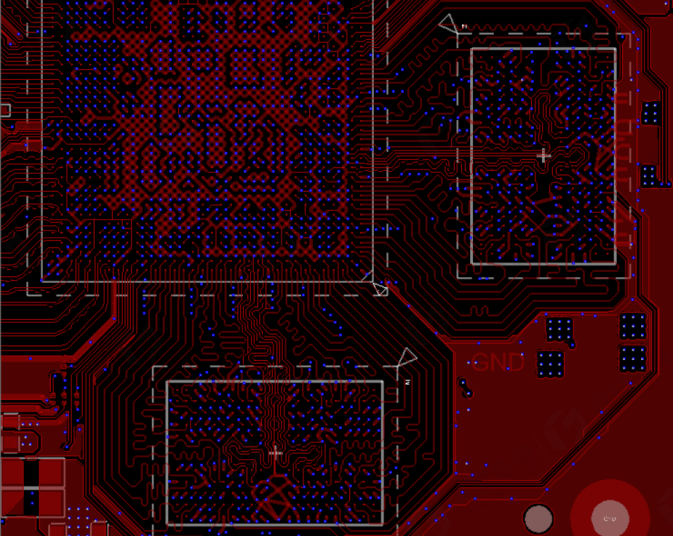

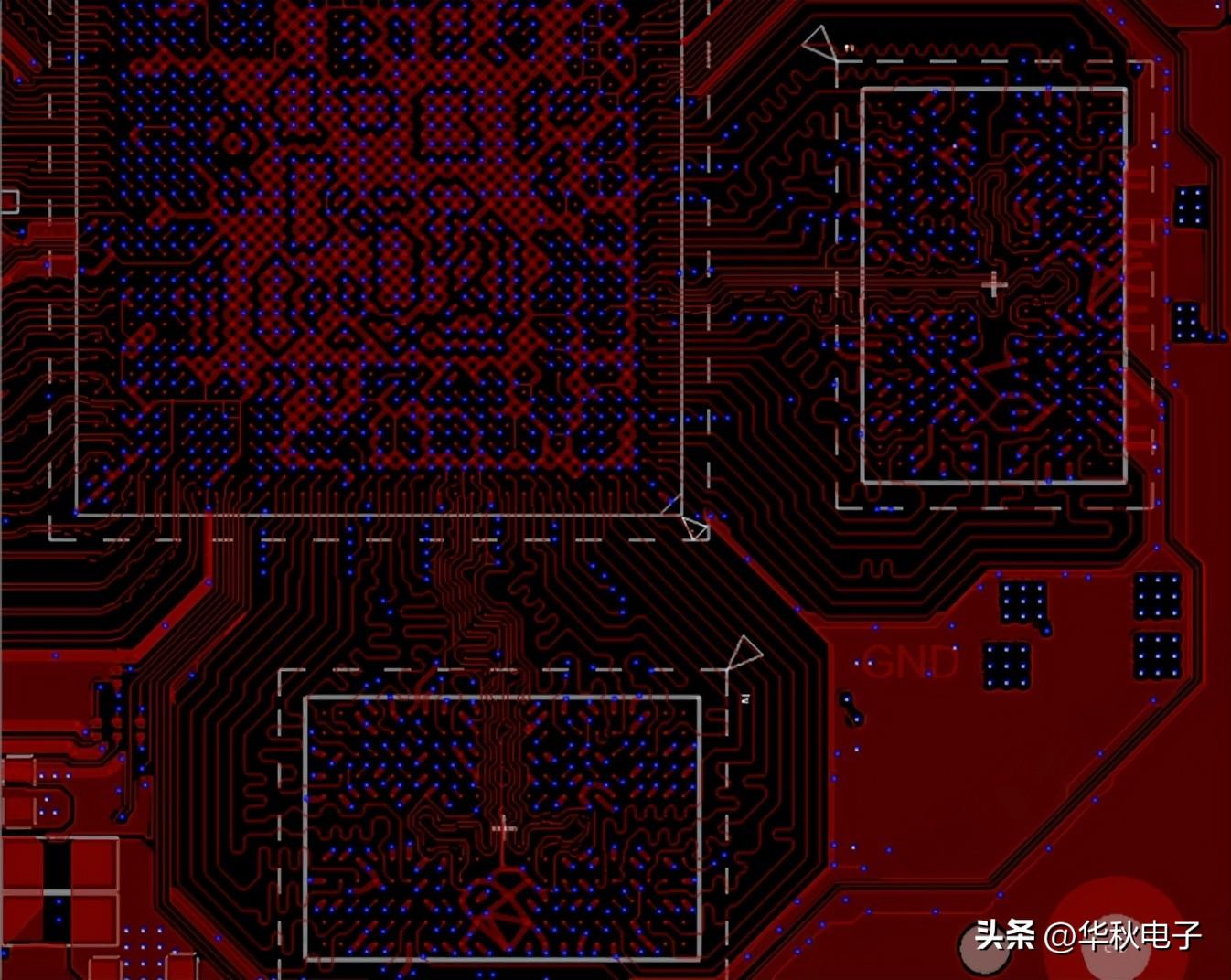

高速先生打開PCB文件,看到了FPGA和C1這個DDR通道的連接,這個通道是由9個DDR顆粒組成,也就是我們所說的1拖9的DDR拓撲。由于板子的密度很大,因此只能采取正反貼的形式進行布局布線,如下圖所示。

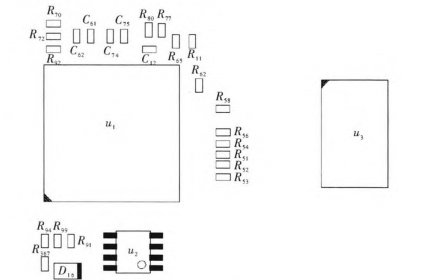

由于FPGA芯片是有關于DDR的設計指導文檔,我司的PCB工程師和客戶在投板前也反復確認了該DDR模塊的設計是完全按照文檔上面每一條細致的指導去布線的。例如下圖的L0,L1,L2等每段長度文檔上都是有要求。

客戶就是因為覺得都按照了上面的設計指導進行布局布線,認為設計其實是達到了要求,因此才堅持著花費了近一個月的時間進行調試,希望能從調試中去解決問題。高速先生介入后,發現客戶的調試其實已經做了很多內容,包括驅動內阻的變化,ODT電阻的變化,電源電壓的微調,VTT電阻的改變,飛線等等,但是仍然無法達到額定的2400Mbps的速率。由于這個項目當時是沒有進行過我們高速先生仿真的,因此我們首先建議做一個debug形式的仿真,也就是在基于調試結果的仿真,看看仿真的測試的擬合度到底高不高,從中找出問題。

由于我們對xilinx的FPGA仿真模型和DDR顆粒的仿真模型都比較有信心,之前也做過很多仿真測試的對比,發現仿真和測試波形的擬合度是比較高的,再加上高速先生看到這個拓撲還是非常的復雜,因此有信心在客戶調試的配置參數下得出一個“差”的仿真結果!你沒聽錯,我們這種debug的仿真就是希望得到一個差的仿真結果,這樣才能和實際上調試fail的情況吻合上。

果然,高速先生希望的事情發生了,我們對地址控制信號進行仿真的時候,發現了距離FPGA最近的DDR顆粒的信號質量是不滿足要求的,為什么要看距離主芯片最近的顆粒,這個高速先生已經說過很多次了哈,這里就不再重復了。

同樣,根據客戶調試的情況,我們在仿真中選擇不同的驅動內阻和VTT電阻的阻值,的確也和調試的情況類似,都不能得到一個很好的信號質量。到這里,我們開了一個好頭,至少能在仿真中得到了和測試結果相對應的結論。

但是高速先生在仿真中還能做些什么呢?我們雖然通過仿真找到了差的波形,但是這對于調試卻起不了太多指導的作用。因此我們繼續去通過仿真模型來看看,到底會不會還有什么驅動的配置我們可以嘗試過。我們打開FPGA的ibs模型,看到可選擇的以下驅動配置中,其實我們和客戶只用到了左邊的這種配置,上面有40到60歐姆內阻的選擇,我們仿真和客戶調試都試過了,沒有明顯的改善。

但是我們驚訝的發現,原來模型上還有綠色的兩列基本和之前紅色列的配置幾乎一樣的驅動內阻可以選擇,但是唯一不同的是F,M和S的區別,因此高速先生再花點時間去掃描一下同樣是40歐姆驅動內阻的情況下,F,M和S下面這三種buffer到底會不會有差異呢?

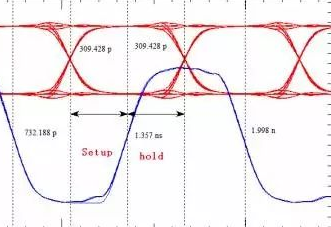

結果讓高速先生感到驚訝的同時又感到興奮,原來在FAST,MEDIUM和SLOW模式下,對于同一個驅動內阻的波形是有著明顯的差異。我們看到MEDIUM和SLOW模式下,信號的上升沿slew會變緩,這樣反而避免了部分的反射,使得信號的ringback減小,眼高的裕量變高。

根據上面的掃描結果,我們選用MEDIUM的模式進行全通道的仿真,看看和之前fast模式的結果相比到底有沒有改善。

結果給高速先生帶來了喜悅,我們用MEDIUM模式去仿真的結果能夠得到明顯的改善,同樣的顆粒信號質量變得可以接受了。

高速先生從FPGA模型的選擇上解決了問題,選取上升沿slew比較緩的驅動反而能夠獲得比較好的信號質量。

到這里,我們就只剩下最后一個問題了,那就是到底我們能不能讓客戶在調試的參數配置中選擇MEDIUM的模式呢?客戶把他們調試的軟件界面發過來給我們,我們從下拉菜單中看到了的確有這種模式可以選擇,然后就讓客戶從默認的FAST模式自動換成MEDIUM的模式,看看效果有什么改善。

在大概等待了一天之后,客戶的一封報喜的郵件讓我們大家都輕松了下來,客戶調試了一個月之后,終于通過這個手動調試的buffer切換快速解決了問題。

編輯:hfy

-

FPGA

+關注

關注

1629文章

21729瀏覽量

603012 -

DDR

+關注

關注

11文章

712瀏覽量

65318 -

AI

+關注

關注

87文章

30728瀏覽量

268892

發布評論請先 登錄

相關推薦

PCB設計經驗分享

DDR電路PCB布局布線技巧

DDR電路的PCB布局布線要求

【PCB設計干貨】DDR電路的PCB布局布線要求

汽車音響導航系統中DDR高速信號的PCB設計

如何進行DDR2高速PCB設計和信號完整性分析的詳細資料分析

DDR布線在PCB設計中的應用解析

【華秋干貨鋪】DDR電路的PCB布局布線要求

DDR電路的PCB布局布線要求

PCB設計:DDR的調試案例

PCB設計:DDR的調試案例

評論